Πολγτεχνείο Κρητής Σχολή Ηλεκτρολογών Μηχανικών Και Μηχανικών Υπολογιστών

Παράλληλη Αρχιτεκτονική για Υλοποίηση του

# Αλγόριθμου Scalejoin στον Υπερυπολογιστή

## Convey

Διπλωματική Εργάσια

Καρανδεινός Χ. Έκτωρ

## Εξεταστική Επιτροπή:

Καθ. Δόλλας Απόστολος(Επιβλέπων) Αναπλ. Καθ. Ιωάννης Παπαευσταθίου Καθ. Γαροφαλάχης Μίνως

Χανιά, Ιούνιος 2017

TECHNICAL UNIVERSITY OF CRETE DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

# Parallel Architecture for the Scalejoin Algorithm

# Implementation on the Convey Supercomputer

DIPLOMA THESIS

Karandinos C. Ektor

Thesis Committee: Prof. Dollas Apostolos(Supervisor) Assoc. Prof. Ioannis Papaefstathiou Prof. Garofalakis Minos

Chania, June 2017

## Abstract

Stream join consists one of the most resource-intensive operators in stream processing. Due to this characteristic, a big interest has been created in building high throughput and low latency systems which will be able to process real-time, bursty and rate varying data streams.

This thesis proposes an FPGA-based architecture which is based on one of the most efficient stream join algorithms, i.e ScaleJoin. The proposed architecture extends the first hardware-based architecture of the ScaleJoin algorithm. The first hardware implementation achieves high throughput and scalability but suffers from low resources utilization. In this thesis, we propose a novel architecture to achieve greater level of parallelism and exploit the available resources. Our system runs on Convey HC-2ex hybrid computer equipped with two six-core Intel Xeon E5-2640 processors running at 2.5 GHz and four Virtex 6 LX760 FPGAs. The experimental performance evaluation shows that our system totally outperforms the corresponding software-based solution and improves greatly the performance of the first hardware implementation.

### Keywords

Stream processing, stream join, ScaleJoin, stream join operator, FPGA architecture, reconfigurable logic

στους γονείς μου

## Ευχαριστίες

Θα ήθελα καταρχήν να ευχαριστήσω τον καθηγητή και επιβλέπων της παρούσας διπλωματικής κ. Απόστολο Δόλλα για το ενδιαφέρον που έδειξε από την πρώτη στιγμή, καθώς επίσης και τον αναπληρωτή καθηγητή κ. Ιωάννη Παπαευσταθίου και τον καθηγητή κ. Μίνω Γαροφαλάκη για την ευκαιρία που μου έδωσαν να ασχοληθώ με αυτό που ήθελα. Επίσης θα ήθελα να ευχαριστήσω ιδιαίτερα τον Γρηγόρη Χρυσό αλλά και τον Χρήστο Ρουσόπουλο για την πολύτιμη καθοδήγηση τους και τις ώρες που αφιέρωσαν για να με βοηθήσουν. Τέλος ευχαριστώ τους γονείς μου για τη στήριξη που μου έδειξαν καθ΄ όλη τη διάρκεια της φοίτησης μου αλλά και όλους τους κοντινούς μου ανθρώπους που μου στάθηκαν όλο αυτό το διάστημα.

Χανιά, Ιούνιος 2017

Καρανδεινός Χ. Έκτωρ

## Contents

| $\mathbf{A}$ | Abstract i |                                            |                                                   |    |

|--------------|------------|--------------------------------------------|---------------------------------------------------|----|

| E١           | υχαρ       | ιστίες                                     |                                                   | v  |

| 1            | Intr       | oducti                                     | ion                                               | 1  |

|              | 1.1        | Termi                                      | nology                                            | 1  |

|              | 1.2        | Contri                                     | ibution                                           | 4  |

|              | 1.3        | Thesis                                     | Structure                                         | 5  |

| 2            | Rela       | ated W                                     | Vork                                              | 7  |

|              | 2.1        | Stream                                     | n Mining Algorithms                               | 8  |

|              |            | 2.1.1                                      | Data Stream Clustering                            | 8  |

|              |            | 2.1.2                                      | Data Stream Classification                        | 8  |

|              |            | 2.1.3                                      | Frequent Pattern Mining                           | 9  |

|              |            | 2.1.4                                      | Change Detection in Data Streams                  | 9  |

|              |            | 2.1.5                                      | Stream Cube Analysis of Multi-dimensional Streams | 10 |

|              |            | 2.1.6                                      | Sliding Window Computations in Data Streams       | 10 |

|              | 2.2        | Stream                                     | n Mining Platforms                                | 10 |

|              | 2.3        | 3 Data Stream Join Processing              |                                                   | 12 |

|              |            | 2.3.1                                      | Software Based Implementations                    | 12 |

|              |            | 2.3.2                                      | Hardware Based Implementations                    | 14 |

| 3            | Scal       | leJoin                                     | Algorithm Analysis                                | 19 |

|              | 3.1        | The S                                      | caleJoin Algorithm                                | 19 |

|              |            | 3.1.1                                      | Problems and challenges                           | 19 |

|              |            | 3.1.2                                      | ScaleGate Data Structure                          | 20 |

|              |            | 3.1.3                                      | ScaleJoin Functionality                           | 21 |

|              | 3.2        | First Hardware Implementation of ScaleJoin |                                                   | 21 |

|                            | 3.3  | Thoug        | oughts For An Improved Hardware Implementation                                                   |    |  |  |  |  |

|----------------------------|------|--------------|--------------------------------------------------------------------------------------------------|----|--|--|--|--|

|                            |      | 3.3.1        | Improvements Needed                                                                              | 24 |  |  |  |  |

|                            |      | 3.3.2        | Design of Proposed Architecture                                                                  | 25 |  |  |  |  |

| 4                          | Scal | leJoin       | System                                                                                           | 29 |  |  |  |  |

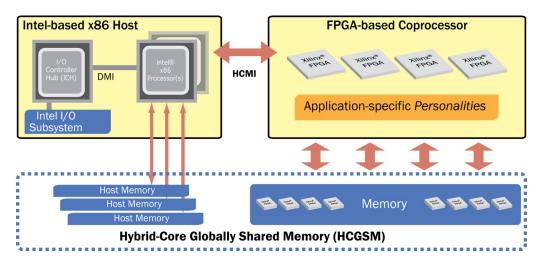

|                            | 4.1  | Conve        | y HC-2 Platform                                                                                  | 29 |  |  |  |  |

|                            |      | 4.1.1        | System Architecture                                                                              | 29 |  |  |  |  |

|                            |      | 4.1.2        | Coprocessor                                                                                      | 30 |  |  |  |  |

|                            |      | 4.1.3        | Personalities                                                                                    | 31 |  |  |  |  |

|                            | 4.2  | Recon        | figurable ScaleJoin System                                                                       | 33 |  |  |  |  |

|                            |      | 4.2.1        | C Code $\ldots$ | 34 |  |  |  |  |

|                            |      | 4.2.2        | Assembly Code                                                                                    | 34 |  |  |  |  |

|                            |      | 4.2.3        | Memory Controllers                                                                               | 35 |  |  |  |  |

|                            | 4.3  | ScaleJ       | oin Implementation                                                                               | 35 |  |  |  |  |

|                            |      | 4.3.1        | Data Inputs                                                                                      | 36 |  |  |  |  |

|                            |      | 4.3.2        | SetOfLines Module                                                                                | 37 |  |  |  |  |

|                            |      | 4.3.3        | LineOfPUs Module                                                                                 | 39 |  |  |  |  |

|                            |      | 4.3.4        | Processing Unit                                                                                  | 41 |  |  |  |  |

| <b>5</b>                   | Eva  | Evaluation 4 |                                                                                                  |    |  |  |  |  |

|                            | 5.1  | Result       | s Check                                                                                          | 45 |  |  |  |  |

|                            | 5.2  | Exper        | imental Setup                                                                                    | 45 |  |  |  |  |

|                            | 5.3  | Softwa       | are Evaluation                                                                                   | 46 |  |  |  |  |

| 5.4 Performance Evaluation |      |              | mance Evaluation                                                                                 | 48 |  |  |  |  |

|                            |      | 5.4.1        | HW vs. SW ScaleJoin Evaluation                                                                   | 48 |  |  |  |  |

|                            |      | 5.4.2        | First HW Implementation vs. Proposed Architecture                                                | 50 |  |  |  |  |

|                            |      | 5.4.3        | HW-based Implementations vs. SW-based Algorithms                                                 | 52 |  |  |  |  |

|                            | 5.5  | Conclu       | usions                                                                                           | 53 |  |  |  |  |

| 6                          | Con  | clusio       | n                                                                                                | 55 |  |  |  |  |

|                            | 6.1  | Future       | e Work                                                                                           | 55 |  |  |  |  |

|                            |      |              |                                                                                                  |    |  |  |  |  |

# List of Figures

| CellJoin                                                                                        | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Handshake Join                                                                                  | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Handshake Join Architecture on FPGA                                                             | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Handshake Join Architecture on FPGA                                                             | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ScaleJoin Architecture on FPGA                                                                  | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Overview Of ScaleJoin's Architecture                                                            | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Comparison Module                                                                               | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Processing Elements                                                                             | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Processing Unit                                                                                 | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Process Flowchart                                                                               | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Convey Hybrid Core System Diagram                                                               | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Coprocessor Diagram                                                                             | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| System Architecture Top Level                                                                   | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ScaleJoin Module                                                                                | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ScaleJoin Control                                                                               | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

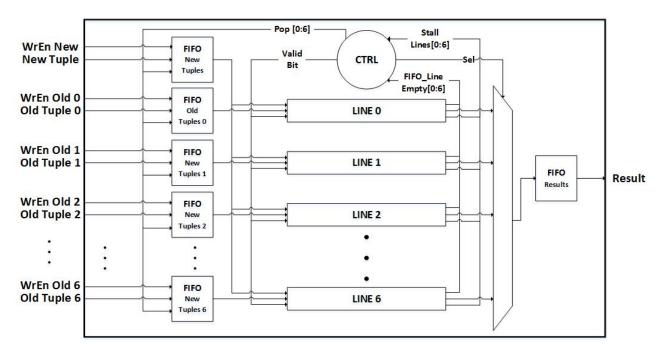

| SetOfLines Module                                                                               | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

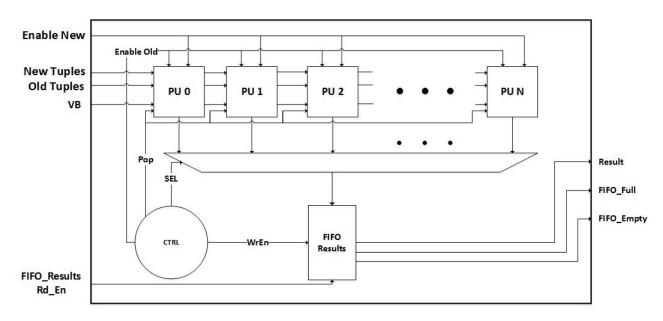

| LineOfPUs Module                                                                                | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

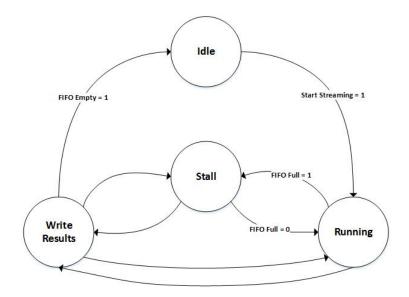

| LineOfPUs Control Unit                                                                          | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

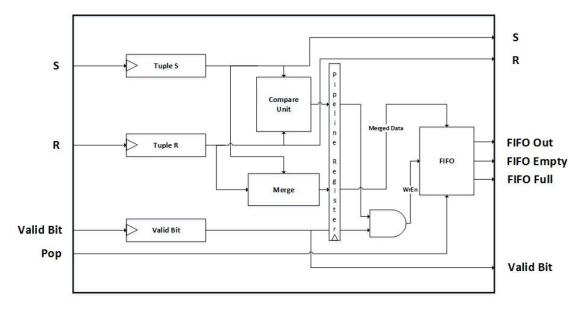

| Processing Unit                                                                                 | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

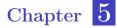

| Comparisons/sec for software-based multicore ScaleJoin and FPGA-based                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| solution                                                                                        | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

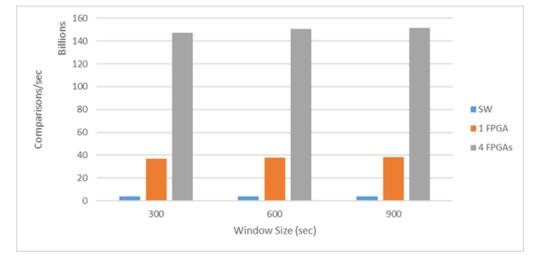

| Throughput (tuples/sec) for software-based multicore ScaleJoin and FPGA- $$                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| based solution                                                                                  | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

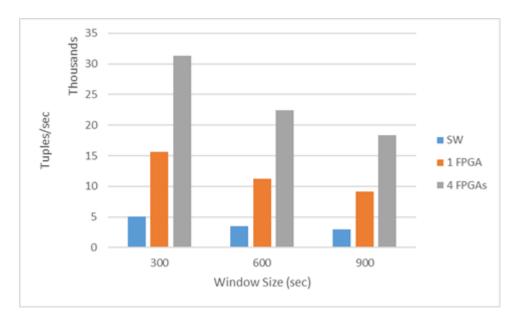

| Comparisons/sec for SW, $1^{\rm st}$ HW architecture and proposed architecture $% 1^{\rm st}$ . | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                 | Handshake JoinHandshake Join Architecture on FPGAHandshake Join Architecture on FPGAScaleJoin Architecture on FPGAOverview Of ScaleJoin's ArchitectureComparison ModuleProcessing ElementsProcessing UnitProcess FlowchartConvey Hybrid Core System DiagramCoprocessor DiagramScaleJoin ModuleScaleJoin ModuleScaleJoin ModuleConvey Hybrid Core System DiagramScaleJoin ModuleScaleJoin ModuleScaleJoin ControlScaleJoin ControlLineOfPUs ModuleLineOfPUs Control UnitComparisons/sec for software-based multicore ScaleJoin and FPGA-based<br>solutionThroughput (tuples/sec) for software-based multicore ScaleJoin and FPGA-<br>based solution |

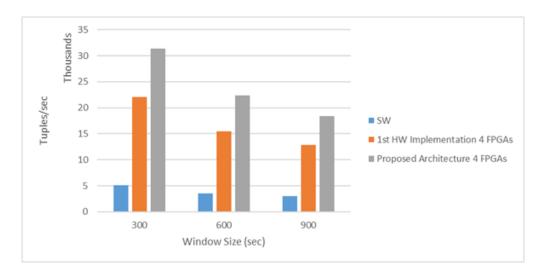

| 5.4 | Throughput (tuples/sec) for SW, $1^{\rm st}$ HW architecture and proposed archi- |    |

|-----|----------------------------------------------------------------------------------|----|

|     | tecture                                                                          | 51 |

# List of Tables

| 2.1 | Stream Mining Platforms                                                                                                                                                  | 11 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1 | System Resources Utilization                                                                                                                                             | 24 |

| 5.1 | System $S_1$ and $S_2$ throughput $\ldots \ldots \ldots$ | 47 |

| 5.2 | System Resources Utilization                                                                                                                                             | 48 |

| 5.3 | $Comparisons/sec \ for \ software-based \ multicore \ ScaleJoin \ and \ FPGA-based$                                                                                      |    |

|     | solution                                                                                                                                                                 | 49 |

| 5.4 | Throughput (tuples/sec) for software-based multicore ScaleJoin and FPGA- $$                                                                                              |    |

|     | based solution                                                                                                                                                           | 50 |

| 5.5 | Comparisons/sec for SW, $1^{\rm st}$ HW architecture and proposed architecture $% 1^{\rm st}$ .                                                                          | 51 |

| 5.6 | Throughput (tuples/sec) for SW, $1^{\rm st}$ HW architecture and proposed archi                                                                                          |    |

|     | tecture                                                                                                                                                                  | 52 |

| 5.7 | Proposed architecture compared with other software and hardware imple-                                                                                                   |    |

|     | mentations                                                                                                                                                               | 52 |

## Introduction

This chapter explains the main concepts of stream data mining in order to introduce the reader to the objectives of this thesis. Also, the terminology used in the following chapters is explained and analysed here. Last, this chapter describes the contribution of this thesis.

The chapter is organized as follows. In section 1.1 the basic terms used in the following chapters are explained, so that the reader becomes familiar with the concepts of this thesis' field. Also, an introduction to the field of stream data mining and more specifically to the stream join processing is made. Section 1.2 presents the contribution of this work. Finally, the structure of this thesis is analysed in section 1.3.

### 1.1 Terminology

#### Stream

In computer science, a stream is a sequence of data elements made available over time. A stream can be thought as items on a conveyor belt that are being processed one at a time rather than in large batches. Streams are processed differently from batch data since normal functions cannot operate on streams as a whole, as they have potentially unlimited data. In our case, we are concerned with stream processing, which is the continuous flow of data that is processed in a dataflow programming language, as soon as the program state meets the starting condition of the stream.

#### Tuple

A tuple is a data structure that consists of an ordered list of elements. Tuples are often used to describe other mathematical objects, such as vectors. In computer science, tuples are directly implemented as product types in most functional programming languages. More commonly, they are implemented as record types, where the components are labeled instead of being identified by position alone.

#### **Big Data**

Big data is a term for data sets that are so large or complex that traditional data processing applications are inadequate to deal with them. Challenges include analysis, capture, data curation, search, sharing, storage, transfer, visualization, querying, updating and information privacy. The term "big data" often refers simply to the use of predictive analytics, user behavior analytics, or certain other advanced data analytics methods that extract value from data, and seldom to a particular size of data set. Big data, usually includes data sets with sizes beyond the ability of commonly used software tools to capture, curate, manage and process data within a tolerable elapsed time. Big data "size" is a constantly moving target, as of 2012 ranging from a few dozen terabytes to many petabytes of data. Big data requires a set of techniques and technologies with new forms of integration to reveal insights from datasets that are diverse, complex, and of a massive scale. Finally, big data can be described by the following three characteristics:

- Volume: The volume of data implies scaling the storage and being able to perform distributed querying for processing. Solutions for the volume problem are either the use of data warehousing techniques or use parallel processing architecture systems.

- Velocity: Velocity deals with the rate in which data is generated and flows into a system. Everyday applications generate unbounded amount of information that can be used in many ways for predictive purposes and analysis. Velocity not only deals with the rate of data generation but also with the speed in which an analysis can be returned from this generated data. Having real-time feedback is crucial when dealing with fast evolving information such as stock markets, social networks, sensor networks, mobile information and many others.

- Variety: One problem in big data is the variety of data representations. Data can have many different formats depending on the source's nature, therefore dealing with this variety of formats can be challenging. Distributed key value stores, commonly referred as NoSQL databases, come in very handy for dealing with variety due to the unstructured way of storing data. This flexibility provides an advantage when dealing with big data. Traditional relational databases would imply restructuring

#### Karandinos C. Ektor - December 2016

the schemes and remodeling when new formats of data appear.

#### Stream Data Mining

Data Stream Mining is the process of extracting knowledge structures from continuous, rapid data records. Examples of data streams include computer network traffic, phone conversations, ATM transactions, web searches, and sensor data. Data stream mining can be considered a sub-field of data mining, machine learning, and knowledge discovery.

In many data stream mining applications, the goal is to predict the class or value of new instances in the data stream given some knowledge about the class membership or values of previous instances in the data stream. Machine learning techniques can be used to learn this prediction task from labeled examples in an automated fashion. In many applications, especially operating within non-stationary environments, the distribution underlying the instances or the rules underlying their labeling may change over time, i.e. the goal of the prediction, the class to be predicted or the target value to be predicted. This problem is referred as concept drift.

As one can easily understand, processing Stream and Data Mining algorithms combination cannot simply "work" to get Stream Data Mining. Many Data Mining algorithms are used to process streams but they need to match new challenges and make adjustments. An example of these challenges and adjustments is the input of the algorithm, which in streams is infinite in constrast with Data Mining, where the data is finite and the configured algorithm must have a real-time response. In Chapter 2 a more analytical reference is made to the problems that Stream Data Mining algorithms have and the challenges of each type of algorithm.

A fundamental operator for the data stream mining is the stream join operator. Stream join is used to correlate the information from different streams. The join operation, usually takes place over specific time-based windows due to the unbounded size of the data streams. The stream join operator is computationally expensive and there are many works that focus on accelerating its processing using distributed or parallel frameworks. There exist published works on how to accelerate stream join processing using multicore platforms [23][45][41][34] and other works that use hardware-based solutions [35][29][21]. Thus, the ScaleJoin algorithm [23] is a new, parallel formulation of the stream join operator that uses a shared-memory framework. The algorithm offers high performance results, outperforming any other state-of-the-art stream join implementation. The main advantages of the ScaleJoin algorithm is that it can process tuples coming from an arbitrary number of in-

put streams and it guarantees deterministic processing with scalable and high-throughput parallelism. ScaleJoin algorithm is presented and analysed in Chapter 3.

### 1.2 Contribution

This section describes the contributions of this thesis. The current work presents a hardware-based architecture for one of the state-of-the-art stream join algorithms, i.e. ScaleJoin.The proposed architecture achieves high throughput and outperforms any other software-based and hardware-based solutions on this problem. More analytically the contributions of our work are presented below.

- The current work improves the performance of the first hardware-based implementation for the ScaleJoin algorithm by proposing a new hardware architecture with a larger number of processing units (PUs) and greater parallelism.

- The proposed architecture outperforms any other previous, either software or hardwarebased, solutions for the stream join problem. More specifically our system carries out 38 times more comparisons per sec than the software-based solution, which runs on a high-end 48 core multiprocessor platform. The proposed system, also, manages to outperform the first hardware-based implementation of the ScaleJoin algorithm by two times as far as the comparisons rate per sec.

- The proposed hardware system offers greater throughput data rates than the previous proposed systems. In more details, the new system achieves at least 6 times better throughput data rate vs. the software solution and 1.4 times better rate vs. the first hardware-based solution.

- Our architecture exploits the full bandwidth of the Convey's HC-2ex memory and it almost doubles the utilization of the available resources.

- The proposed hardware-based architecture is scalable and generic, which means that it can be used for many different streaming problems that need to correlate streaming data.

### 1.3 Thesis Structure

The rest of this thesis is organized as follows. Chapter 2 presents algorithms and platforms regarding stream mining and makes an introduction to the stream join problem. In addition some of the most important implementations (software and hardware) in stream join processing are presented and analysed. Chapter 3 describes the ScaleJoin algorithm and its first hardware implementation. We address the improvements than can be made and make a first plan for our design. Chapter 4 presents and analyses our proposed architecture while in Chapter 5 takes place the evaluation of our work. Finally chapter 6 draws the conclusion of this work.

## **Related Work**

Data streams are infinite and high speed sequences of data instances. Mining of these large scale data streams to perform some kind of machine learning or futuristic predictions regarding data instances have drawn a significant attention of researchers in couple of previous years. The data streams resemble the real time incoming data sequence very well. The source of these data streams can be various sensors situated in medical domain to monitor health conditions of patients, in industrial domain to monitor manufactured products, etc. Other sources are user web click streams on social networking, e-commerce sites etc, twitter posts, various blogs, web logs, and many more [20] [8]. The above mentioned sources not only produce data streams, but they produce them in huge amount (of scale of tera bytes to peta bytes) and at rapid speed. Now, mining such huge data in real time raises various challenges and has become the hot area of research recently. These challenges include memory limitation and faster computing requirement.

The data stream mining task can be considered the same as traditional data mining task in terms of objective but quite different in terms of processing or executing the mining task. The reason behind this difference is the underlying challenges of infinite high speed data streams. This task, makes the traditional data mining algorithms and techniques incapable of appropriately handling data streams and yields the requirement of algorithms suitable for streaming data mining. This may be achieved in two ways; either modify the existing data mining algorithms to make them suitable for stream mining or create new streaming data mining algorithms right from the scratch. Something equally important data stream mining requires, is new platforms for computing and mining large scale data streams in real time. These platforms are required for various purposes such as data summarization, data streams aggregation from multiple sources, facilitating APIs for developing streaming data mining algorithms, etc. [17] [10] [7] [47] [43]. In this chapter, we address some of the main stream data mining algorithms and platforms in Sections 2.1 and 2.2. In Section 2.3, we point out the significance and the particularity of stream join processing. Finally, Sections 2.4 and 2.5 present some implementations of stream join algorithms implemented in software and hardware respectively.

### 2.1 Stream Mining Algorithms

#### 2.1.1 Data Stream Clustering

Clustering is a widely studied problem in the data mining literature. However, it is more difficult to adapt arbitrary clustering algorithms to data streams because of one-pass constraints on the data set. An interesting adaptation of the k-means algorithm has been discussed in [42], which uses a partitioning based approach on the entire data set. This approach uses an adaptation of a k-means technique in order to create clusters over the entire data stream. In the context of data streams, it may be more desirable to determine clusters in specific user defined horizons rather than on the entire data set. A technique worth mentioning is the micro-clustering technique [12], which determines clusters over the entire data set. There is also a variety of applications of micro-clustering, which can perform effective summarization based analysis of the data set. For example, microclustering can be extended to the problem of classification on data streams [13]. In many cases, it can also be used for arbitrary data mining applications such as privacy preserving data mining or query estimation.

#### 2.1.2 Data Stream Classification

The problem of classification is perhaps one of the most widely studied in the context of data stream mining. The problem of classification is made more difficult by the evolution of the underlying data stream. Therefore, effective algorithms need to be designed in order to take temporal locality into account. A wide variety of data stream classification algorithms exist, some of them are designed to be purely one-pass adaptations of conventional classification algorithms [36], whereas others (such as the methods in [13] and [19]) are more effective in accounting for the evolution of the underlying data stream. Classic example of Stream Classification algorithms is Very Fast Decision Trees algorithm (VFDT) or Hoeffding Trees developed by Domingos and Hulten [15] and it is also used in Samoa. This algorithm splits the tree using the current best attribute taking into account that the number of examples used satisfies the Hoeffding bound. VFDT is an extended version of

#### Karandinos C. Ektor - December 2016

such a method which can address the research issues of data streams. Another algorithm worth mentioning is the on Demand Classification. Aggarwal et al. have adopted the idea of micro-clusters introduced in CluStream [27] in On-Demand classification in [9]. The on-demand classification method divides the classification approach into two components. One component constantly stores summarized statistics about the data streams and the second one, continuously, uses the summary statistics to perform the classification. The summary statistics are represented in the form of class-label specific micro-clusters. This means that each micro-cluster is associated with a specific class label, which defines the class label of the points in it.

#### 2.1.3 Frequent Pattern Mining

The problem of frequent pattern mining was first introduced in [38], and was extensively analyzed for the conventional case of disk resident data sets. In the case of data streams, one may wish to find the frequent itemsets either over a sliding window or the entire data stream [14] [39]. Frequent patterns can not only effectively summarize the underlying datasets, providing key sights into the data, but also serve as the basic tool for many other data mining tasks, including association rule mining, classification, clustering, and change detection among others [26] [25] [28]. Many efficient frequent pattern algorithms have been developed in the last decade [22] [24] [30]. These algorithms typically require datasets to be stored in persistent storage and involve two or more passes over the dataset. Recently, there has been much interest in data arriving in the form of continuous and infinite data streams. In a streaming environment, a mining algorithm must take only a single pass over the data. Such algorithms can only guarantee an approximate result.

#### 2.1.4 Change Detection in Data Streams

An important problem in the field of data stream analysis is change detection and monitoring. In many cases, the data stream can show changes over time, which can be used for understanding the nature of several applications. In many cases, it is desirable to track and analyze the nature of these changes over time. In [44] [16] [11], a number of methods have been discussed for change detection of data streams. The presence of evolution in data streams may also change the underlying data to the extent that the underlying data mining models may need to be modified to account for the change in data distribution.

#### 2.1.5 Stream Cube Analysis of Multi-dimensional Streams

Much of stream data resides at a multi-dimensional space and at rather low level of abstraction, whereas most analysts are interested in relatively high-level dynamic changes in some combination of dimensions. To discover high-level dynamic and evolving characteristics, one may need to perform multi-level, multi-dimensional on-line analytical processing (OLAP) of stream data. Such necessity calls for the investigation of new architectures that may facilitate on-line analytical processing of multi-dimensional stream data [46] [18].

#### 2.1.6 Sliding Window Computations in Data Streams

Many of the synopsis structures which are discussed, use the entire data stream in order to construct the corresponding synopsis structure. The sliding-window model of computation is motivated by the assumption that it is more important to use recent data in data stream computation [32]. Therefore, the processing and the analysis is only done on a fixed history of the data stream. To be more specific data elements arrive at every instant; each data element expires after exactly N time steps; and, the portion of data that is relevant to gathering statistics or answering queries is the set of last N elements to arrive. The sliding window refers to the window of active data elements at a given time instant and window size refers to N.

### 2.2 Stream Mining Platforms

Stream mining platforms are the frameworks that facilitate creation or collection of data streams as well as integration of various algorithms and APIs of stream mining to enable a developer or user to easily mine the data streams and evaluate the results. List of various data stream mining platforms along with their main focus are listed in Table 1. The stream processing frameworks listed in Table 2.1 can be categorized into three basic units. First unit includes stream preprocessing frameworks [9-12,57-58] that perform collection, filtering, aggregation and integration over data streams. Second unit of frameworks include stream processing engines that facilitate libraries and APIs, which provide faster manipulation of data streams such as S4 [31], Storm [4], Spark [47], Samza [2], etc. and facilitate streaming data mining libraries such as MOA [6], Spark [47], SAMOA [37], etc. Third unit of frameworks usually focus on analytical processing such as SQLstream Blaze [1], Pulser [33], etc. The distributed processing frameworks, have received a lot of attention from research and industries. These frameworks can handle huge scale of streaming data

#### Karandinos C. Ektor - December 2016

| Stream Mining Platform               | Year | Major Focus                                                                                                                                                                                                                                                                  |

|--------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Aurora [17]                          | 2003 | Faster computing of data streams (from multiple                                                                                                                                                                                                                              |

| Autora [17]                          | 2003 | sources) as defined by application administrator.                                                                                                                                                                                                                            |

| Scribe [10]                          | 2004 | Real time aggregation of streaming data from various                                                                                                                                                                                                                         |

|                                      |      | sources                                                                                                                                                                                                                                                                      |

| Borealis [7]                         | 2005 | Used for faster processing of incoming data streams.                                                                                                                                                                                                                         |

| Vowpal-Wabbit [3]                    | 2007 | Scalable, fast computing and integration of variety of data.                                                                                                                                                                                                                 |

| MOA [6]                              | 2010 | Performs low scale data stream computing. A GUI based framework that contains bulk of streaming data mining algorithms.                                                                                                                                                      |

| Apache S4 [31]                       | 2010 | Distributed faster data stream processing engine.                                                                                                                                                                                                                            |

| Apache Spark [47]                    | 2010 | Provides in memory data stream computation plat-<br>form on Hadoop data stores. It is 10 times faster<br>than MapReduce computation paradigm of Hadoop.                                                                                                                      |

| Storm [4]                            | 2011 | Distributed faster data stream processing engine.                                                                                                                                                                                                                            |

| Samza [2]                            | 2013 | A fault tolerant and scalable distributed framework                                                                                                                                                                                                                          |

| Saliiza [2]                          | 2015 | for data stream processing.                                                                                                                                                                                                                                                  |

| SAMOA [37] [40]                      | 2013 | Provides large scale data stream computation<br>through distributed framework. It can be easily in-<br>tegrated with other stream processing engines such<br>as Storm and S4. Also, it has library of distributed<br>mining algorithms for streams of data.                  |

| Amazon Kinesis [43]                  | 2013 | A cloud based service that provides real time dis-<br>tributed processing of large scale data streams. It<br>can potentially capture terabytes data per hour,<br>coming from thousands of sources such as financial<br>transactions, web lick streams, social media, etc.    |

| streamDM $[5]$                       | 2014 | An open source framework that collaborates with<br>apache spark and is effective in mining big scale data<br>streams.                                                                                                                                                        |

| Kafka Integrated SQLstream Blaze [1] | 2014 | Provides high performance distributed processing of<br>data streams via SQLstream Blaze stream processing<br>suite, for real time aggregation, analysis and visual-<br>ization of large scale data streams.                                                                  |

| Pulser [33]                          | 2015 | Open source framework for capable of capturing and<br>processing large scale (around million) events and an-<br>alytics in seconds. It can create custom data streams<br>in order to perform real time business activity mon-<br>itoring and reporting, fraud detection etc. |

computation and analytics.

Table 2.1: Stream Mining Platforms

The stream processing frameworks listed in Table 2.1 can be categorized into three basic units. First unit includes stream preprocessing frameworks [9-12,57-58] that perform collection, filtering, aggregation and integration over data streams. Second unit of frameworks include stream processing engines that facilitate libraries and APIs, which provide faster manipulation of data streams such as S4 [31], Storm [4], Spark [47], Samza [2], etc. and facilitate streaming data mining libraries such as MOA [6], Spark [47], SAMOA [37], etc. Third unit of frameworks usually focus on analytical processing such as SQLstream Blaze [1], Pulser [33], etc. The distributed processing frameworks, have received a lot of at-

tention from research and industries. These frameworks can handle huge scale of streaming data computation and analytics.

### 2.3 Data Stream Join Processing

Given the fundamental role that is played by joins in querying relational databases, it is not surprising that stream join has also been the focus of much research on streams. Recall that relational (theta) join between two non-streaming relations R1 and R2, denoted  $R1 \bowtie R2$ , returns the set of all pairs  $\langle r1, r2 \rangle$ , where  $r1 \in R1$ ,  $r2 \in R2$ , and the join condition  $\theta(r1, r2)$  evaluates to true. A straightforward extension of join to streams gives the following semantics (in rough terms): At any time t, the set of output tuples generated thus far by the join between two streams S1 and S2 should be the same as the result of the relational (nonstreaming) join between the sets of input tuples that have arrived thus far in S1 and S2.

Stream join is a fundamental operation for relating information from different streams. This is especially useful in many applications such as sensor networks, where the streams that arrive from different sources may need to be related with one another. Due to the high computational cost of stream joins, a big interest has been created in achieving high throughput and low latency. For this reason, many implementations have been proposed both in software and hardware. The main goal of these implementations is to parallelize the processing of stream joins. Most of such works use multi-core CPUs, field programmable gate arrays (FPGAs) or massively parallel processor arrays (MPPAs). Some of the above implementations are presented below.

#### 2.3.1 Software Based Implementations

#### CellJoin [21]

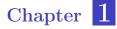

CellJoin is an algorithm that follows a three-step procedure for stream join, as described by Kang *et al.*[cytation here]. CellJoin algorithm is mapped on a cell processor, which is an heterogeneous multi-core architecture. The algorithm parallelizes the scan task over the available processing units achieving high performance. The main idea of the algorithm is based on the assignment of each in-memory window partition of one stream to the available CPU cores so that the scan is parallelized. Although CellJoin achieves low latency, its scalability is very limited due to the re-partition needed every time a new tuple arrives. The overhead of window re-partitioning grows linearly with the core number and the input

### Karandinos C. Ektor - December 2016

stream rate causing CellJoin algorithm to scale poorly.

Figure 2.1: CellJoin

#### Handshake Join [45]

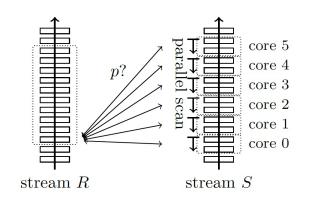

Handshake Join algorithm main goal is to scale out to very high degrees of parallelism in order to avoid the bottleneck that occurs with traditional approaches (CellJoin). To understand how Handshake Join works we can resemble it with soccer players. To be more specific, as soccer players, before the begging of every match shake hands, by walking in opposite directions, Handshake Join compare both streams, flowing in opposite directions, in parallel. This implementation is scalable enabling the use of multiple cores to increase the window size without limiting performance. Handshake Join replaced the classical three-step procedure, which was used by the stream join implementations.

#### Low Latency Handshake Join [41]

Low Latency Handshake Join algorithm, aims to maintain the positive characteristics of the original algorithm (scalability and high throughput). At the same time, it attempts to reduce latency and produce a deterministically ordered output. The high latency of the original algorithm is caused due to the queuing of tuples along the distributed windows. To avoid that bottleneck Low Latency Handshake Join forwards newly incoming tuples and stores them into a node-local window on the core that they belong. This way, each incoming tuple is "seen" by all involved processing units, it is stored in the respected nodelocal window and then it is discarded. After all the comparisons are made with a specific tuple it is removed from the node by an expiry message. Finally, a punctuation mechanism with very little overhead is used, to sort the output data and offer a deterministic result.

Figure 2.2: Handshake Join

#### SplitJoin [34]

One of the latest implemented algorithms for stream join is SplitJoin algorithm. SplitJoin main contribution is the split of the sequential operation model. More specifically instead of following the classic process, first store and then process the newly incoming tuples, SplitJoin abstract these computation steps as two concurrent and independent steps ("storage" and "processing"). This splitting allows parallel execution and high scalability, which can be further improved by dividing the sliding window into a set of disjoint sub-windows each one assigned to a different join core through a distribution tree. In addition to the splitting of the join computation, SplitJoin algorithm introduces a single top-down data flow instead of the bi-directional data flow models (Handshake Join). This way there is no linear latency overhead as the join cores are no longer chain connected but completely independent, avoiding as well the inter-core communication overhead.

#### 2.3.2 Hardware Based Implementations

#### Handshake Join on FPGA [45]

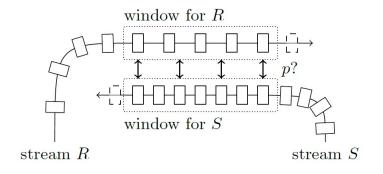

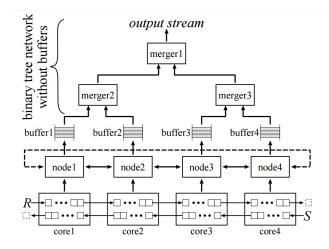

The basic idea of Handshake join is to execute window based stream join operation on two streams flowing in opposite directions in order to achieve high scalability and parallelization. To implement this concept on hardware, three issues have to be taken into account. First of all, the result collection, second the capacity of output channel and third the limitation of internal buffer sizes. The core of the proposed architecture is the join core which is the most fundamental component of the architecture. Its purpose is to evaluate the join condition over the input tuples and generate the output that form the final result. The generated results are then driven into a network of mergers which merge the valid result data streams into one. This network is in fact a binary tree of mergers, whose number is determined by the number of join cores. Finally an admission control is used in order to avoid result losses due to buffer overflows. An overview of handshake implementation in reconfigurable logic is shown in Figure 2.3 below.

Figure 2.3: Handshake Join Architecture on FPGA

#### Handshake Join Operator on FPGA [35]

An improvement of the Handshake join implementation on FPGA is the Handshake Join Operator. Although it is stated in [45] that the merging network supports high degrees of parallelism and that it is highly scalable, the truth is that it is an overwhelming bottleneck for scalable performance. Due to this fact, an adaptive merging network is proposed, which removes the FIFO buffers in the network and it introduces a ring structure, which is directly connected to the join cores. This way, an output result tuple from a join core is always forwarded and stored in a FIFO buffer (before the merging network). It is important to mention that the chosen buffer FIFO does not need to be at the closest path where the join took place. This way the system avoids buffer overflows. The top-level of this implementation of Handshake join is shown in Figure 2.4.

Figure 2.4: Handshake Join Architecture on FPGA

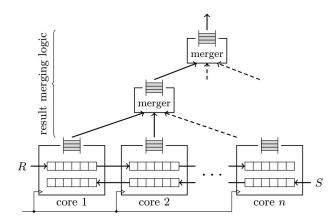

#### ScaleJoin Architecture on FPGA [29]

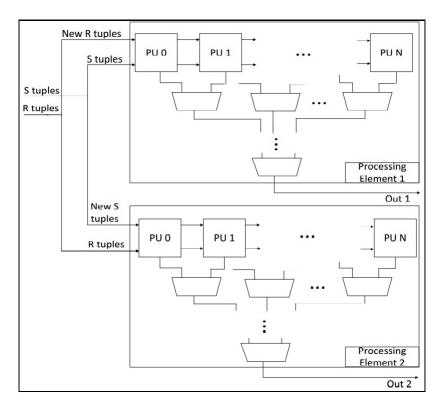

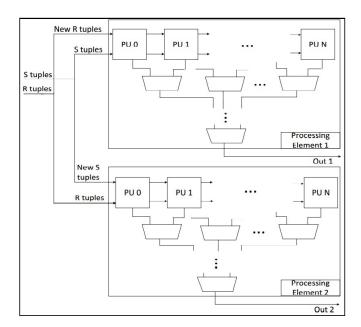

The first implementation of ScaleJoin algorithm on reconfigurable logic, achieves at least four times higher throughput over the original multi-thread software solution. The architecture consists of two processing elements, which in their turn consist of N processing units connected in a pipeline way. Each processing element is responsible for comparing the newly arrived tuples of one stream with the tuples of the opposite stream inside a window and each processing unit takes care of the comparison. The process is broken in

Figure 2.5: ScaleJoin Architecture on FPGA

three stages. First, the newly arrived tuples are loaded in the processing units, second the tuples are streamed through the pipeline of processing units and finally, the results are written back in memory. This implementation offers high throughput due to the large number of processing units available (128 in each processing element), as well due to the high parallelization upon the overall comparisons.

## Chapter 3

## ScaleJoin Algorithm Analysis

In this chapter we are going to analyse ScaleJoin algorithm, one of the most efficient algorithm in data stream join operations. A detailed description of how ScaleJoin algorithm works, its basic components and the performance results are some of the main features that will be presented. Also, the first hardware implementation of ScaleJoin is going to be analysed, in order to note the improvements needed. Finally, based on some observations we propose our architecture, which improves the first hardware-based implementation offering higher throughput.

### 3.1 The ScaleJoin Algorithm

ScaleJoin algorithm [23], is a state-of-the art stream join algorithm capable of processing efficiently bursty and rate-varying data streams. It offers deterministic and skew-resilient stream processing, while also enabling fine-grain parallelism to achieve high throughput and low latency stream processing. It is based on an abstract data structure, ScaleGate, which operates at the articulation points maintaining the tuples being consumed and produced in a deterministic fashion regardless of the number of processing units or the number of physical streams delivering to them. ScaleJoin allows for the parallel execution of an arbitrary number of sequential stream joins while distributing the overall work among the available processing threads, without assuming any centralized coordinator.

#### 3.1.1 Problems and challenges

The main problems and challenges that ScaleJoin algorithm has to face are deterministic processing, disjoint parallelism and skew-resilience. Below is a brief description of foregoing challenges/problems.

Figure 3.1: Overview Of ScaleJoin's Architecture

#### **Deterministic Processing**

Given the same inputs in a method, the same outputs must be produced independently of its environment. This requirement allows for a parallel stream join to be leveraged in sensitive scenarios (fraud detection or business-centric pricing applications) and to leverage fault tolerance mechanisms, in which deterministic processing ensures consistency among primary and replica nodes.

#### **Skew Resilience**

The ability to process any varying rate of incoming tuples independently by each processing thread. Also, the process of a possible different number of physical streams delivering tuples should not affect the functionality of the algorithm but tuples' comparisons should be assigned to a unique processing thread.

#### **Disjoint Parallelism**

ScaleJoin does not rely on a centralized coordinator to assign the workload on processing units sequentially. Every processing thread available (n total processing threads) executes  $\frac{1}{n}$  comparisons splitting evenly the overall workload. This way architectures that support high degrees of parallelism are leveraged achieving higher throughput and lower processing latency.

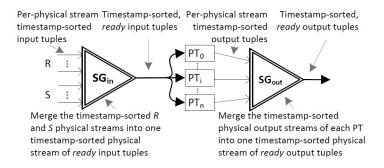

#### 3.1.2 ScaleGate Data Structure

As we mentioned before, ScaleJoin introduces ScaleGate, an abstract data type responsible of maintaining the tuples being consumed and produced in a deterministic fashion, regardless of the number of processing units or the number of physical streams delivering

#### Karandinos C. Ektor - December 2016

to them. Inspired by skip lists, a multi level pointer mechanism is designed and adopted to the ScaleGate requirements. This way, fine-grained synchronization is achieved, which in its turn boosts parallelism. ScaleGate is a lock-free implementation ensuring system-wide progress, by guaranteeing at least one of the threads operating on the data structure to make progress independently of the behavior of other threads. It is also linearizable, meaning that every method call should appear to take effect at some point (linearization point) between its invocation and response. Given these attributes, ScaleGate is able to define a total order in the execution, which is consistent with the real-time ordering of operations, maintaining items in a sorted manner.

#### 3.1.3 ScaleJoin Functionality

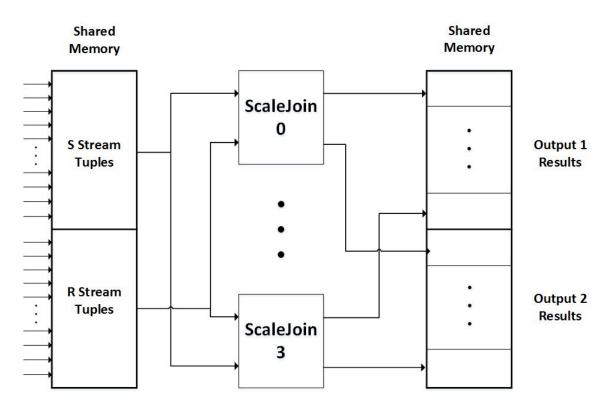

As already mentioned and shown in figure 3.1, ScaleJoin allows the parallel execution of an arbitrary number n of processing threads (PTs), each consuming, comparing and matching the input tuples delivered by S and R streams. This process is a modified version of the three-step procedure. To be more specific, the first step, which is is responsibility of the input ScaleGate structure  $(SG_{in})$ , is to merge the input tuples of each stream into a single timestamp-sorted stream of ready R and S tuples. A ready tuple is defined as ready to be processed, if assuming a tuple  $t_i^j$  to be the i-th tuple from a timestamp-sorted stream j,  $t_i^j < merge_{ts}$ , where  $merge_{ts}$  is the minimum among the latest timestamps from each timestamp-sorted stream j. The ready tuples afterwards are sent by the ScaleGate to the PTs in a round robin fashion. The PTs in their turn compare the incoming ready tuple, using a predicate P, with each tuple of the opposite stream inside a window size interval from the tuple. If P holds, an output tuple is created, combining the tuples from the two streams and it is sent to the ScaleGate at the output of the architecture  $(SG_{out})$ .  $SG_{out}$ then sorts by timestamp the incoming output tuples and sends them as the final system output.

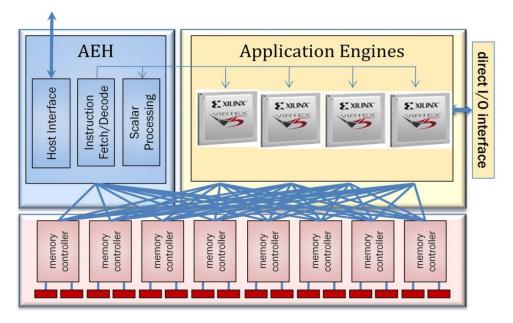

# 3.2 First Hardware Implementation of ScaleJoin

A first implementation of ScaleJoin algorithm was proposed in reconfigurable logic about a year ago, outperforming the other state of the art software-based multi-core solutions. The reconfigurable architecture was mapped on Convey HC-2ex hybrid computer equipped with an Intel Xeon E5-2640 processor at 2.5 GHz and four Virtex-6 LX760 FP-GAs. The implemented system achieves at least four times better throughput vs. the original ScaleJoin algorithm [23]. In this section we present a top-down analysis of the

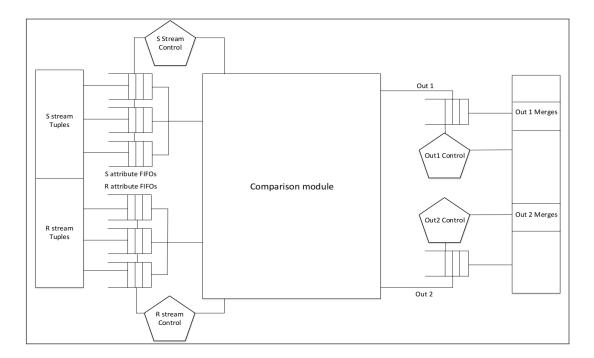

Figure 3.2: Comparison Module

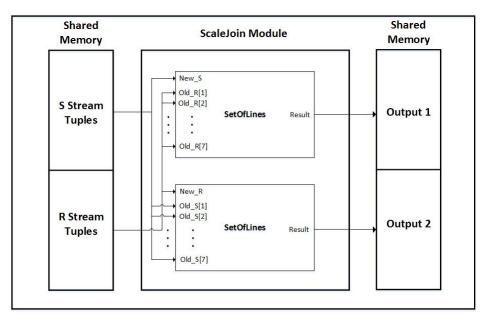

first hardware implementation of ScaleJoin algorithm. The top level of this architecture is the Comparison module, shown in Figure 3.2. This unit is mapped inside each of the four FPGAs of Convey HC-2ex hybrid computer. Along with this module, there are several control units responsible for managing the data inputs from the memory controllers of the system. This architecture uses 14 out of the 16 available memory controllers. Only two of the memory controllers utilize the full bandwidth of 64 bits, while the rest utilize only 32 bits.

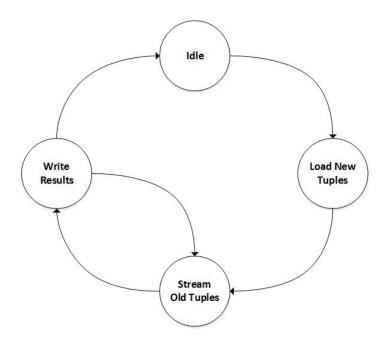

As we mentioned in Section 2.3.2 Comparison module consists of two processing elements, which in their turn consist of N processing units connected in a pipeline way. In this case, each processing element has 128 PUs, which means that there is a total of 256 PUs in each Comparison module. Each processing element is responsible for comparing the newly arrived tuples of one stream with the tuples of the opposite stream inside a window and each processing unit calculates the corresponding correlations. The process is split in three stages with the first one being the load of the new incoming tuples to the corresponding processing element. After that, the old tuples of each stream are streamed through the pipeline of PUs so that all the comparisons between the tuples take place. If the processed tuples produce a result, this result's information is kept into a FIFO at each PU. Then this information is forwarded through a network of multiplexers to the output

Figure 3.3: Processing Elements

in order to be stored back to memory. When all the tuples from the processing window are streamed and all the results are stored to memory the process finishes. This process takes place again every second or many times during a single second, in case the newly arrived tuples are more than the available PUs. This whole process is controlled by several control units that manage the input and streaming of the tuples, as well as the possible stalls and results.

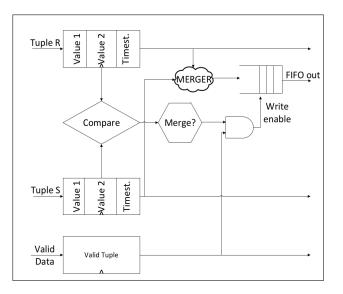

Figure 3.4: Processing Unit

Finally, the innermost unit of this architecture is the processing unit (PU). This module is responsible for comparing the tuples of the input streams. If the comparison is successful a new tuple is created, that hold information for the achieved correlation. This new tuple is kept in a FIFO inside the PU, until the global control forwards it to the output, so that it is stored to memory. Figure 3.4 shows the architecture of the PU.

# 3.3 Thoughts For An Improved Hardware Implementation

In this section we are going to present the features that limit the performance of the first hardware implementation of ScaleJoin algorithm and propose our thoughts for a new design that will improve the existing performance.

#### 3.3.1 Improvements Needed

Although the first architecture achieves high throughput and outperforms the state of the art software-based implementations, further improvements can be made to accomplish even greater performance results. The main reasons that limit the performance results are:

- The clock frequency achieved, as well as the timing errors of the first hardware implementation confine the performance. The reconfigurable part of Convey's HC-2ex can reach a clock frequency of up to 150 MHz, something that would significantly leverage processing throughput.

- The resources utilization of the first implementation, as shown in Table 3.1, is less than 30% of the available resources Convey HC-2ex offer. This was due to routing issues of the design, that could not let a larger design to be mapped.

- Only 14 out of the 16 available memory controllers offered by the platform are used and only two of them use the full bandwidth. A better management of the memory controllers has to be made, in order to take advantage of the full bandwidth of all the available memory controllers.

| FPGA Available Resources | System Utilization  |

|--------------------------|---------------------|

| DSPs                     | 0/864~(0%)          |

| Slice Registers          | 158777/948480 (16%) |

| Slice LUTs               | 151688/474240 (31%) |

| Block RAMs               | 114/720 (15%)       |

Table 3.1: System Resources Utilization

In order to address the above mentioned issues, a new architecture should be proposed that will overcome the problems that limit the first hardware implementation of the

ScaleJoin algorithm.

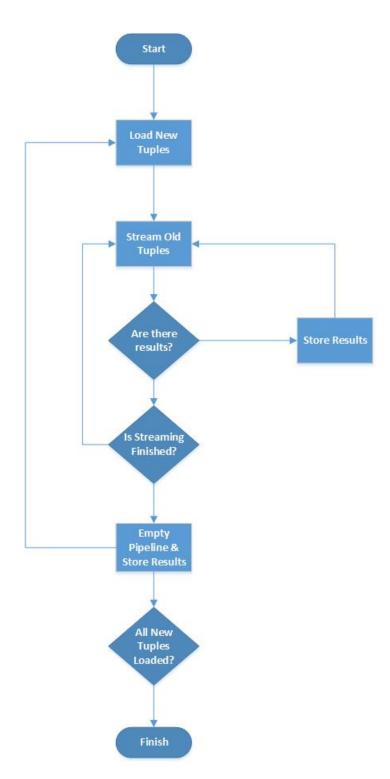

### 3.3.2 Design of Proposed Architecture

Based on the observations we made on the first hardware implementation of ScaleJoin algorithm, as well as on the software algorithm itself, we analysed the way our implementation is structured, its processing steps and how we plan to overcome the issues that appeared in the first hardware implementation.

#### **Clock Frequency**

Regarding the clock frequency we had to locate the longest data path delay (critical path), which is responsible for the system's clock frequency and the timing errors that appeared. We concluded that the critical path was inside the implemented processing unit (PU) due to the comparison that takes place there. To address this issue we chose to alter PU's implementation and build a pipelined architecture, in order to reduce the critical path and increase the clock frequency.

#### **Resources Utilization**