Technical University of Crete School of Electronics and Computer Engineering Department of Electronics and Computer Engineering

### Memory System Evaluation of Disaggregated High Performance Parallel Systems

**Orion** Papadakis

Thesis Commitee: Prof. Dionisios N. Pneumatikatos (ECE) (Supervisor) Prof. Vasilis Samoladas (ECE) Dr. Dimitris Theodoropoulos (ECE)

Submitted in part fulfilment of the requirements for the diploma of Electronics and Computer Engineering, April 2017

#### Abstract

Supercomputers or High Performance Computers (HPC), traditionally play a significant role either in the Computer Architecture scientific field, or in the Computer Science, due to their usage in manner computing processes, scientific research and applications. Consequently, the study around them, as well as, the Memory System performance and size study is necessary about their further evolve, due to the traditional bottleneck between Memory and CPU speed (memory gap). Large resources inefficiencies (mostly in Memory) as well as, significant power consumption regarding to the current Cloud Data Center structure, have been observed. Their mainboard-oriented monolithic structure fails to operate in an optimal way with the hardware, corresponding to the modern application needs. Larger Data Center are being built, in response to that problem, a strategy which leads to even more power consumption. The nowadays research about Disaggregated Architecture Systems, study those problems. It aims to change the traditional mainboard-organized Data Center structure by proposing a more flexible and software-controlled one, organized around Pooled Disaggregated Resources.

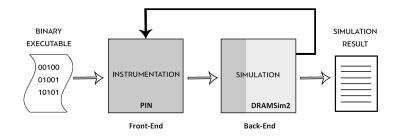

The current diploma thesis is part of the DiMEM Simulator, a modular execution-driven Disaggregated Memory Simulation tool study and implementation. That tool approximately tries to depict the Disaggregated Memory System behaviour using HPC workload. The DiMEM Simulator couples the Intel PIN framework with DRAMSim2 Memory Simulator, where that thesis also focuses. The main study object are the DRAMs, the Memory Simulation methods, the Disaggregated Memory Simulation implementation, as well as the parameters experimentation. The presented results show the approximated Disaggregated Memory System behaviour.

#### Περίληψη

Οι Υπερυπολογιστές ή Υπολογιστές Υψηλών Επιδόσεων (High Performance Computers) διαχρονικά, κατέχουν σημαντικό ρόλο στο πεδίο της Αρχιτεκτονικής Υπολογιστών αλλά και γενικότερα στην Επιστήμη Υπολογιστών καθώς χρησιμοποιούνται σε ιδιαίτερα απαιτητικές υπολογιστικά εργασίες και βαρύνουσας σημασίας επιστημονική έρευνα και εφαρμογές. Συνεπώς η μελέτη τους, και πιο συγχεχριμένα, η μελέτη των συστημάτων μνήμης τους όσον αφορά τις επιδόσεις χαι το μέγεθός τους είναι αναγκαία για την περαιτέρω ανάπτυξη των συστημάτων αυτών καθώς παραδοσιακά το (memory gap-wall) παίζει επιβραδυντικό ρόλο στις ήδη υψηλές επιδόσεις των επεξεργαστών. Όσον αφορά την υπάρχουσα δομή των μεγάλων Cloud Data Centers παρατηρείται σημαντική σπατάλη πόρων (κυρίως μνήμης) και υψηλή κατανάλωση ενέργειας. Η μονολιθική τους δομή με επίκεντρο το mainboard δεν αξιοποιεί βέλτιστα το hardware για τις ανάγχες των εφαρμογών χαι εμφανίζονται ανεπάρχειες. Έτσι, προχειμένου να επιστρατευτούν οι αναγχαίοι πόροι, χτίζονται πιο μεγάλα Data Centers, πραχτιχή που οδηγεί μεταξύ άλλων και στην ακόμα υψηλότερη κατανάλωση ενέργειας. Στην κατεύθυνση αυτή, βρίσκονται υπο έρευνα και μελέτη Συστήματα Απομακρυσμένης/Επιμερισμένης Αρχιτεκτονικής (Disaggregated Architecture Systems). Η Αρχιτεκτονική αυτή στοχεύει να αλλάξει τον παραδοσιακό τρόπο οργάνωσης ενός Data Center, προτείνοντας την μεταχόμιση από την ενοποίηση γυρω από το mainboard σε μια πιο ευέλιχτη χαι μεταβαλόμενη από το software ενοποίηση γύρω από blocks, τις Επιμερισμένες  $\Delta$ εξαμενές Πόρων (Pooled Disaggregated Resources).

Η διπλωματική αυτή είναι κομμάτι της μελέτης και ανάπτυξης ένα ενοποιημένου (modular) εργαλείου προσομοίωσης μνήμης «οδηγούμενο» από την εκτέλεση ενός προγράμματος (execution driven) με σκοπό να αποτυπωθεί προσεγγιστικά η συμπεριφορά του τυπικού HPC φόρτου εργασίας σε συνθήκες Μνήμης Επιμερισμένης Αρχιτεκτονικής. Το εργαλείο συνενώνει το Intel Pin Framework με τον προσομοιωτή Μνήμης DRAMSim2 όπου και επικεντρώνεται η διπλωματική. Αντικείμενο μελέτης είναι οι μνήμες DRAM καθώς και οι μέθοδοι προσομοίωσής τους, η υλοποίηση της προσομοίωσης Μνήμης Επιμερισμένης Αρχιτεκτονικής, και ο πειραματισμός με τις διάφορες παραμέτρους. Τα αποτελέσματα που παρουσιάζονται αποτυπώνουν προσεγγιστικά τη γενικότερη συμπεριφορά ενός συστήματος Μνήμης Επιμερισμένης Αρχιτεκτονικής.

## Acknowledgements

First and foremost, I would like to thank my advisor, Professor Dionisios N. Pnevmatikatos for his motivation, immense knowledge and for giving me the opportunity to work on this very interesting topic.

Also I would like to thank Dr.Dimitris Theodoropoulos for his technical support during this thesis.

I would like to thank my colleague Andreas Andronikakis, that without our productive collaboration, our whole work and study would have never been accomplished.

Moreover, I would like to thank all those friends who during my studies were always supportive and created for me millions of beautiful memories.

Finally, most of all, I would like to thank my family for their enormous help, understanding and supporting me in all levels.

# Contents

| $\mathbf{A}$ | bstra | ict     |                                                          | i  |

|--------------|-------|---------|----------------------------------------------------------|----|

| 1            | Intr  | roducti | ion                                                      | 1  |

| 2            | Bac   | kgrou   | nd And Related Work                                      | 4  |

|              | 2.1   | Backg   | round                                                    | 4  |

|              |       | 2.1.1   | DRAM Technology Overview                                 | 4  |

|              |       | 2.1.2   | General Simulation Techniques: Execution or Trace Driven | 8  |

|              |       | 2.1.3   | DRAMSim2 Memory Simulator Overview                       | 11 |

|              |       | 2.1.4   | Disaggregated Systems                                    | 20 |

|              | 2.2   | Relate  | ed Work                                                  | 21 |

| 3            | DIN   | AEM S   | Simulator: Overall Approach                              | 23 |

|              | 3.1   | Binary  | y Instrumentation                                        | 23 |

|              | 3.2   | Memo    | ry Simulation                                            | 24 |

|              |       | 3.2.1   | The Reordering Window Technique                          | 25 |

|              |       | 3.2.2   | Preparation of Simulation                                | 26 |

|   |     | 3.2.3 Memory Simulation: Calling DRAMSim2 | 31 |

|---|-----|-------------------------------------------|----|

|   | 3.3 | Skip Mode Feature                         | 36 |

|   | 3.4 | Simulation Output                         | 37 |

| 4 | Eva | luation and Experimental Results          | 41 |

|   | 4.1 | CPU Configurations and Metrics            | 41 |

|   | 4.2 | DRAM Configurations and Metrics           | 42 |

|   | 4.3 | Splash-3 Benchmark Suite                  | 43 |

|   | 4.4 | PARSEC Benchmark Suite                    | 46 |

|   | 4.5 | Experimental Process                      | 47 |

|   | 4.6 | Experimental Results                      | 53 |

| 5 | Con | nclusion and Future Work                  | 69 |

|   | 5.1 | Conclusion                                | 69 |

|   | 5.2 | Future Work                               | 70 |

# List of Tables

| 2.1  | Example A: 1GB Memory System composed by one 1GB-x4-16Bank DIMM, Example B: 2GB Memory System composed by two 1GB-x8-16Bank DIMMs | 8  |

|------|-----------------------------------------------------------------------------------------------------------------------------------|----|

| 4.1  | The general specs table of the 3 CPUs                                                                                             | 42 |

| 4.2  | Intel Ivy Bridge i7 3770 Cache Metrics                                                                                            | 42 |

| 4.3  | Intel Skylake i 6700K Cache Metrics                                                                                               | 42 |

| 4.4  | Intel Xeon Cache Metrics                                                                                                          | 42 |

| 4.5  | DRAM Metrics - Modified DDR4 Micron 1G 16B x4 sg083E                                                                              | 43 |

| 4.6  | Barnes Native Input                                                                                                               | 45 |

| 4.7  | Volrend Native Input                                                                                                              | 46 |

| 4.8  | Raytrace Native Input                                                                                                             | 46 |

| 4.9  | FluidAnimate Native Input                                                                                                         | 47 |

| 4.10 | Barnes Utilization                                                                                                                | 49 |

| 4.11 | Raytrace Utilization                                                                                                              | 51 |

| 4.12 | Nanosecond to Memory Cycles Disaggregated Latency Correspondence                                                                  | 53 |

| 4.13 | Disaggregated Latency impact range - Ivy                                                                                          | 55 |

| 4.14 | Disaggregated Latency impact range - Skylake       | 55 |

|------|----------------------------------------------------|----|

| 4.15 | Disaggregated Latency impact range - Xeon          | 55 |

| 4.16 | Average Disaggregated Latency Impact per Benchmark | 55 |

# List of Figures

| 1.1  | Whole System Abstract Figure                                                     | 3  |

|------|----------------------------------------------------------------------------------|----|

| 2.1  | A typical PC organization and the DRAM subsystem as one part of a complex whole. | 5  |

| 2.2  | Basic organization of DRAM internals                                             | 6  |

| 2.3  | Overview of DRAMSim2                                                             | 12 |

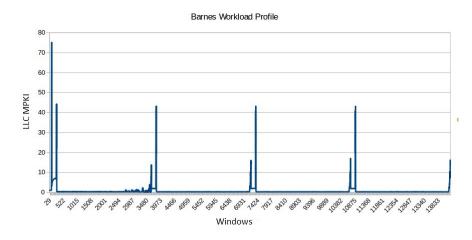

| 4.1  | Barnes Profile                                                                   | 49 |

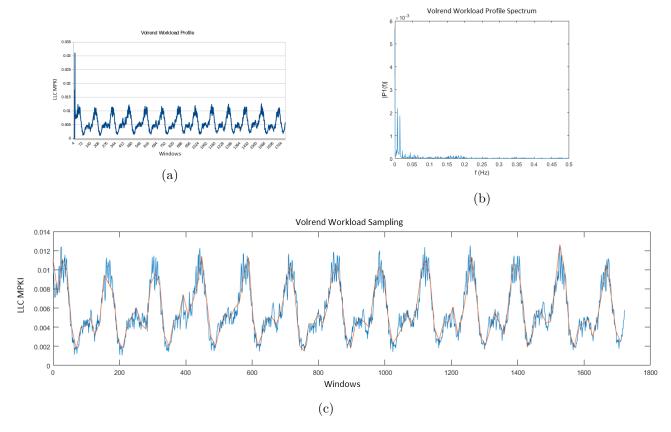

| 4.2  | Volrend Profile Sampling                                                         | 50 |

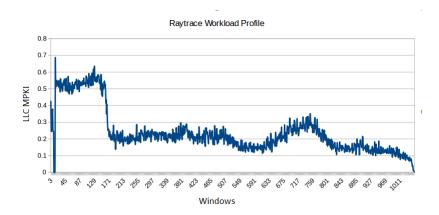

| 4.3  | Raytrace Profile                                                                 | 51 |

| 4.4  | FluidAnimate Profile                                                             | 52 |

| 4.5  | Barnes Ivy Results                                                               | 57 |

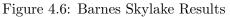

| 4.6  | Barnes Skylake Results                                                           | 58 |

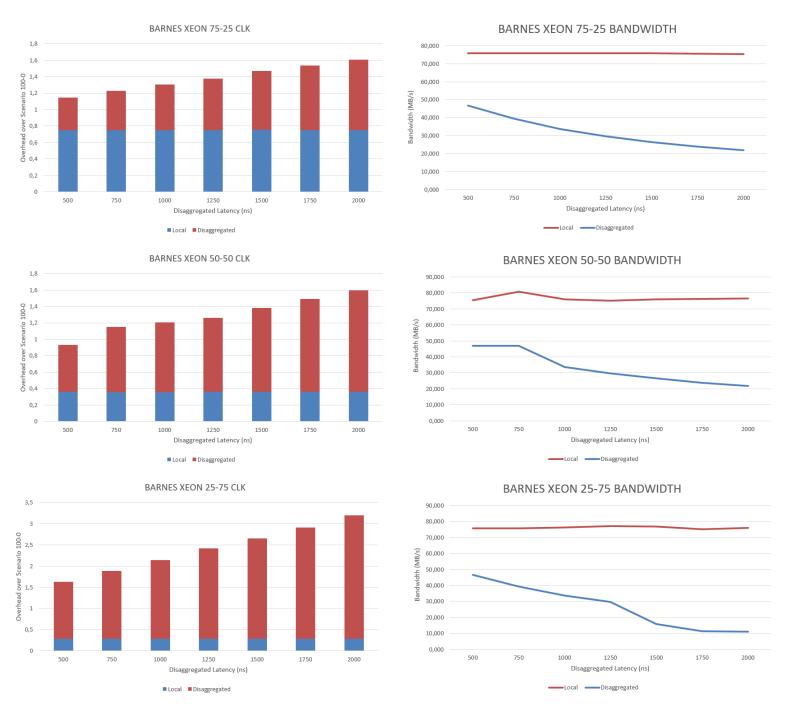

| 4.7  | Barnes Xeon Results                                                              | 59 |

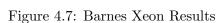

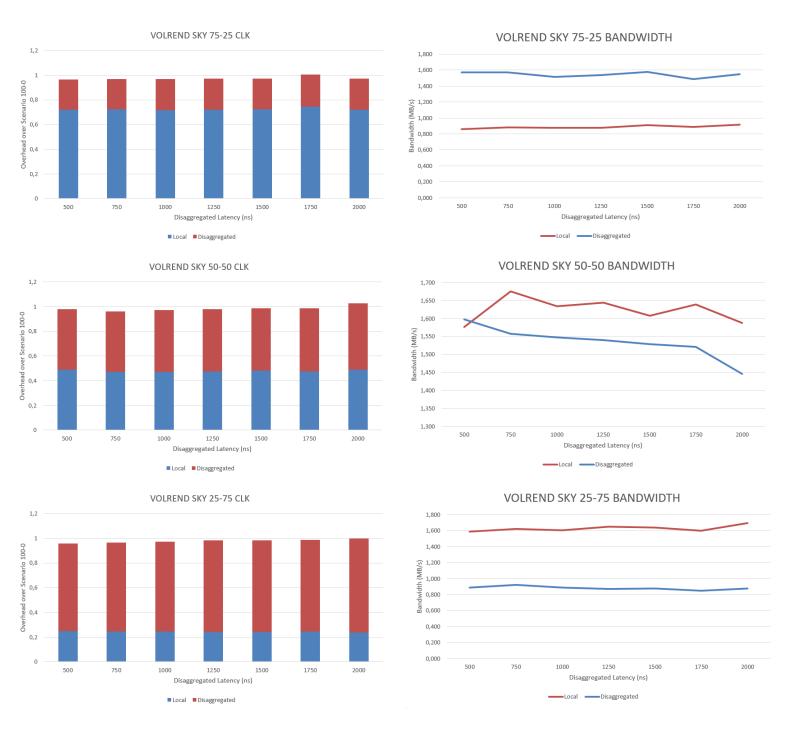

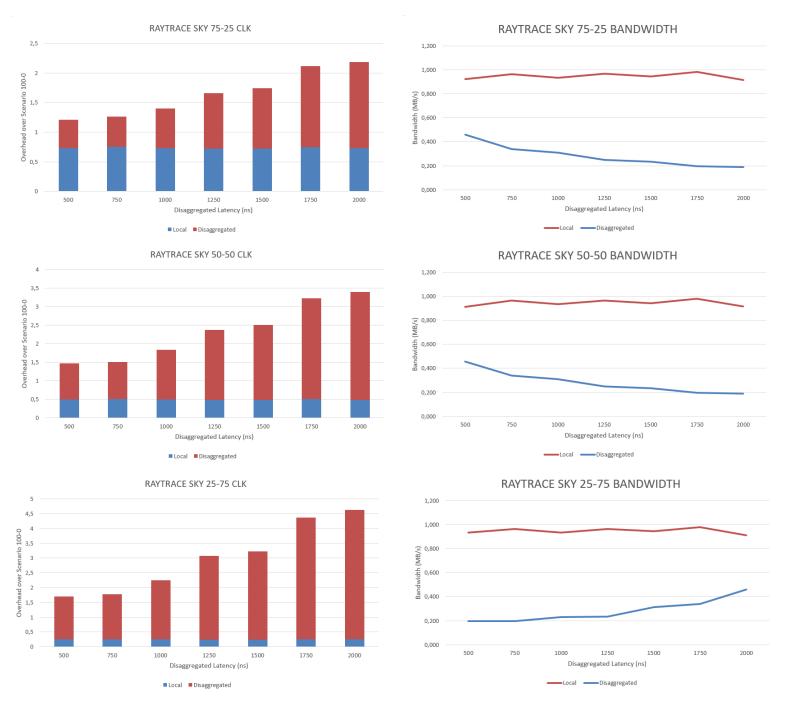

| 4.8  | Volrend Ivy Results                                                              | 60 |

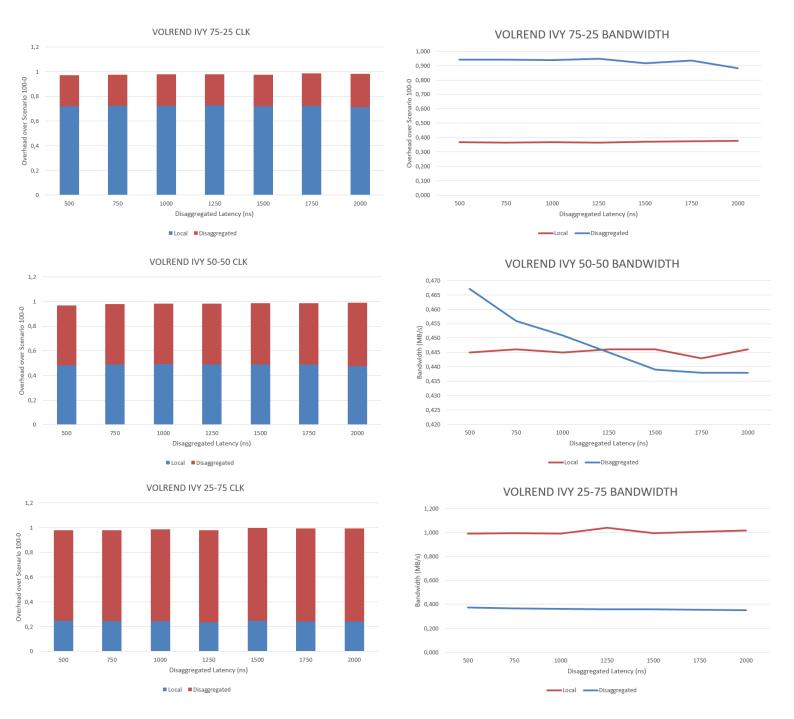

| 4.9  | Volrend Skylake Results                                                          | 61 |

| 4.10 | Volrend Xeon Results                                                             | 62 |

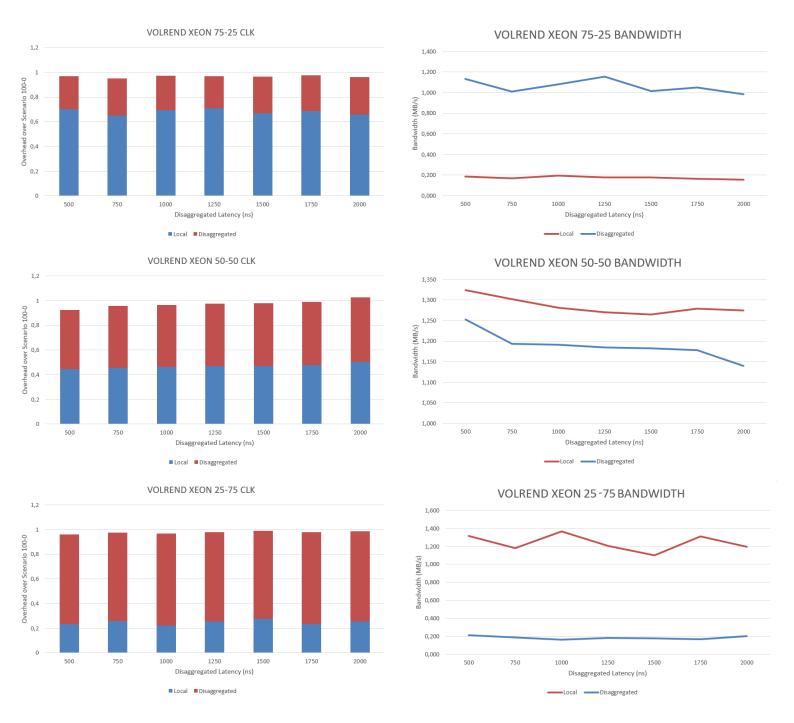

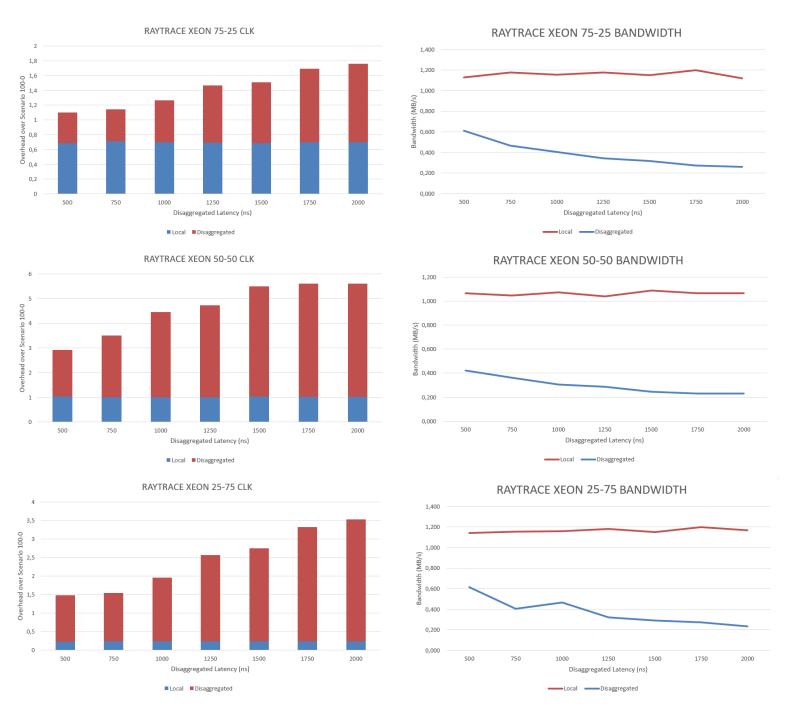

| 4.11 | Raytrace Ivy Results         | 63 |

|------|------------------------------|----|

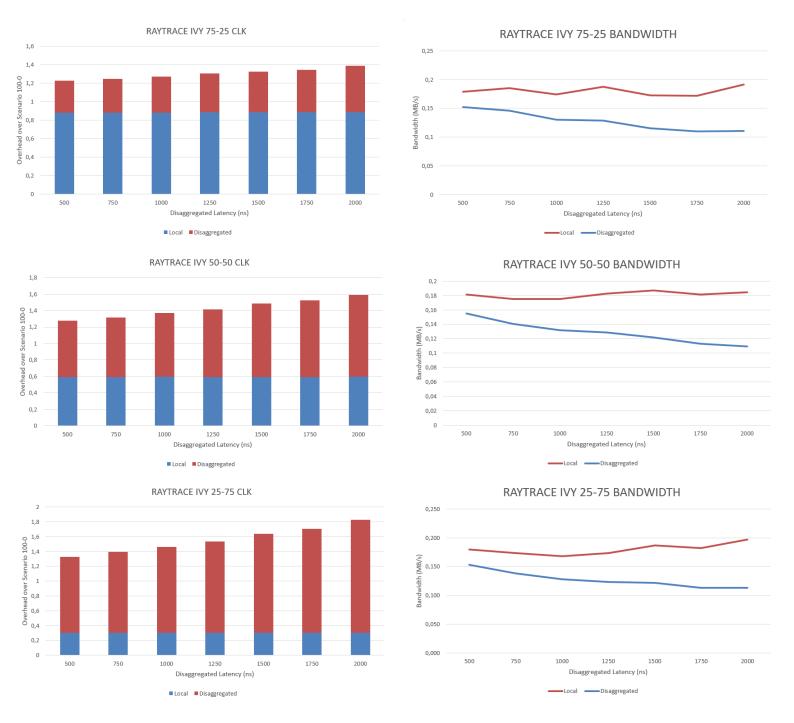

| 4.12 | Raytrace Skylake Results     | 64 |

| 4.13 | Raytrace Xeon Results        | 65 |

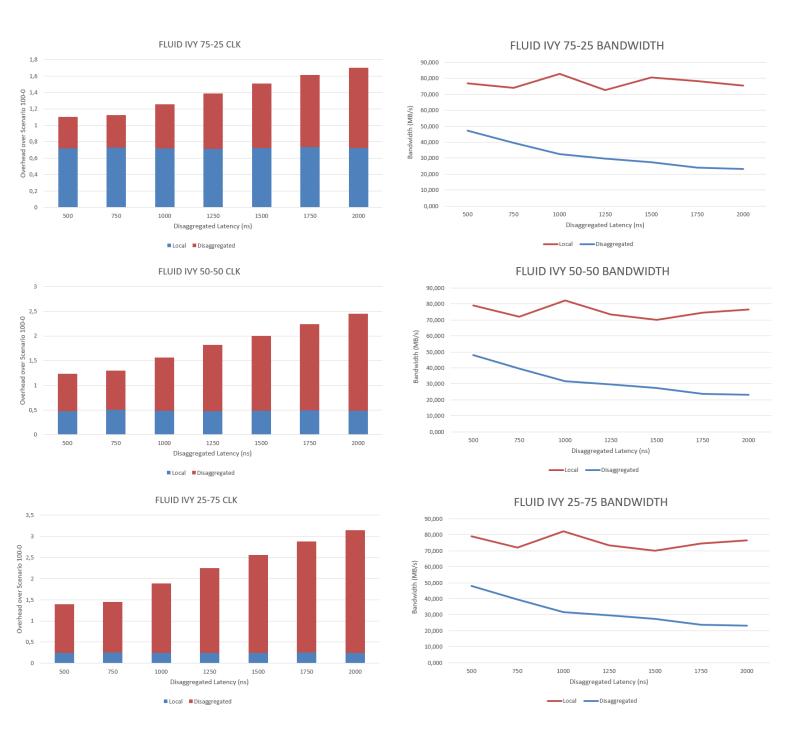

| 4.14 | FluidAnimate Ivy Results     | 66 |

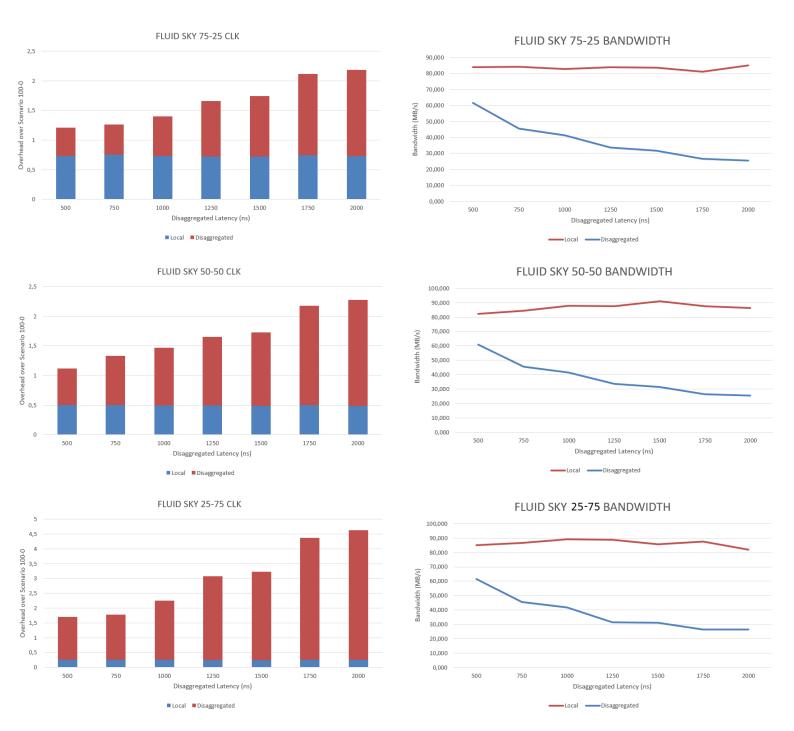

| 4.15 | FluidAnimate Skylake Results | 67 |

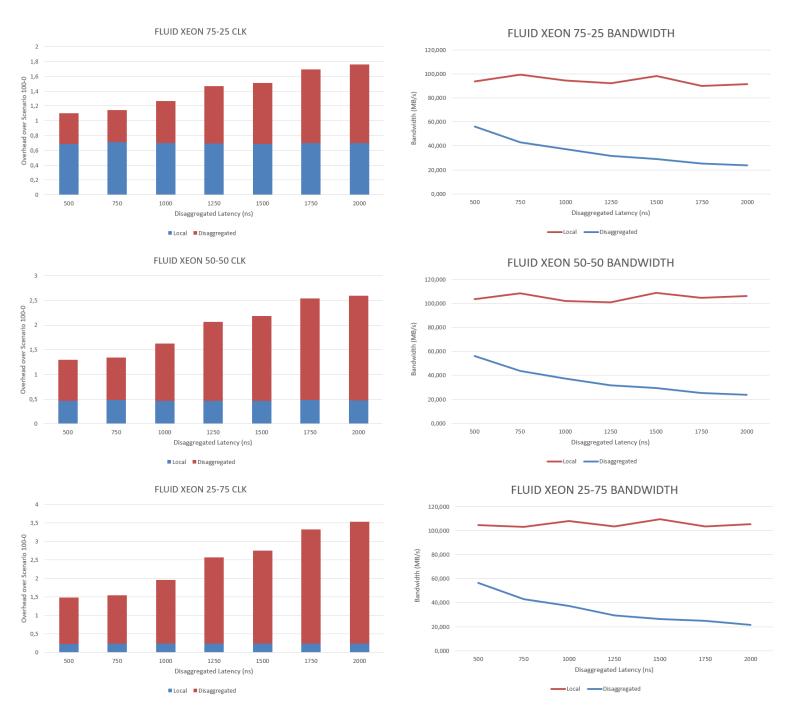

| 4.16 | FluidAnimate Xeon Results    | 68 |

# Listings

| 2.1  | MemorySystem Constructor             | 12 |

|------|--------------------------------------|----|

| 2.2  | MemorySystem Methods                 | 12 |

| 2.3  | MultiChannelMemorySystem Constructor | 13 |

| 2.4  | MultiChannelMemorySystem Methods     | 13 |

| 2.5  | Initialization Example               | 15 |

| 2.6  | before parsing                       | 17 |

| 3.1  | MultithreadCount Method              | 26 |

| 3.2  | SetMultithreadCount Method           | 27 |

| 3.3  | Analysis Function begins Simulation  | 27 |

| 3.4  | GoToSim code                         | 28 |

| 3.5  | prepareSimulation() code             | 30 |

| 3.6  | Disaggregate() code                  | 31 |

| 3.7  | Simulate() code                      | 34 |

| 3.8  | Skip Mode code                       | 36 |

| 3.9  | Pintool.out example                  | 37 |

| 3.10 | DRAMSim2.out example                 | 39 |

### Chapter 1

## Introduction

High-performance computing (HPC) or Supercomputers is the use of parallel processing for running advanced application programs efficiently, reliably and quickly. Performance of those systems is measured above a *teraflop*  $(10^{12})$  floating point operations per second. Some of them are near or at the current highest performance. For instance, the Chinese supercomputer *Sunway TaihuLight*, which is the first in the TOP500 list (June 2016) as the fastest supercomputer in the world, reaches 93 petaflops  $(10^{15})$  on the LINPACK benchmarks. Since HPC are commonly used by academic institutes, researchers and engineers, their study constitutes a crucial and traditionally continuous researching field of Computer Architecture.

Disaggregated Architecture Systems are under research by the H2020 EU project dRedBox[10], that aims to break the system resources and scalability limitations, which lead to inefficiencies, suboptimal resource availability and unexploited spare resources in current datacenters. Furthermore, it introduces a new Rack-Scale Architecture that will not require memory or accelerator to be co-located with a processor in the same node. System resources are aimed to be connected via multiple networks. High-speed and low-latency electrical network will be used for intra - tray data access in memory bricks. High-speed low-latency optical network will be used for inter - tray data memory bricks. The current thesis is trying to do an experimental evaluation of that memory inter-connection.

Before a particular design "committed to silicon", we need a way to evaluate the performance of

design alternatives quickly, accurately and costlessly. An initial assessment and exploration for the whole set of design parameters is absolutely necessary, in order to be reliable for further research and development. System Simulation is a good option for that purpose because it is cheap and easy to develop compared with a real system implementation.

The goal of the current diploma thesis is the development of a Disaggregated Memory System Simulator and its use for the evaluation of Disaggregated High Performance Parallel Systems. The DIMEM Simulator has to operate by passing all the Main Memory CPU requests to a Disaggregated Memory System model. Furthermore it must aggregates statistical results, such as CLK, Bandwidth, in order, to make the user able to evaluate the Simulation.

In Memory Simulation a software system that models and simulates Memory is needed, together with a suitable method to model the traffic of the System. The work of DIMEM Simulator is based on the DRAMSim2, a Cycle Accurate Memory System Simulator (for modelling and simulation). This way implementation of the traffic generation and passing methods to DRAMSim2 are the missing pieces of the puzzle. Intel's PIN dynamic binary instrumentation framework was chosen as the development means of a dynamic program analysis tool for memory tracing and preparing the simulation.

The tool which was created using Intel's Pin (Pintool) combines two main goals: 1)Binary Executable Memory Tracing, 2) Memory Simulation. These two goals were expanded in two discrete but interrelated Diploma Thesis. The first one has been covered by Andreas Andronikakis [9], and the second is the object of the current thesis. These two goals compose the whole Disaggregated Memory System Simulator (DiMEM), which can be used for evaluation of any type of Disaggregated Memory System.

The current Diploma Thesis focuses on the Pintool's Simulation Preparation functionality, both from theoretical and implementation point of view, so that the Pintool obtains more completesystem and useful tool characteristics than a simple Memory Tracing Pintool. The implemented features which will be described in detail in chapter 3 are:

1. Reordering, Approximate Timing and Sorting of the Multithreaded Trace

- 2. Making use of the capabilities of DRAMSim2 Cycle Accurate Memory System Simulator,

- 3. Implementation of Disaggregate Memory Behaviour

- 4. Speeding-up the Simulation with "Skip Mode" and Statistical processing of the results.

In the implementation chapter code parts are presented to help readers understanding.

High-Performance Parallel Systems are the object of Disaggregated Memory System Evaluation process which will be described in chapter 4. Segments of both Splash-3 and PARSEC Benchmark Suites have been used for evaluation.

Figure 1.1: Whole System Abstract Figure

### Chapter 2

## **Background And Related Work**

#### 2.1 Background

#### 2.1.1 DRAM Technology Overview

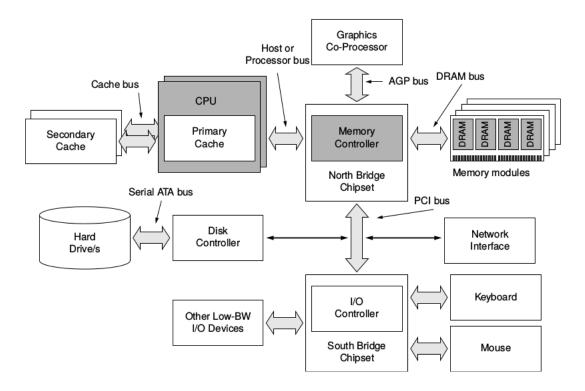

The random-access memory technology (RAM) is used for the Main Memory implementation of a Computer System. Main Memory is responsible for the majority of the needed information required during a program execution. Despite the fact that it is commonly conceived as a *box* that receives CPU requests and responses with data, Main Memory has a structure which is critical for its performance. These structural characteristics are about to be described for the purpose of understanding the evaluation approach.

#### The Basic Circuit

RAM that uses a single *transistor-capacitor pair* for each bit is called a dynamic random-access memory or DRAM. The circuit is dynamic because the capacitors storing electrons are not perfect devices, and their eventual leakage requires that, to retain information stored there, each capacitor in the DRAM must be periodically refreshed (read and rewritten).[1]

Figure 2.1: A typical PC organization and the DRAM subsystem as one part of a complex whole.

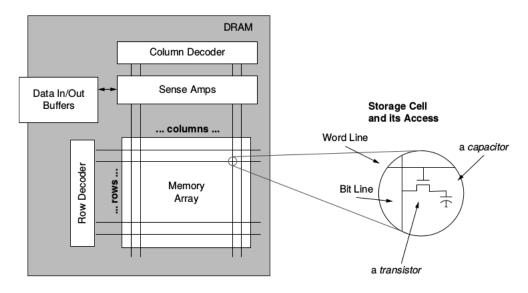

#### Memory Arrays

Each DRAM device/chip contains one or more *memory arrays*, rectangular grinds of storage cells with each cell holding one bit of data. The arrays are organized into rows and columns. The Memory Controller (MC) uses the rows and columns (row address and column address) to access a specific storage cell into the DRAM chip. In the case of more than one memory array, a DRAM chip works in several different ways: in unison, completely independently or somewhere in the middle. If the memory arrays are designed to act in unison, they work as a unit, and the memory chip transmits or receives a number of bits equal to the number of arrays (Device Density or Device Width) each time the memory controller accesses the DRAM. For example, an x4 DRAM indicates that the DRAM device has four memory arrays and that a column width is 4 bits (each column read or write transmits 4 bits of data). In an x4 DRAM part, four arrays each read 1 data bit in unison, and the part sends out 4 bits of data each time the MC makes a column read request.

Figure 2.2: Basic organization of DRAM internals.

#### **Banks and Devices**

A set of memory arrays that operates independently from other sets is referred to as a *Bank*. Each Bank is independent and can be activated, precharged, read out, etc. at the same time that other Banks (on the same or on other DRAM devices) are being activated, precharged, etc. The use of multiple independent Banks of memory has been a common practice in computer design since DRAMs were invented. One or more Banks which work in unison are organized and compose a DRAM device. As a result, interleaving multiple memory banks has been a popular method, used to achieve high-bandwidth memory buses using low-bandwidth devices.

Despite the existent confusion, among the bibliography, about the clear definition of word "Bank", it is currently used by DRAM device manufacturers to describe the number of independent *DRAM* arrays within a DRAM device [6]. For example a 16 Banks x4 DRAM Device contains 16 independent quadruple Arrays. Each quadruple Array acts independently from the 15 others, but the 4 internally contained Arrays act in parallel.

#### Ranks

As a system can have multiple DIMMs, each of which can be perceived as an independent Bank, and the DRAM devices can implement internally multiple independent Banks, the word "Rank" was introduced to distinguish DIMM-level independent operation. Each Rank is a set of DRAM devices that operates in unison, and internally each of these DRAM Devices implements one or more independent Banks. JEDEC standard defines that a Rank must have 64 bits output bus so the number of DRAM Devices in a Rank is equal to 64/Device Width. Each DIMM can contain exactly one or two Ranks.

#### **DIMM/Channel**

The Rank or Ranks compose a DIMM, or in other words a Channel. A computer's Memory System can have a single Channel, or multiple Channels. As an overview, a Channel is the collection of all DRAM Devices that share a common physical link (command, address, data buses) to the processor, and , thus, although a set of DIMMs in the Channel receives the same command, only one Rank replies. A Multi-channel system can be further divided into (1) multiple dependent (lockstep) Channels: single Memory Controller with ganged Channels to provide a wider interface; and (2) multiple independent Channels (each with its own Controller).

The number of Banks is also used as a way to characterize a whole DIMM, without considering as the total *physical* number of Banks that a whole DIMM may contains. The physical number of contained Banks = Banks per Device x Devices per Rank x Num of Ranks, but the characterization of N (=Banks per Device) Banks DIMM is used. For example a 4 GB 16 Banks x4 DRAM, physically, may not consists of 16 Banks only, but it is used to be referred as a 16 Banks DIMM from the aspect of its structure characterization.

To summarize, an example table is presented with all DRAM structural characteristics expanded:

|                   | Example A | Example B |

|-------------------|-----------|-----------|

| Total Size        | 1 GB      | 2 GB      |

| Is Multi Channel  | NO        | YES       |

| Num of DIMMS      | 1         | 2         |

| DIMM Size         | 1 GB      | 1 GB      |

| Ranks per DIMM    | 1         | 1         |

| Num of Ranks      | 1         | 2         |

| Devices per Rank  | 16        | 8         |

| Device Size       | 64 MB     | 128 MB    |

| Banks per Device  | 16        | 16        |

| Bank Size         | 4 MB      | 8 MB      |

| Arrays per Bank   | x4        | x8        |

| Array Size        | 1 MB      | 1 MB      |

| Rows (in bits)    | 128       | 128       |

| Columns (in bits) | 64        | 64        |

Table 2.1: Example A: 1GB Memory System composed by one 1GB-x4-16Bank DIMM, Example B: 2GB Memory System composed by two 1GB-x8-16Bank DIMMs

#### 2.1.2 General Simulation Techniques: Execution or Trace Driven

Let's make an overview of the memory system simulation methods and approaches so that we determine how and why a choice has been made. The most important diversifying factor, is the generation way of the memory trace because, in order to simulate the memory system behaviour and performance, a memory trace is necessary.

#### **Trace Driven Simulation Approach**

A tracing collection process is necessary so that the information about "interesting instructions" of a binary executable can be written out in file, the Trace File, as each instruction is executed. The tracing process can operate both over a real-existing Instruction Set Architecture (ISA), and over an emulated and maybe not-existing one.

The only information needing to be recorded is about the data address and the type of memory operation. Trace Files have quite a large size in general (0,5 GB per 1 Billion Memory Accesses) for real benchmark programs. After the trace production, Trace Files are passed as input, read by the Memory System Simulator and analyzed for performance study. It should be emphasized that the Simulator can run on any machine, even though on one with different ISA, because, the Memory System Simulator itself does not need to execute the ISA but only to analyze the execution history for a particular architecture being studied.

Since a Trace-based Memory System Simulator is ISA-independent, it can be used to evaluate also not existing Architectures. In addition, this technique is very useful when the execution of a program used for trace collection, is extremely slow or wasteful, due to the fact that the Trace File is generated once and can be reused, thus, saving both resources and time.

The pros and cons of the trace driven simulation method are presented below:

#### Advantages

- 1. Can run on any machine as long as trace format is known.

- 2. Simplicity and low modeling complexity. Only memory address and access type recorded.

- 3. Produced once, used many times.

- 4. Evaluation of not existing Architectures.

#### Disadvantages

- A Trace File is only a capture. May not be representative of the dynamic behavior of multithreaded applications. Special custom handling and synchronization needed, such as TaskSim-NANO++ [7].

- 2. Simplicity requires low-level of model detail. The detail lose may refer to the time accuracy, which is important for the result reliability.

- 3. Two step process.

- 4. Large disks are needed as a result of large space need to store traces.

- 5. High-speed disks are needed to avoid overhead from read/write traces to disk.

#### **Execution Driven Simulation Approach**

The Simulation follows the actual execution of a program. This can be done either with the direct execution of the program by the Memory Simulator, or with the Memory Simulator pairing with a front-end driver, which executes the program and generates the Trace. In both ways, as the Binary is executed, the trace is generated on-the-fly, so Memory Simulation is performed exactly after the execution of an Instruction. The ISA can sometimes be emulated. A timing model is also necessary for the time accuracy of the simulation. The timing model usage adds a significant overhead. The pros and cons of execution driven simulation method are presented below:

#### Advantages

- 1. Parallel behaviour can be captured.

- 2. No need to store traces.

- 3. No overhead from read/write to disk.

- 4. One step process.

#### Disadvantages

- 1. Execution-driven is ISA-depended, consequently increased development time for different architectures.

- 2. Is slower when a complex architecture is studied. (speed of the simulator is a very important issue and a complex one).

- 3. Time accuracy of the timing model adds a significant overhead to simulation time.

The Execution Driven approach can be implemented either *one-by-one*, or *in-fragments* as *send-to-simulator* rate. In one-by-one Execution Driven, a single instruction is approached separately, so *each* instruction is traced, it is also simulated. The Execution Driven in fragments approaches the simulation trace neither as a monolithic whole (Trace driven), nor per single instruction separately, but somewhere in the middle. The Trace is separated, during execution, into arbitrary sized fragments by storing them into a buffer. When a buffer is full-filled, it is sent for Simulation. The size of that buffer is arbitrary and must be specified experimentally.

#### 2.1.3 DRAMSim2 Memory Simulator Overview

#### General

DRAMSim2 is a very popular open-source cycle-accurate JEDEC DDRx Simulator which models memory controller, memory channels, ranks, banks and all timing constraints in a general way [2]. It is developed in object-oriented C++. It can be used either in *standalone* mode to simulate memory system traces, or as a dynamic shared library which is convenient for connecting it to CPU simulators (such as MARSSx86, gem5) or other custom front-ends, in order to develop a full-system simulator.

In the current thesis DRAMSim2 is approached as the "Simulation Pair" of the Instrumentation Trace Generator Pintool from the Andronikakis thesis [9]. DRAMSim2 has the goal "to be an accurate and publicly available DDR2/3 memory system model" and can be used both for tracedriven simulations and so as Library Interface for more custom-system approaches. DRAMSim2 has came to fill the previously semi-blank field of memory system simulators with a quite simple programming interface. Despite the fact that DRAMSim2 is focused on DDR2/3, the differences with the DDR4 technology are only on latency and power so it can be used also for latency and power aimed and less rigorous DDR4 simulation.

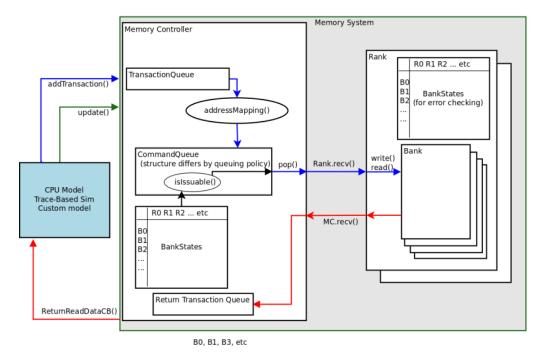

The basic component is the cycle accurate memory controller with the mission of translation and issuing DRAM commands to a memory-bus-attached set of DRAM devices. The DRAMSim2 functionality is enclosed by an easy-to-use interface, so it is easy, also, to connect DRAMSim2 with any kind of "front-end driver", for example with a cycle accurate CPU simulator such as MARSSx86 or just a trace reader etc.

Figure 2.3: Overview of DRAMSim2

#### A few words about internal functionality

The MemorySystem class is the DRAMSim2 core-module and models one channel of a Multi-Channel Memory System. So the whole system is modelled by the MultiChannelMemorySystem class.

The constructor functions and methods of those two classes are presented so that their functionality can be explained easily :

```

1 MemorySystem::MemorySystem(unsigned id, unsigned int megsOfMemory,

CSVWriter &csvOut_, ostream &dramsim_log_)

```

Listing 2.1: MemorySystem Constructor

```

1 void update();

```

2 **bool** addTransaction(Transaction \*trans);

3 **bool** addTransaction(**bool** isWrite, uint64\_t addr);

```

4 void printStats(bool finalStats);

```

5 **bool** WillAcceptTransaction();

6 void RegisterCallbacks( Callback\_t \*readDone, Callback\_t \*writeDone, void (\*reportPower (double bgpower, double burstpower, double refreshpower, double actprepower));

Listing 2.2: MemorySystem Methods

MultiChannelMemorySystem :: MultiChannelMemorySystem (const string & deviceIniFilename\_, const string &systemIniFilename\_, const string & pwd\_, const string &traceFilename\_, unsigned megsOfMemory\_, string \* visFilename\_, const IniReader :: OverrideMap \*paramOverrides)

Listing 2.3: MultiChannelMemorySystem Constructor

- 1 **bool** addTransaction(Transaction \*trans);

- 2 **bool** addTransaction(**const** Transaction &trans);

- 3 **bool** addTransaction(**bool** isWrite, uint64\_t addr);

- 4 **bool** willAcceptTransaction();

- 5 **bool** willAcceptTransaction(uint64\_t addr);

- 6 **void** update();

- 7 **void** printStats(**bool** finalStats=**false**);

- 8 ostream &getLogFile();

- 9 **void** RegisterCallbacks(

- 10 | TransactionCompleteCB \*readDone,

- 11 TransactionCompleteCB \*writeDone,

- 12 void (\*reportPower)(double bgpower, double burstpower, double

refreshpower, double actprepower));

- 13 **int** getIniBool(const std::string &field, bool \*val);

- 14 **int** getIniUint(const std::string &field, unsigned int \*val);

- 15 **int** getIniUint64 (const std::string &field, uint64\_t \*val);

16 **int** getIniFloat(const std::string &field, float \*val);

17 **void** InitOutputFiles(string tracefilename);

18 **void** setCPUClockSpeed(uint64\_t cpuClkFreqHz);

Listing 2.4: MultiChannelMemorySystem Methods

The main arguments for a MultiChannelMemorySystem object are, in essence, the Device Ini file (the MultiChannelMemorySystem constructor first argument, deviceIniFilename\_), the system ini file (the second argument, systemIniFilename\_) and the DRAM size (fifth argument, megsOfMemory). With these 3 arguments we can describe our simulated Memory System structure and characteristics.

Device Ini File defines the DIMM structural characteristics for example : DEVICE\_WIDTH, NUM\_BANKS, NUM\_ROWS, NUM\_COLS and many *non-structural* characteristics such as : REFRESH\_PERIOD, tCK, ,, Vdd etc.

System Ini File defines the Memory Controller characteristics, for example : JEDEC\_DATA\_BUS\_BITS, TRANS\_QUEUE\_DEPTH, CMD\_QUEUE\_DEPTH, SCHEDULING\_POLICY, QUEUING\_STRUCTURE etc. It also sets the debugging flags of DRAMSim2.

MultiChannelMemorySystem is the DRAM system composed of one or more channels (MemorySystem). Each channel contains multiple ranks and each rank has several banks. Furthermore, each channel has a pendingTransactionQueue. In addition, there is one corresponding memory controller for each channel.

The memory controller has four queues:

- 1. the Transaction Queue (TransQ) which receives and stores incoming transactions,

- 2. the Command Queue (CmdQ) which stores the translated commands of each transaction.

- 3. If a read command is dispatched to the memory, then the transaction will be stored into the *Pending Read Transaction Queue* (PendRTQ) until the data is returned.

- 4. Finally the Return Transaction Queue (RtnQ) is for storing the returned transactions.

#### Initialization

The first step is the creation of a new MultiChannelMemorySystem object by calling the constructor (listed in figure 2.3) with the appropriate arguments and Ini files described above. The getMemorySystemInstance() function can be called alternatively. That function is implemented in MultiChannelMemorySystem class and gets exactly the same arguments as the original Constructor function. Its task is the MultiChannelMemorySystem Constructor call. After that, the *Callback Functions* must be registered so as to be executed when a read or write request is completed. A simple example of initialization follows.

```

void main(){

1

\mathbf{2}

. . .

3

MultiChannelMemorySystem *mem = getMemorySystemInstance( arg1, ...);

TransactionCompleteCB *read_cb = new Callback< /* args*/ >(&obj, &

4

some_object :: read_complete);

5

TransactionCompleteCB *write_cb = new Callback< /*args*/ >(&obj, &

some_object :: write_complete);

\mathbf{6}

7

mem->RegisterCallbacks(read_cb, write_cb);

8

. . .

9

/*

Simulation code can follows

10

11

*/

12

}

```

Listing 2.5: Initialization Example

#### Simulation

A function must be called for every MemorySystem clock tick and also a function to queue the memory requests. After the completion of a memory request, DRAMSim2 calls the provided callback function to inform the front-end for the completed request. The process of Simulation can be described like this: CPU requests are buffered into the TransQ in execution order, then they are translated into DRAM commands and placed into the CmdQ which can have *per rank* or *per rank per bank* structure. The memory controller takes into consideration the state of every memory bank, the read/write dependencies and the timing constraints to decide the next issue request. Due to that decision, the memory controler is, also, free to issue out-of-order. The out-of-order issuing helps to increase bank usage and bandwidth and also latency lowering. After a completed transaction, the bandwidth and latency are kept. An average calculation is performed over a given *epoch* defined in Device Ini File.

#### **Refresh Modelling**

Another simulation issue is the DRAM refresh. Modelling refresh is necessary because the refresh induces differentiation in the memory requests latency. If a request is issued during a DRAM refresh, it will have to wait much longer than other requests. That latency elongation can impose significant performance penalties for processors in wait for memory accesses and as a result, they significantly affect the whole system performance.

#### Power Model

Another DRAMSim2 feature is the power calculation based on the power model described in [8]. The DRAMSim2 power calculation adapts to any DDR model. The power consumption is calculated per Bank. The calculation is based in the Bank's activity where each action, or state, corresponds to a specific amount of power. That correspondence is a result of many power equations which model the DDR DRAMS and also described in [8]. This model and calculations follow in a strictly way theoretical equations and can be considered as accurate, despite any real world deviations.

#### **DRAMSim2** Inputs

#### Memory Trace

The Trace either as a Trace File, or as an execution driven process is the main input source of DRAMSim2. In the standalone mode the Trace is a .trc file, the Trace File, with 3 columns: Memory Address, Transaction Type (P\_MEM\_WR, P\_MEM\_RD, P\_FETCH) and Cycle. In case of a front-end driver which produces Trace File timed in nano seconds, it must be preprocessed with a python parse script (comes with DRAMSim2 package) in order to be mapped to cycles.

For example:

| 0x018ADB20 | P_MEM_WR | $0  \mathrm{ps}$ | 0x018ADB20 P_MEM_WR | 0 |  |

|------------|----------|------------------|---------------------|---|--|

| 0x018ADB28 | P_MEM_WR | 10.000 ns        | 0x018ADB28 P_MEM_WR | 1 |  |

| 0x01A5DB58 | P_FETCH  | 50.000 ns        | 0x01A5DB58 P_FETCH  | 5 |  |

| 0x01A5DB50 | P_MEM_RD | 60.000 ns        | 0x01A5DB50 P_MEM_RD | 6 |  |

| 0x01A5DB48 | P_FETCH  | 70.000 ns        | 0x01A5DB48 P_FETCH  | 7 |  |

|            |          |                  |                     |   |  |

Listing 2.6: before parsing

Listing 2.7: after parsing

When used as a library interface, a simple and easy-to-use API is provided, in order to pass the transactions in a custom way. The function must be used to pass a Transaction to DRAMSim2 is the addTransaction, in listing 2.4.

#### System Ini File

The System Ini (system.ini) file contains the Memory System and Memory Controller parameters. They are presented below:

| NUM_CHANS           | ADDRESS_MAPPING_SCHEME |

|---------------------|------------------------|

| NUM_RANKS           | SCHEDULING_POLICY      |

| JEDEC_DATA_BUS_BITS | QUEUING_STRUCTURE      |

| TRANS_QUEUE_DEPTH   | VIS_FILE_OUTPUT        |

| CMD_QUEUE_DEPTH     | USE_LOW_POWER          |

| EPOCH_LENGTH        | VERIFICATION_OUTPUT    |

| ROW_BUFFER_POLICY   | TOTAL_ROW_ACCESSES     |

Some debugging flags also exist.

#### Device Ini File

The Device Ini file (DRAMmodel.ini) contains all the DRAM model structural parameters such as banks, rows, columns, clock, other timing and all power parameters, as well. The most important of them are presented below:

| DRAM Device Structural parameters                                               |                                                                            |  |  |

|---------------------------------------------------------------------------------|----------------------------------------------------------------------------|--|--|

| NUM_BANKS         number of banks                                               |                                                                            |  |  |

| NUM_ROWS                                                                        | number of array rows                                                       |  |  |

| NUM_COLS                                                                        | number of array columns                                                    |  |  |

| DEVICE_WIDTH                                                                    | number of arrays per device (eg x16)                                       |  |  |

| REFRESH_PERIOD (in ns)                                                          |                                                                            |  |  |

| The four Latency parameters $CL$ - $t_{RCD}$ - $t_{RP}$ - $t_{RAS}$ (in cycles) |                                                                            |  |  |

| CL                                                                              | <b>CAS latency</b> : the number of cycles between sending a column address |  |  |

|                                                                                 | to the memory and the beginning of the data in response                    |  |  |

| $t_{RCD}$                                                                       | Row Address to Column Address Delay: The minimum number                    |  |  |

|                                                                                 | of clock cycles required between opening a row of memory and accessing     |  |  |

|                                                                                 | columns within it.                                                         |  |  |

| $t_{RP}$                                                                        | Row Precharge Time: The minimum number of clock cycles required            |  |  |

|                                                                                 | between issuing the precharge command and opening the next row.            |  |  |

| $t_{RAS}$                                                                       | Row Active Time: The minimum number of clock cycles required               |  |  |

|                                                                                 | between a row active command and issuing the precharge command.            |  |  |

The parameters also include all other timing, latency and power constraints. It must be noted that other structural characteristics such as Ranks, Number of Devices per Rank etc are not defined directly, but are calculated internally. The Device ini file defines the 4 *strategic* structural characteristics that describe directly only the DRAM Device. The Total Storage is defined as an argument in the MultiChannelMemorySystem Object Constructor (listing 2.3) and can be considered as the second part of the equation that calculates the remaining structural characteristics.

DRAMSim2 computes internally PER\_DEVICE\_STORAGE, NUM\_DEVICES, and PER\_RANK\_STORAGE while all the other parameters are set by the Device Ini file.

- 1. PER\_DEVICE\_STORAGE = NUM\_ROWS \* NUM\_COLS \* DEVICE\_WIDTH \* NUM\_BANKS (in bits)

- 2. A rank "must" have a 64 bit output bus according to the JEDEC standard, so each rank must have: NUM\_DEVICES\_PER\_RANK = 64 / DEVICE\_WIDTH. If multiple channels are ganged together, the bus width is NUM\_CHANS \* 64/DEVICE\_WIDTH

- 3. PER\_RANK\_STORAGE = PER\_DEVICE\_STORAGE \* NUM\_DEVICES\_PER\_RANK = NUM\_ROWS \* NUM\_COLS \* NUM\_BANKS \* 64

- 4. MultiChannelMemorySystem object gives Total Storage in Mega Bytes so NUM\_RANKS = (TOTAL\_STORAGE/8) / PER\_RANK\_STORAGE

The only way this could run into problems is if  $TOTAL_STORAGE < PER_RANK_STORAGE$ . In that case DRAMSim2 sets NUM\_RANKS = 1 and continues.

Due to that fact, it is clear that both total storage and DRAM structural parameters must be selected carefully, so that the user can be able to control the Simulation.

#### DRAMSim2 Output

Also the simulator outputs in detail, per epoch, the bandwidth, latency and power statistics to a log file. The whole output format depends on which debug flags have been set on or off.

#### 2.1.4 Disaggregated Systems

The Rack-scale Disaggregated Systems is new Data Center approach, that aspires to change the traditional design, organization and building of data centers, proposing the deployment of pooled, disaggregated resources rather than "monolithic and tightly integrated components".

The Architecture of a server is traditionally organized in trays with a specific number of processors, memory size etc. Furthermore, due to their co-existence in the same node, they consist a monolithic and tightly coupled whole. The cloud or hyperscale computing servers, typically accommodate a large set of interconnected racks, each utilizing multiple interconnected server trays, as depicted in the figure above.

In general, a server tray consists of -typically multiple- CPUs attached via one or multiple Memory Controllers to tray-local Random Access Memory (RAM) for rapid instruction read and fast, random read/write byte-level access to data. The CPUs can also access persistent local storage and I/O devices (e.g. flash storage, accelerators) using a single or an hierarchy of I/O bridges.

At the same time, current Datacenter scale-out workloads mostly perform parallel tasks (e.g. internet search) that require access to vast amounts of data, but the traditional approach introduces limitations in terms of available system resources and scalability, leading to inefficiencies, suboptimal resource availability and unexploited spare resources in current datacenters.

To surmount these inefficiencies, the disaggregated architecture aims not to require memory or accelerator to be co-located with the processor in the same node. This will enhance

- 1. elasticity,

- 2. improvement of virtual machine migration, and

- 3. reduction of the Total Cost of Ownership (TCO)

in comparison to the current servers. In this new architecture the main building block is not the server, but the brick or dBRICK. The term brick refers to that new main building block unit in Disaggregated Architecture, which may be designed in different kinds, like compute, memory and peripheral bricks. To build a server based on Disaggregated architecture requires, in addition, many new breakthrough developments in network, memory interface, hyper visor and orchestration layer.

For example, the network should provide ultra-low latency and high bandwidth to, efficiently, interconnect disaggregated components in the datacenter. Regarding memory, interfaces should be transparent to application. Remote-Disaggregated memory should require no changes in current applications and because of that it should be accessed as if it is local memory in today's systems.

A Disaggregated Data Center composed of computational, memory and general purpose block units.

The memory units, are the key for disaggregation. They are aimed to provide a large and flexible pool of memory resources which can be partitioned and (re)distributed among all processing nodes (and corresponding VMs) in the system. The memory units can support multiple links. These links can be used to provide more aggregate bandwidth, or can be partitioned by the orchestrator and assigned to different computational units, depending on the resource allocation policy used. This functionality can be used in two ways. First, the nodes can share the memory space of the memory unit, implementing essentially a shared memory block (albeit shared among a limited number of nodes). Second, the orchestrator can also partition the memory of the memory unit, creating private "partitions" for each client. This functionality allows for finer-grained memory allocation.

Due to the fact that DDR4 memory modules were selected for dRedBox research and development, the same memory is used in the current thesis.

#### 2.2 Related Work

Memory Simulator is a topic with large body of prior work. Many approaches have been made either from the DRAM simulation aspect (Ramulator[19], DrSIM[4]), or from Memory Controller point-of-view to play a vital role on exploration of future Memory Architectures ([3]).

Ramulator as the current latest cycle-accurate DRAM simulator bears lots of improvements. Its initial idea relies on the observation that a DRAM can be abstracted as a state-machine hierarchy, with the DRAM standard dictating each state-machine behavior. It was build from scratch and supports all the latest DRAM standards (DDR3-4,LPDDR3/4, GDDR5, WIO1/2, HBM, as well as some academic proposals (SALP, AL-DRAM, TL-DRAM, RowClone, and SARP). Finally does not sacrifice simulation speed to gain extensibility while is 2.5x faster than the next fastest simulator

The Memory Controller focused design, generally, is an alternative approach for Memory Simulation. The [3] work uses that principle to build a high-performance event-based model offering 7x simulation speed improvement without accuracy and detail level loss. That work presents a highlevel memory controller model, specifically designed for full-system exploration of future system architectures. Due to the fact that is controller-focused, a DRAM memory model it is needed.

Gem5 simulator is a popular Full System Simulator containing many features, such as: Multiple CPU models, GPU model, Event-driven memory system, Multiple ISA support (Alpha, ARM, SPARC, x86) and Power and energy modeling. Regarding to the Memory Simulation using Gem5, two different memory system models are included: Classic(ast and easily configurable) and Ruby(flexible infrastructure, accurate simulation). Gem5 can play both the role of the Memory Simulator [3], or the Memory Simulator's front-end driver [2].

Due to the reason that the Intel PIN framework had already been chosen as the Simulator's frontend driver, Gem5 was not an option. Ramulator had not been released so far, so, the choice of DRAMSim2 as the memory simulation back-end was one-way. Except from that, the PIN-DRAMSim2 coupling was a contribution, since that match hadn't already been approached.

Regarding to the Last Level Cache Misses profiling, there are many already implemented tools doing so, like Cachegrind[16], OProfile[17] and perf[18]. However it was chosen the implementfrom-the-scratch option using Intel Pin framework, to explore also other aspects as well.

### Chapter 3

## **DIMEM Simulator: Overall Approach**

#### 3.1 Binary Instrumentation

In order to simulate and evaluate a memory system, except for a memory simulator, the existence of a *trace generator* or a *front-end driver* to cover the simulation traffic/input needs is also necessary. The trace generator is a software system that, as first step, produces, once, an experimental memory trace written in a Trace File, based on a real-world workload. After that, the Trace File can be used, more than once, as input in a memory simulator. The front-end driver can be a software system, also, that, for example, during a benchmark execution, takes the control of the execution and also "drives" the memory simulation. The term "drives" refers to the behavior of the front-end to correspond the memory simulation with real-time CPU-to-memory-requests following a memory trace produced on the fly (or -in other words- during execution).

For the DIMEM Simulator the pairing of a front-end driver with the DRAMSim2 memory simulator it was chosen. The development of a *Pintool* was chosen as the front-end driver. A Pintool is a program created by using Intel's PIN framework and describes how PIN will *Instrument* a specific binary executable.

The developed Pintool has the task to Instrument a binary executable to collect the memory trace of Main-Memory-only effective addresses. The memory trace is intended to *drive* the DRAMSim2 memory simulator during execution time. In a semi-parallel way, the Pintool instruments the executable until it reaches an arbitrary user-defined instructions amount, the Window, and then the collected trace is prepared to be sent for simulation to DRAMSim2. After simulation is completed, the Pintool continues that procedure iteratively until the binary execution ends.

A few more details: the Pintool gets the execution control of a binary executable program, so that it can be able to apply the *Instrumentation* and the *Analysis Functions*. The Instrumentation function is responsible to inject the instrumentation code in the binary. The Analysis function is the injected code, thus, it contains the, actually, instrumentation code.

The Pintool instruments using *per Instruction* Granularity and calls an Analysis Function when an instruction is or includes a Read or Write Operation. That is, in summary, the functionality of Instrumentation Function.

The Analysis Functions, are consequently, called when a Read or Write Operation is found. Then it is filtered through a Cache Model to decide if the Operation actually affects Main Memory. Finally, every instruction that affects Main Memory, is recorded to the Record Buffer (RB). The RB is processed in the next steps, before Simulation, for Simulation preparatory reasons. The RB reordering, approximate timing and sorting, according to the (possible) multithreading nature of the Instrumented binary executable, is the main object of the current thesis implementation.

The current thesis work has also to do with the second task of the Pintool, Simulation preparatory process and Memory System Simulation exploiting DRAMSim2. The implementation description uses code quotes to be more descriptive.

#### 3.2 Memory Simulation

The implementation of simulation process of DIMEM Simulator is the main goal of the current thesis. We have already talked about the pairing of the front-end driver (Pintool) with a Memory System Simulator (DRAMSim2). In the previous section we gave a brief description of the Pintool. The object of the current section is to explain more technical details about the Memory System Simulation, the way that the capabilities of DRAMSim2 Cycle Accurate Memory System Simulator were exploited, the implemented techniques for reordering, approximate timing and sorting, the techniques for maintenance the multithreaded nature of the trace and the simulation speed-up technique.

At the current thesis the memory system simulator was based on the "execution driven" method because of the advantages 1, 2 and 3 of the execution driven. Also, the "in pieces" simulation rate was chosen. So the rate was named Window and the whole technique "Reordering Window Technique".

#### 3.2.1 The Reordering Window Technique

As Reordering Window Technique referred the way, or the rate, the collected Memory Trace is passed to the Memory Simulator. The Reordering Window Technique relies on the simulation choices have been made. This technique can be described as an hybrid of the trace and execution driven also. As first priority was the fact that Instrumentation and Simulation chosen to pair as a whole and not as a "two discrete steps" process. That choice was made because of the aim of DRAMSim2 paired with a Pintool study. So, the choice of the simple Trace File generation was rejected consequently, the trace cannot be passed to memory simulator as a Trace File, and a Buffer must be used. As mentioned above, that buffer is called RB. The RB keeps instances of Main Memory Access Record structure (MMAR), a structure to store a single instrumented instruction that affects Main Memory. An MMAR stored to RB can be passed to simulator at any time. Our choice was to be passed in fragments after a constant size of instrumented instructions.

These constant size fragments named *Windows*. The Window Size is given as an input to the Pintool and is totally experimental.

After that, because of execution-driven gained ground, it had to be a choice about the timing model. Another priority was the speed of the system in a good trade-off with the accuracy. In order to decide about the timing model with those two factors (speed and accuracy) it was proceed the choice of implementation of a simple and quite approximately timing technique, based on the additive cache latency and penalties. With that choice it is avoided the large timing model overhead. Despite that, an approximate timing exists -for sure better than no timing-. The timing was also necessary due to another priority: the goal of multithreaded applications simulation. If the technique is not able to perform an, at least, approximate timing, it is also unable to simulate the multithreaded behavior and affection to the memory system. To summarize, the technique is an hybrid because in the side of trace generation it is not produce a Trace File, but a more dynamically generated Trace in a Buffer through a one step process, so is much closer to executiondriven. In the other side, of memory simulation, the produced trace is not using a detailed cycle accurate timing but an approximately one, so, in spite of the trace generation, from the timing perspective is much closer to trace-driven. With these characteristics, at the end of the day, we know that the reordering window technique is not the "best of all", because does not provide a true intreleaving of requests, but is the one that suits to our goals and needs: fast one-step simulation with multithreaded (at least approximate) timing capability.

#### 3.2.2 Preparation of Simulation

As noted in a previous section, Window Size (INS\_LIMIT) is a critical parameter of Simulation and represents the number of instructions must *pinned* before a Memory Simulation. It is noted that, the Pintool instruments until the count of *pinned* instructions equals to Window Size. It is important how the already pinned instructions are counted so that, the Pintool know when to pause instrumentation, and call Simulation functions. To count the number of Instrumented instructions it is used an ICOUNT class object of the INSTLIB namespace. The ICOUNT class is already implemented in Intel Pin's icount.H header file. The ICOUNT class is an independent instrumentation tool for counting Instrumented instructions and can be used with other Pintools. Because ICOUNT calculates the count for one thread, it was implemented a new method of ICOUNT class, named *MultithreadCount()*, which returns the total number of instructions already executed by every running thread. The code follows below:

```

1 UINT64 MultithreadCount() const

2 {

3 UINT64 multithreadCount = 0;

4 ASSERTX(Mode() == ModeBoth);

5 for(UINT64 i=0; i<ISIMPOINT_MAX_THREADS; i++)</pre>

```

Listing 3.1: MultithreadCount Method

The implementation of that method was based on the already implemented method Count() which calculated the count for the caller thread only. Also it should be noted that it was implemented and another method, named SetMultithreadCount() for the purpose of initialization to 0 the Count. In that case, as previously, the implementation was based on the already implemented method SetCount() which was also designed for single thread applications. The code follows below:

```

VOID SetMultithreadCount(UINT64 count)

1

\mathbf{2}

{

3

ASSERTX(\_mode != ModeInactive);

4

for (UINT64 i=0; i < ISIMPOINT_MAX_THREADS; i++)

5

{

_{-}stats [i]. count = count;

6

7

_stats [i].repDuplicateCount = 0;

8

}

9

}

```

Listing 3.2: SetMultithreadCount Method

As soon as the number of *pinned* instructions reaches the defined Window Size (INS\_LIMIT), the Simulation process begins.

```

//window size is arbitrary defined

#define INS_LIMIT 50000000

...

...

```

```

5

LOCALFUN UINT32 PinAnalysisFunction()

\mathbf{6}

{

7

//get the instruction count so far

UINT32 c = icount.MultithreadCount();

8

9

//some analysis code

10

. . .

11

. . .

//if window size is reached go to simulation

12

if(c \ge INS_LIMIT)

13

14

{

ins\_count = ins\_count + c;

15

GoToSim(threadid, c);

16

icount.SetMultithreadCount(0);

17

18

\operatorname{ram_count} = 0;

19

}

20

}

```

Listing 3.3: Analysis Function begins Simulation

The function called by the Pin Analysis function to perform the Simulation is, at line 16, the GoToSim() function. That function is responsible for two discrete jobs which are implemented in the *prepareSimulation()* and the *Disaggregate()* functions. It was considered useful about these two discrete jobs to implemented as two discrete functions also, for structure programming reasons. It was estimated, likewise, that the task of calling the two functions had to be assigned in an also new/discrete function. So the GoToSim() function has a unifying role of the two discrete jobs that compose the Simulation process.

4 ...

5 prepareSimulation();

6 Disaggregate();

7 //some more helping code

8 ....

9 return ;

10 }

Listing 3.4: GoToSim code

#### The prepareSimulation() function

The role of that function is to perform the necessary transformation to the RB (Trace Buffer) so that to be in the appropriate form for the simulation. The RB is a *multi*-dimensional Vector, one dimension per CPU core, and contains MMARs (Records of Instructions that affect Main Memory). The *prepareSimulation()* function performs a loop to access the RB by CPU core order. For each MMAR, calculates the *Issue-to-Memory Cycle* and then stores the Record to a new (one dimensional) Buffer named Trace Buffer (TB). The Issue-to-Memory Cycle of an Instruction (that term refers to the cycle that this instruction is going reach the Memory System and create a request) is the Issue-to-Memory Cycle of the previous Instruction from the *same* CPU core plus the current Instruction Penalty (latency).

$\operatorname{rec}[\operatorname{is}].\operatorname{cycle} = \operatorname{rec}[\operatorname{is}-1].\operatorname{cycle} + \operatorname{rec}[\operatorname{is}].\operatorname{penalty};$

After all MMARs are stored to TB, their order is not chronologically correct, so the next step is sorting by the calculated Cycle. The Sorting result is the actual Memory Trace, stored in TB, with approximate chronological order and timing, so it is ready to be Simulated. The chronological order is the sorting by Cycle result, so due to the fact that the Cycle was calculated approximately, the whole chronological order is also approximately. As a resume of the *prepareSimulation()* function we can say that receives the Instrumentation output, stored in RB, and transforms it to an approximately chronological ordered and timed Memory Trace, stored in TB, ready to be Simulated.

```

1

LOCALFUN VOID prepareSimulation()

\mathbf{2}

{

3

PIN_MutexLock(&Mutex);

for (std::size_t cores=0;cores<coreNUM;cores++)

4

{

5

for (std::size_t i=0; i < j [cores]; is++, i++)

6

{

7

/* store to TB(rec) and calculate cycle - recs=RB */

8

9

rec.push_back(Record());

\operatorname{rec}[\operatorname{is}] = \operatorname{recs}[\operatorname{cores}][\operatorname{i}];

10

rec[is].threadid = recs[cores][i].threadid;

11

12

\operatorname{rec}[\operatorname{is}].\operatorname{ip} = \operatorname{recs}[\operatorname{cores}][\operatorname{i}].\operatorname{ip};

\operatorname{rec}[\operatorname{is}].r = \operatorname{recs}[\operatorname{cores}][\operatorname{i}].r;

13

14

rec[is].penalty = recs[cores][i].penalty;

if (i==0)

15

rec[is].cycle = 0;

16

else

17

\operatorname{rec}[\operatorname{is}].\operatorname{cycle} = \operatorname{rec}[\operatorname{is}-1].\operatorname{cycle} + \operatorname{rec}[\operatorname{is}-1].\operatorname{penalty};

18

rec[is].cacheFlag = recs[cores][i].cacheFlag;

19

20

}

}

21

/* sorting by cycle */

22

std::sort(rec.begin(), rec.end(), less_than_cycle());

23

PIN_MutexUnlock(&Mutex);

24

25

}

```

#### Listing 3.5: prepareSimulation() code

The Penalty value is the additive penalty/latency of the cache hits between the current and the previous Recorded Instruction of the same CPU core.

#### The Disaggregate() function

At this point the Memory Trace is ready to be simulated. For every Instruction, firstly the Disaggregate() function is called, that decides which Memory System Model will simulate the instruction, the Local or the Remote-Disaggregated. Subsequently calls the Simulate() function with the Instruction as an attribute. In other words, the Disaggregate() function splits the Instructions through a *percentage* condition.

```

LOCALFUN VOID Disaggregate()

1

\mathbf{2}

{

3

PIN_MutexLock(&Mutex);

for (std::size_t i=0; i < rec.size(); i++)

4

5

{

6

if (i \% 101 < DISAGGREGATE_PERCENTAGE)

Simulate (dis_mem, i, DISAGGREGATED_LATENCY);

7

8

else

Simulate(mem, i, 0);

9

}

10

11

PIN_MutexUnlock(&Mutex);

12

}

```

Listing 3.6: Disaggregate() code

#### 3.2.3 Memory Simulation: Calling DRAMSim2

As already noted, in the current thesis, DRAMSim2 is used as an internal library interface. At the main() function of the Pintool, DRAMSim2 is initialized. The initialization registers the Callbacks of the Read, Write and everything else functions needed to be executed when a Transaction completes. These Callbacks are registered to one (or more) simulated Memory System objects, modelled by the MultiChannelMemorySystem class. In this implementation are used two discrete simulated Memory System objects, in respect with the Simulation and Evaluation of Disaggregated Memory System approach. DRAMSim2 implementation gives the ability of simulation more than one independent Memory Systems, which may also modelled by different Device ini file. For example the first may use a x16 DDR2 and the second a x8 DDR3 etc. Each simulated Memory System produces its own output log file also. The approach of the current thesis focus more on DDR4 DRAM models, because the whole vision of Disaggregated Memory Systems will be based on the nowadays, or even future, Memory System technologies. This topic will be discussed in detail in the Evaluation and Experimental Results Chapters.

With regard to the implementation, are used two discrete Memory Systems. The first named DIMEMmem, and models the Local Main Memory Module. The other named DIMEMdis\_mem, and models the Remote (or Disaggregated) Main Memory Module. When DRAMSim2 is used as a library interface, the front end driver is responsible for the time-correct passing of the input for simulation. For example, if the time between two instructions is 10 clock cycles, after the passing of the first, the front-end driver must not give the next instruction until 10 clock cycles of the memory system pass. For that purpose is the *Cycle* field, that was kept in the Instruction Record and calculated in prepareSimulation(). Cycle embodies the cache latency of the refereed instruction, and also the additive cache latency of the discarded instructions that not affect Main Memory. Using that calculation we are able to support that an approximate instruction timing is actually used, which drives the DRAMSim2 traffic.

For example we suppose the following instruction sequence:

| Core 0 |      | Core 1 |      |

|--------|------|--------|------|

| Instr. | Pen. | Instr. | Pen. |

| Hit    | 1    | Miss10 | 4    |

| Miss00 | 4    | Hit    | 2    |

| Hit    | 1    | Miss11 | 4    |

| Miss01 | 4    | Hit    | 1    |

| Hit    | 2    | Hit    | 3    |

| Hit    | 3    | Miss12 | 4    |

| Miss02 | 4    | Miss13 | 4    |

After the front-end driver discards the Cache Hit Instructions, in prepareSimulation() is calculated the Cycle that the misses *reach* the Memory System. As explained before, the Cycle of an instruction equals with the previous instruction Cycle plus the current instruction penalty, which embodies also the additive penalty of the discarded cache hit instructions. So the table transformed:

| Core 0 |       | Core 1 |       |

|--------|-------|--------|-------|

| Instr. | Cycle | Instr. | Cycle |

| Miss00 | 5     | Miss10 | 4     |

| Miss01 | 10    | Miss11 | 10    |

| Miss02 | 20    | Miss12 | 18    |

|        |       | Miss13 | 22    |

So finally the Trace that destined for DRAMSim2 input, after chronological reordering is:

| Instr. | Cycle |

|--------|-------|

| Miss10 | 4     |

| Miss00 | 5     |

| Miss01 | 10    |

| Miss11 | 10    |

| Miss12 | 18    |

| Miss02 | 20    |

| Miss13 | 22    |

ı.

At this point is clear that the goal of parallel application nature maintenance in the produced Trace is achieved due to the fact that a *core regardless* reordering occurred (only by Cycle) and also may exist more than one instructions in the same cycle, which shows the parallel nature of the produced Trace.

Subsequently, the simulate() function is called. Either in the case of Local Memory, or in the case of Remote, it has the same functionality. Before the instruction is passed as a new Transaction, all the necessary Memory Updates are performed, for timing reasons. While a Memory Update, the clock, as well as the internal Memory tasks go on for a Cycle without new input. The Memory is Updated as many times as the difference of the current and the previous instruction cycle, plus the defined Disaggregated latency. That extra latency, in the case of the local memory is equal to zero. After the updates are completed, a new Transaction is passed to Memory Simulator with its memory address and a *is read or write* boolean value as arguments. The code follows below:

```

mem_ is the simulated Memory System (local or remote)

1

/*

\mathbf{2}

i is the Trace Buffer index

3

dis_latency is the extra latency for remote

4

*/

LOCALFUN VOID Simulate ( MultiChannelMemorySystem *mem_, std::size_t i,

5

std::size_t dis_latency)

{

6

7

bool isWrite;

8

/* to avoid out-of-border access the first time */

9

if (i == 0)

10

{

for (std::size_t i2=0; i2 < rec[i].cycle - 0 + dis_latency; i2

11

++)

12

mem_{-} \rightarrow update();

}

13

else

14

{

15

for (std::size_t i2=0; i2 < rec[i].cycle - rec[i-1].cycle +

16

dis_latency; i2++)

mem_{-} \rightarrow update();

17

}

18

/* is read or write find out */

19

isWrite = (rec[i].r = W'? true : false);

20

/* add new Transaction to Simulator */

21

22

obj.add_one_and_run(mem_, rec[i].ip, isWrite);

```

## 23 }

#### Listing 3.7: Simulate() code

The add\_one\_and\_run() is the function that, finally, begins the simulation by passing a new Transaction to the simulated Memory System. It calls the addTransaction() function of DRAMSim2 with isWrite and addr as attributes. Essentially, that addTransaction() refers to the Multi-ChannelMemorySystem object method addTransaction(), which calls the corresponding MemorySystem addTransaction(). If, at this point, the Transaction becomes acceptable, directly is added to MemoryController Transaction Queue and then translated to DRAM command so as to be added to Command Queue and executed when its order comes; if not, is added to MemorySystem Pending Queue until is acceptable.

Those actions followed iteratively as soon as the whole Trace Window is passed for simulation. When the simulation session completes, the Pintool turns back to *Instrumentation mode* for the next Window etc. The whole process completes when the binary executable terminates, which means that the whole set of Instructions affect Main Memory is Instrumented and Simulated.

## 3.3 Skip Mode Feature

The applications run for Billion of Instruction and Cycles, and they have significant initialization phases. We therefore need the ability to "skip" initialization and simulate the "core" of the application or to sample over the application execution.

The choice of Skip mode can be applied to many tasks of the DIMEM Simulator, but it was observed that just as the Instrumentation sub-task has large overhead, so as the Simulation sub-task has the same, so it was decided the Skip mode to be applied over a full (Instrumented + Simulated) processed Window *periodically*.

The additional implementation based on a user defined constant integer named SKIP\_MODE, which models the number of periodically skipped windows. For example if SKIP\_MODE is 5, the DIMEM

Simulator will be in Skip mode for 5 Windows, before simulates one. Subsequently, again skips 5 Windows, one simulated etc.

New code added at Instrumentation Analysis functions, so as to be checked if the DIMEM Simulator is in Skip or Normal Mode before the sub-tasks, which may must be skipped, actually executed or called. It should be added into these functions because they are responsible for either Instrumentation or Simulation sub-task calls.

```

1

LOCALFUN UINT32 AnInstrumentationAnalysisFunc(arg1, arg2, ...)

\mathbf{2}

{

/* calculate window \# */

3

UINT32 c = icount.MultithreadCount();

4

UINT32 windowCnt = ins_count / INS_LIMIT;

5

6

7

if ( ( windowCnt >= STARTING_WINDOW-1 ) &

( (windowCnt % (SKIP_STEP + 1)) == 0 || SKIP_STEP == 0 ) &

8

(simulated_windows_counter < WINDOWS_TO_SIMULATE) ) \

9

{

10

/* instrumentation analysis code */

11

12

. . .

}

13

14

else

15

{

/* Skip mode code

16

print some helping messages */

17

18

. . .

icount.SetMultithreadCount(0);

19

20

}

21

}

```

Listing 3.8: Skip Mode code

## **3.4** Simulation Output

The Simulation Output consists of two discrete output files: Pintool's .out file and DRAMSim2 .log file.

#### Pintool .out file

These files contain information about Ram accesses and their percentage per Window, the Local and Disaggregated Clock cycles, the Total and Total Instrumented Instructions, the Local and Disaggregated Cycles per Instruction (CPI) and finally a complete Cache report. The Cache report contains information about Load/Store/Total Hits, Misses, Accesses, Miss Rate for each Cache Level separately. A simple example is following:

> Ram Accesses: 132980 Ram Percentage: 0.27% Simulation number: 1 of 40

```

...

Local Clock: 584842980

Disaggregated Clock: 6708072956

Total Instructions: 6300001184

Total Instrumented Instructions: 2000000000

0.292 cyles per Instruction (L)

3.35 cyles per Instruction (D)

...

L1 Data Cache 0:

Load Hits: 126941409

Load Misses: 7090283

Load Accesses: 134031692

```

| Load Miss Rate:  | 5.29%     |

|------------------|-----------|

| Store Hits:      | 61278276  |

| Store Misses:    | 4117665   |

| Store Accesses:  | 65395941  |

| Store Miss Rate: | 6.30%     |

|                  |           |

| Total Hits:      | 188219685 |

| Total Misses:    | 11207948  |

| Total Accesses:  | 199427633 |

| Total Miss Rate: | 5.62%     |

| Flushes:         | 0         |

| Stat Resets:     | 0         |

Listing 3.9: Pintool.out example

#### DRAMSim2 .log file

These files contain a DRAM report per EPOCH. The report presents statistical results about the current DRAM state per Rank. For each Rank, at the begining are presented the Total Return Trasactions and an average Bandwidth. Then are listed the Reads, Writes, Latency and Bandwidth (per Bank) and Power Data for that Rank. At the end of a .log file is presented a complete Latency Histogram for all Ranks. A simple example is following:

```

| Benchmark: BARNES | CPU: IVY | Scenario: 25-75 | Step: 3 |

______

Printing Statistics [id0]______

Total Return Transactions : 5521948 average bandwidth 68.119MB/s

-Rank 0 :

__Reads : 462380 (29592320 bytes)

__Writes : 184524 (11809536 bytes)

```

| -Bandwidth / Latency   | (Bank 0): 4.282 MB/s 33.576 ms |

|------------------------|--------------------------------|

| -Bandwidth / Latency   | (Bank 1): 4.300 MB/s 33.401 ms |

| -Bandwidth / Latency   | (Bank 2): 4.283 MB/s 33.555 ms |

| -Bandwidth / Latency   | (Bank 3): 4.249 MB/s 33.441 ms |

| -Bandwidth / Latency   | (Bank 4): 4.227 MB/s 33.471 ms |

| — Power Data for Rank  | 0                              |

| Average Power (mW)     | : 1000.132                     |

| -Background (mW)       | : 976.925                      |

| -Act/Pre (mW)          | : 7.577                        |

| -Burst (mW)            | : 13.621                       |

| -Refresh (mW)          | : 2.009                        |

| -Rank 1 :              |                                |

|                        |                                |

| Latency list (17)      |                                |

| [lat] : #              |                                |

| [30 - 39] : 5509845    |                                |

| $[40\!-\!49]$ : 6095   |                                |

| [50 - 59] : 6008       |                                |

| = Pending Transactions | : 0 (9081920616) =             |

|                        |                                |

Listing 3.10: DRAMSim2.out example

The number in brackets at the last line represents the reached DRAM Clock Cycle.

## Chapter 4

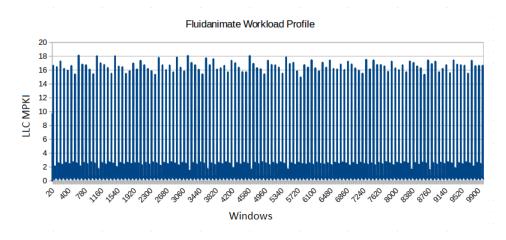

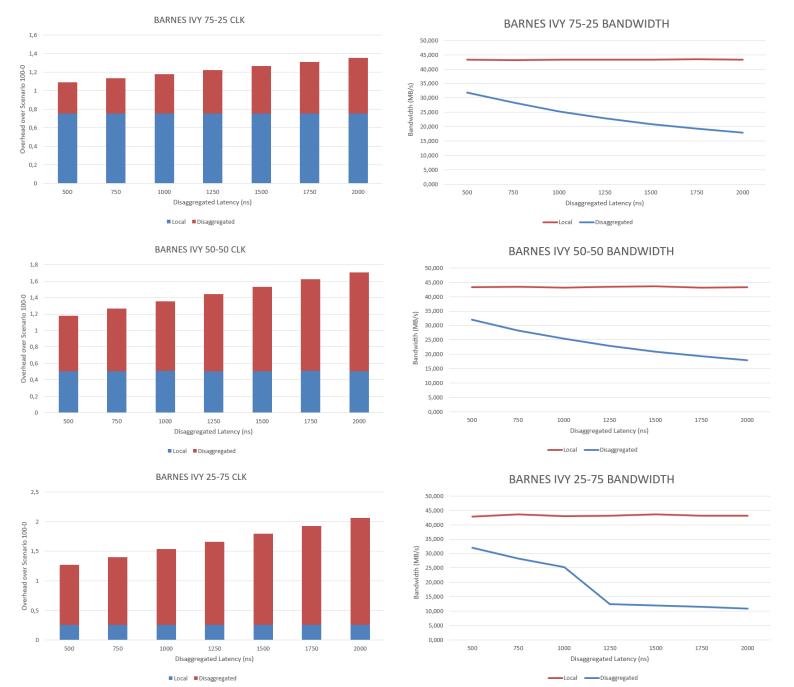

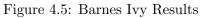

# **Evaluation and Experimental Results**