#### TECHNICAL UNIVERSITY OF CRETE

ELECTRONIC AND COMPUTER ENGINEERING DEPARTMENT

MASTER THESIS

### ON THE WAY OF HASHING FOR LOW COST EXACT PATTERN MATCHING

by

PAPADOPOULOS GIORGOS

CHANIA JULY 2005

Acknowledgments

ii

### Abstract

Network Intrusion Detection Systems monitor all network traffic passing on the local sensor segment, reacting to any anomaly or signature based activity. As networks become faster there is an emerging need for security analysis techniques that can keep up with the increased network throughput. Clasic networkbased intrusion detection sensors can barely keep up with bandwidths of a few hundred Mbps. Therefore, next generation "sensors" should provide deep packet inspection capabilities in order to provide protection at network speed. Since such systems rely on pattern matching techniques to analyze packets, hardware based systems with dedicated pattern matching logic has become very promising.

Currently there are plenty published architectures that implement network intrusion detection. Eventhough, some of them achieve very good performance and efficiency, there are many limits arise from the fact that NIDS perform mostly signature analysis and the number of the signatures continues to increase with great speed. A new approach to intrusion detection is needed to solve the problems of larger and faster networks and mostly the constraints caused by the increase of different kind of attacks, that recently published research suffer from.

In this thesis we propose the combination of hashing and use of memory to achieve low cost, exact matching of SNORT-like intrusion signatures exploiting the benefits of FPGAs. The basic idea is to use hashing to generate a distinct address for each candidate pattern, which is stored in memory. Our implementation, HashMem, uses simple CRC-style polynomials implemented with XOR gates, to achieve low cost hashing of the input patterns. We reduce the sparseness of the memory using an indirection memory that allows a compact storing of the search patterns and use a simple comparator to verify the match. Our implementation uses in the order of 0.15 Logic Cells per search pattern character, and a few tens of memory blocks, fitting comfortably in small or medium FPGA devices.

iv

# Contents

| 1 | Intr | oduction                   | 1  |

|---|------|----------------------------|----|

|   | 1.1  | Motivation                 | 2  |

|   | 1.2  | Scope                      | 3  |

|   | 1.3  | Outline                    | 4  |

| 2 | NID  | Ss                         | 5  |

|   | 2.1  | Snort Rules                | 6  |

|   | 2.2  | Software Based             | 6  |

|   | 2.3  | Hardware Based             | 8  |

|   |      | 2.3.1 NFAa & DFAs          | 9  |

|   |      | 2.3.2 CAMs and Comparators | 11 |

|   |      | 2.3.3 Hashing              | 13 |

| 3 | Has  | hMem Architecture          | 15 |

|   | 3.1  | Basic Idea                 | 15 |

|   | 3.2  | Initial Approach           | 17 |

|   | 3.3  | CRC generation             | 18 |

|   | 3.4  | Short Patterns             | 20 |

|   | 3.5  | Final Implementation       | 22 |

| 4 | Imp  | rovements                  | 25 |

|   | 4.1  | Doubling Performance       | 25 |

|   | 4.2  | Reusing Logic and Memeory  | 26 |

|   | 4.3  | Sharing Memory Structures  | 28 |

|   | 4.4  | Further Optimizations      | 30 |

|   |      | 4.4.1 Pipeline             | 30 |

|   |      | 4.4.2 Xilinx SRL16         | 31 |

|   | 4.5  | Upgrading                  | 31 |

| 5 | Eval | luation                    | 33 |

|---|------|----------------------------|----|

|   | 5.1  | HashMem Variants           | 34 |

|   |      | 5.1.1 Performance and Area | 34 |

|   |      | 5.1.2 Area Utilization     | 37 |

|   | 5.2  | HashMem vs Related Work    | 40 |

|   | 5.3  | Upgrade Evaluation         | 44 |

|   | 5.4  | Summary                    | 47 |

| 6 | Con  | clusions & Future Work     | 53 |

|   | 6.1  | Conclusions                | 53 |

|   | 6.2  | Future Work                | 54 |

| A | Арр  | endix A                    | 57 |

|   | A.1  | CRC Theory                 | 57 |

|   | A.2  | Software                   | 58 |

# **List of Figures**

| 2.1 | The distribution of patterns per pattern width. Comparison of the                                                            |    |

|-----|------------------------------------------------------------------------------------------------------------------------------|----|

|     | two rulesets                                                                                                                 | 7  |

| 2.2 | The distribution of total characters per pattern width. Comparison                                                           |    |

|     | of the two rulesets.                                                                                                         | 7  |

| 3.1 | The basic HashMem idea. To search for a pattern of length N char-                                                            |    |

|     | acters, we hash N input characters and produce a memory address.                                                             |    |

|     | If the stored pattern matches the input pattern, we have a match, otherwise no                                               | 16 |

| 3.2 | The process that turns out to the HashMEM architecture. (a) A                                                                |    |

|     | CRC generator implements the hash module but the 12-bit output                                                               |    |

|     | requires long pattern memory. (b) The insertion of the indirec-                                                              |    |

|     | tion memory level to alleviate the problem and shorten the pattern                                                           |    |

|     | memory                                                                                                                       | 17 |

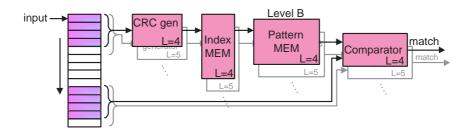

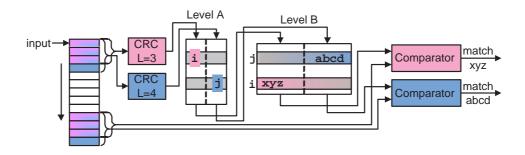

| 3.3 | Detailed HashMem Architecture. The entire structure is replicated                                                            |    |

|     | to detect multiple width patterns concurrently                                                                               | 17 |

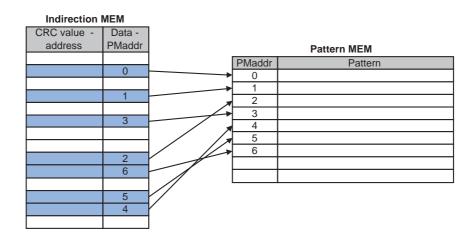

| 3.4 | The indirection procedure. Data from the indirection memory is                                                               |    |

|     | used to address the pattern memory                                                                                           | 18 |

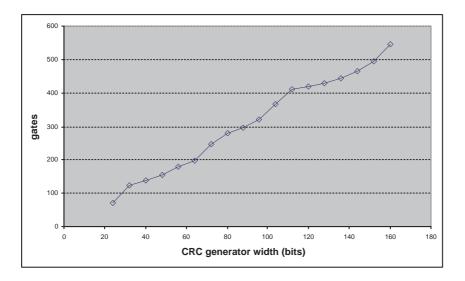

| 3.5 | The area cost in gates for various input widths of CRC generators                                                            |    |

|     | that use the polynomial $[x^{12} + x^2 + 1]$                                                                                 | 19 |

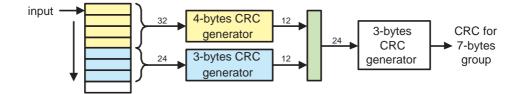

| 3.6 | Hierarchical CRC generation for a 7 character pattern using the                                                              |    |

|     | partial CRC results for the first 4 and the next 3 input characters. $% \left( {{{\bf{n}}_{{\rm{c}}}}_{{\rm{c}}}} \right)$ . | 20 |

| 3.7 | Short patterns matching procedure using two LUT memories                                                                     | 22 |

| 3.8 | Area cost relatively to the pattern width. The memory block line is                                                          |    |

|     | shown in green color and in pink is the distribution of the number                                                           |    |

|     | of the comparator LUTs                                                                                                       | 23 |

| 4.1  | The 2-bytes per clock cycle overall structure for a given pattern  |    |

|------|--------------------------------------------------------------------|----|

|      | width. The two memory ports are used for the patterns at offsets 0 |    |

|      | and 1, while the logic is replicated                               | 26 |

| 4.2  | A 7 character pattern ("abcdefg") is partially matched as two pat- |    |

|      | terns of 3 ("abc") and 4 ("defg") characters. The partial matches  |    |

|      | are then combined to determine the overall match                   | 28 |

| 4.3  | Sharing of indirection and data memories for patterns of different |    |

|      | widths. While conceptually the two ports point to the two origi-   |    |

|      | nal memories, the data is merged and the dashed separating lines   |    |

|      | indicate the separate read ports and not distinct data             | 30 |

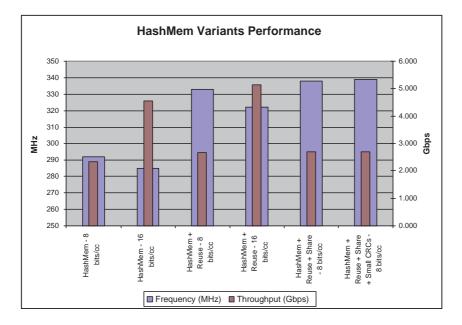

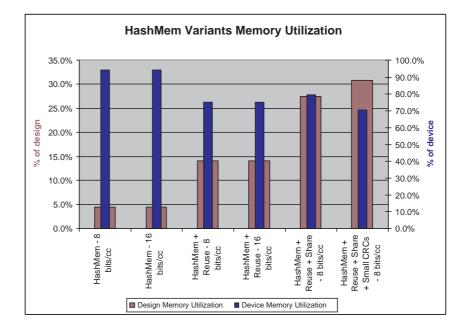

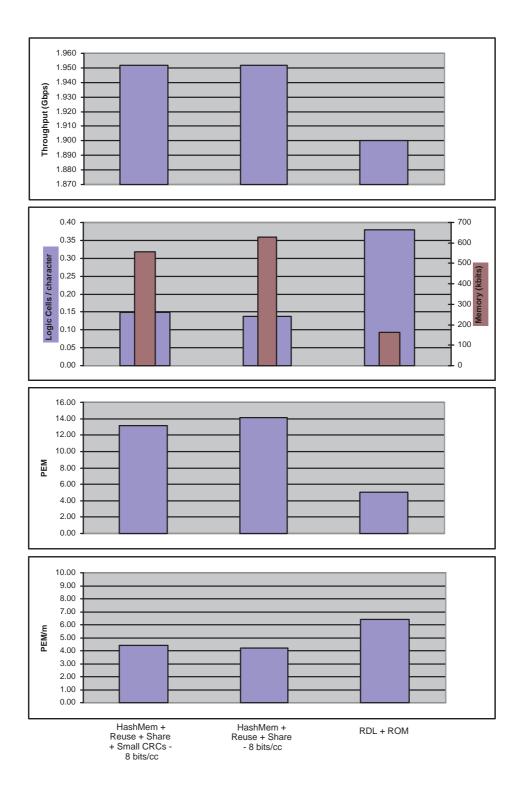

| 5.1  | A plotting diagram that compares the preformance in terms of fre-  |    |

|      | quency and throughout.                                             | 37 |

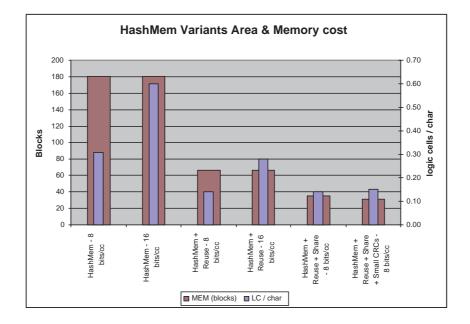

| 5.2  | A diagram that compares the area cost and the memory block usage.  | 38 |

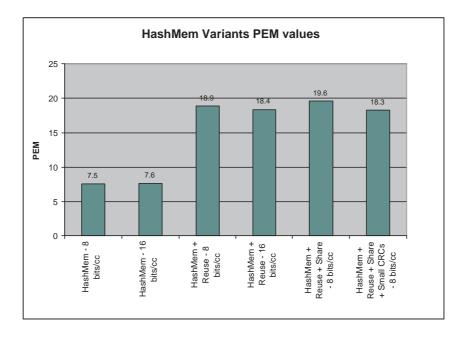

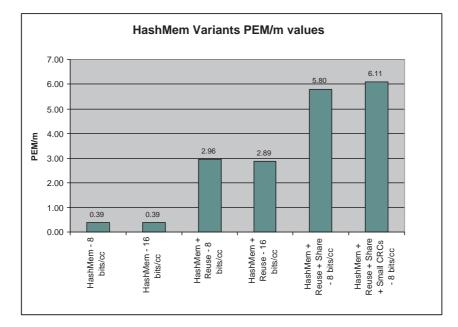

| 5.3  | A diagram that compares the PEM values                             | 38 |

| 5.4  | A diagram that compares the PEM/m values                           | 39 |

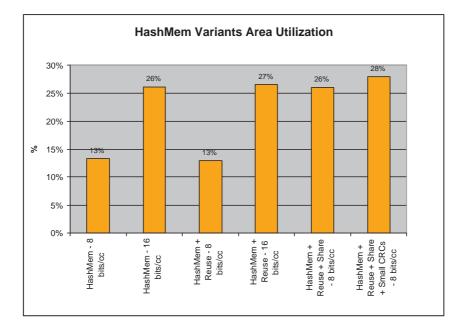

| 5.5  | The area utilization of the total device area for each implementa- |    |

|      | tion variant.                                                      | 41 |

| 5.6  | The memory utilization of the total device memory (right) and the  |    |

|      | used blocks of memory (left)                                       | 42 |

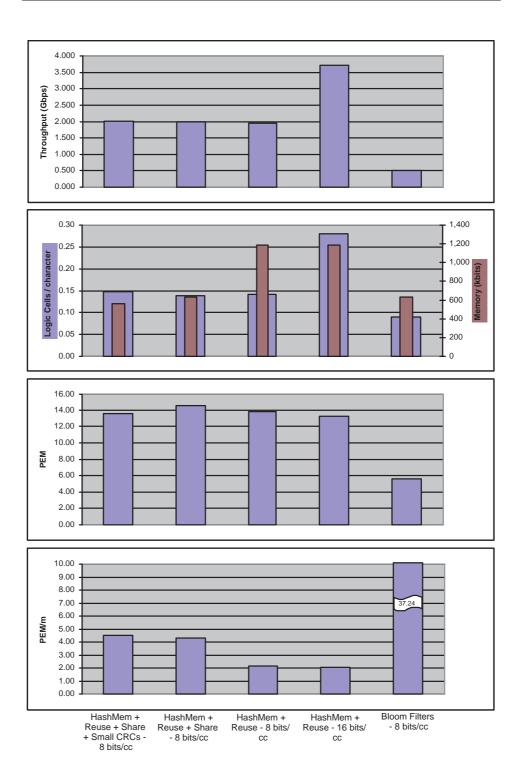

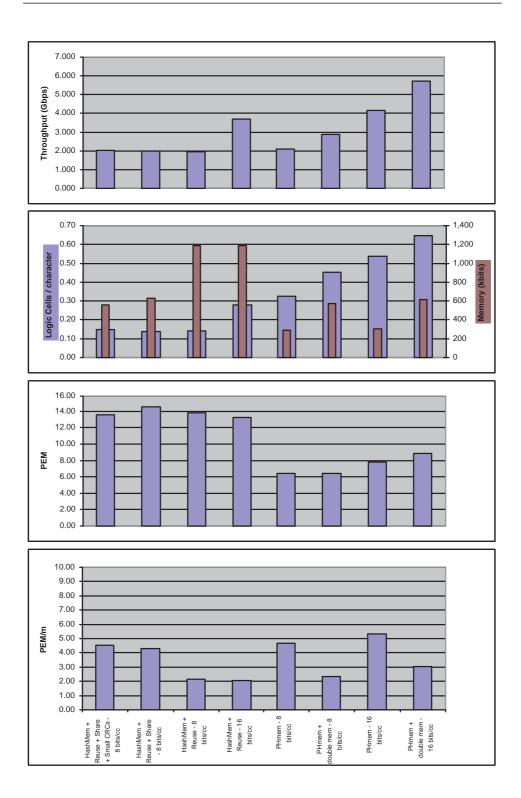

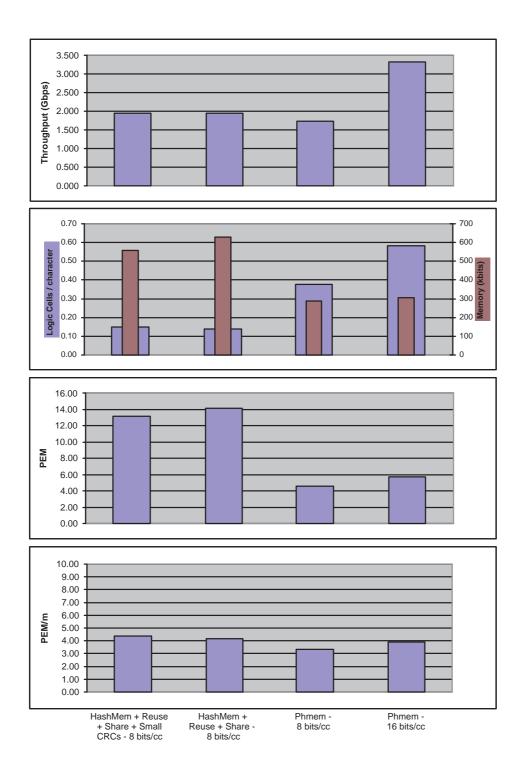

| 5.7  | HashMem (in Virtex2) compared to Bloom Filters architecture (in    |    |

|      | VirtexE)                                                           | 48 |

| 5.8  | HashMem compared to Cho's RDL+ROM asrchitecture, both im-          |    |

|      | plemented in Spartan3 family devices                               | 49 |

| 5.9  | HashMem compared to the PHmem architecture, for implementa-        |    |

|      | tions in Virtex2 family devices                                    | 50 |

| 5.10 | HashMem compared to the PHmem architecture, for implementa-        |    |

|      | tions in Spartan3 family devices                                   | 51 |

|      |                                                                    |    |

## **List of Tables**

| 3.1 | The CRC generation organization. Table (a) shows the straightfor-   |    |

|-----|---------------------------------------------------------------------|----|

|     | ward generation groups, table (b) contains the groups that use com- |    |

|     | bination of two already generated CRCs and table (c) the groups     |    |

|     | that use combination of four CRCs.                                  | 21 |

| 3.2 | The area characteristics of the initial design implementating for   |    |

|     | variable width groups                                               | 23 |

| 5.1 | Comparison of the HashMem architecture variants                     | 35 |

| 5.2 | Area utilization ratios.                                            | 36 |

| 5.3 | Area and Memory utilization of the HashMem architecture variants.   | 40 |

| 5.4 | Detailed comparison of HashMem and previous FPGA-based string       |    |

|     | matching architectures                                              | 45 |

| 5.5 | Area cost details and comparison of the "HashMem + Reuse" im-       |    |

|     | plementation between the old and the new ruleset                    | 46 |

<u>x</u>\_\_\_\_\_

### **Chapter 1**

## Introduction

Intrusion detection is needed in today's computing environment because it is impossible to keep pace with the current and potential threats and vulnerabilities in our computing systems. The environment is constantly evolving and changing fueled by new technology and the Internet. To make matters worse, threats and vulnerabilities in this environment are also constantly evolving. Today, firewalls with limited capabilities are built into many commercial network switch and router. Simple firewalls usually examine packet headers for specific information to determine whether to block or allow packet passage. But protection from firewalls as we know them is not enough. As computer networks grow faster, it becomes easier for malicious packets to enter into a network without being detected. The purpose of a Network Intrusion Detection System (NIDS) is to help protect computer network users from malicious attacks. They perform deep packet inspection in order to identify a matching signature. Three primary types of signatures are string signatures, port signatures, and header condition signatures. A signature based IDS will monitor packets on the network and compare them against a database of signatures or attributes from known malicious threats. The currently common known such database is provided by Snort [30] via Snort Rules, on which are based most of the NIDS projects. There are many systems introduced to provide intrusion protection initially in software, or even implementations in general purpose processors. However, both these solution suffer from the growth of the network speed, for which these systems are a bottleneck. What is more, the most computational intensive part of an NIDS is the patterns matching. For this reason, separate hardware based solutions, both in ASIC and FPGAs, have been also developed that perform signature matching and support high throughput. However, FPGAs seem to be more suitable because of their capability to be reconfigured in order to be updated to the current signatures.

#### **1.1 Motivation**

The area of hardware NIDS pattern matching has been very active recently. Several architectures have been proposed to implement SNORT-like pattern matching in FPGA. The architectures differ in the approach (finite automata or CAM-like), internal organizations, and of course in their cost- performance tradeoffs [29; 20; 21; 26; 16; 14; 33; 11; 4; 3; 6]. The common factor of these efforts however is the continuous drive for lower cost, at the same or better performance.

Many researchers designed pattern matching architectures based on regular expressions (NFAs / DFAs) [13; 20; 26; 29]. This is a low cost solution, but does not achieve very high performance. It is also difficult to perform more than one character per cycle, and usually, the operating frequency is limited by the amount of combinational logic for state transitions.

Other researchers preferred to implement discrete comparators [4; 5; 12; 32]. This choice leads to designs that operate at higher frequency, using one or more comparators for every matching pattern. This approach uses FPGA logic cells to store each pattern. In particularly, every LUT can store a half- byte of a pattern and the flip-flops that already exist can be used to create a fine-grained pipeline without any area overhead. The result is high speed designs but with an increased area cost. Finally, while the matching rules are very often updated and their number increases quickly, the area will easily become a serious constrain.

Another straightforward approach for pattern matching is the use of regular CAM [8; 21]. Current FPGAs offer the capability to use the integrated block RAMs for constructing CAMs. This is a simple procedure, as the CAM is fed with the input data and reports a match according to its contents. These approaches achieve modest performance but they have increased area cost as well. Another major drawback is the large number of the patterns and also their variable width. Thus, there must exist separate CAMs for patterns of different widths, or construct a CAM that may contain variable width patterns. The first approach requires too many CAMs while the second one is a hard task. But the major drawback of the

CAM approach generally is the width of the CAM in order to also perform long pattern matching.

#### 1.2 Scope

It is clear that the use of CAMs do not offer desirable results, since the logic cost remain high and there is significant a limitation in implementing long patterns. The common factor off all these efforts however is the continuous drive for lower cost, at the same or better performance. This work builds on two distinct ideas: (i) of the use of hashing of the input to retrieve approximate match information used in the Bloom filters [16; 3], and (ii) on the use of memories to provide exact match with fewer gates used by Burkowski [9], and later by Cho and Magnione-Smith [11].

Dharmapurikar et al. proposed the use of Bloom filters for low cost pattern matching [16]. Bloom filters are very elegant in representing set membership, but have two potential drawbacks: (i) they require multiple hash functions and memories, and (ii) they give an approximate match answer since they allow false positives. Attig et al. proposed the use of external SDRAM memory to augment the bloom filters with exact match, but at extra cost, and without offering worst case guaranteed bandwidth since the external memory is not pipelined [3].

Cho and Magnione-Smith used a CAM to match short patterns and to match unique prefixes of longer search patterns [11]. They choose the CAM width so as to provide unique prefix signals for each possible match. The match signals for all prefixes are then encoded to provide a memory address where the candidate suffixes are stored. The remaining input is compared against the expected suffix, and the result is the overall match for the pattern. Their approach offers very good memory density and low gate count. The cost of this approach however increases if the patterns have many and long common prefixes since they require even larger CAMs.

Our proposed architecture, HashMem (Hashing + Memory), attempts to strike a different balance between memory and logic usage. We try to maintain high performance using fine-grain pipelining and also minimize the logic cost by using simple logic functions and taking advantage of the FPGA embedded memory blocks. We use simple hash functions to generate sparse but distinct addresses for each of the search patterns, giving us a hint of whether there is a possible match (with probability proportional to the density of the hash space). We then use an indirection table to "gather" the search patterns in a compact memory, and compare the input against the single possible search pattern to eliminate false positives. Our implementations achieve processing throughputs between 1.95-2.7 Gbps processing a single input character per cycle, for a cost of 0.15 logic cells per search pattern character and a few tens of memory blocks, fitting comfortably in small or medium FPGA devices.

#### 1.3 Outline

The rest of the dissertation is organized as follows. In the next chapter we provide short information about NIDS and describe other NIDS and previous FPGA-based pattern matching architectures. In chapters 3 and 4 we describe the proposed Hash-Mem architecture starting from an initial approach and extend it to achieve better cost and performance. In section 5 we present the implementation results and we attempt a fair comparison with other published results. Finally, we conclude in chapter 6, and discuss some issues about future extensions.

At the end, there is an Appendix which contains some useful information about CRC theory, and also some information about the software assistance in order to build the VHDL cose.

### **Chapter 2**

# Network Intrusion Detection Systems

Intrusion detection is a security technology that attempts to identify and isolate "intrusions" against computer systems. Most ID systems identify such attacks using a technique called "signature analysis" (also called "misuse detection"). Signature analysis simply refers to the fact that the ID system is programmed to interpret a certain series of packets, or a certain piece of data contained in those packets, as an attack.

Most signature analysis systems are based off of simple pattern matching algorithms. In most cases, the IDS simply looks for a substring within a stream of data carried by network packets. When it finds this substring (for example, the "phf" in "GET /cgi-bin/phf?"), it identifies those network packets as vehicles of an attack. Snort rules are the most commonly used rules that describe such information about packets.

In the next sections we present some things of the Snort Rules, and then we present some software and hardware approaches that implement intrusion detection based on such rules.

#### 2.1 Snort Rules

One of the best network intrusion-detection systems (NIDS) is the free and open source Snort package. It is an open source network intrusion prevention system, capable of performing real-time traffic analysis and packet logging on IP networks. It can perform protocol analysis, content searching/matching and can be used to detect a variety of attacks and probes, such as buffer overflows, stealth port scans, CGI attacks, SMB probes, OS fingerprinting attempts, and much more.

Snort uses a flexible rules language to describe traffic that it should collect or pass. It has three primary uses. It can be used as a straight packet sniffer like tcpdump, a packet logger (useful for network traffic debugging, etc), or as a full blown network intrusion prevention system. Snort rules are powerful, flexible and relatively easy to write, so new rules to detect the latest malware may be written by everyone very easily.

Eash Snort rule can contain header and content fields. The header part containd information about protocol, source and destination IP addresses and port. The content part contains substrings that may exist in packets' payload.

In out work we implemented pattern matcing only for the payload data of packets using the content field of Snort rules. For our implementation we chose to use the Snort ruleset dated early 2004 that consists of 1,474 rules and a total of 18,636 characters. At the end we also used the last published ruleset, dated May of 2005, in order to evaluate our design in upgrading.

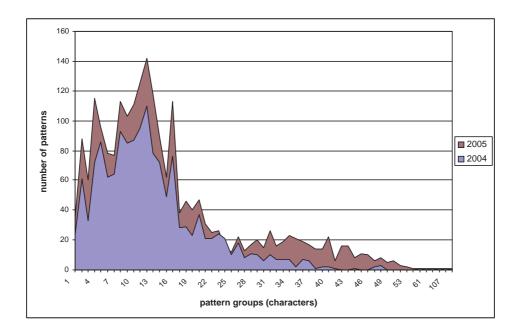

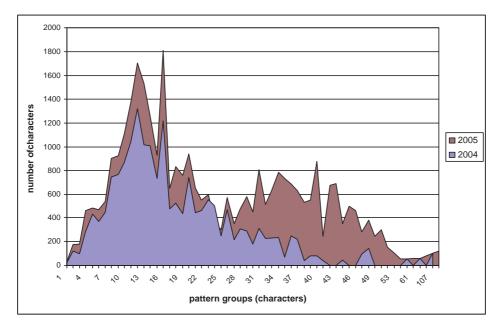

In figure 2.1 we present the pattern distribution per width for both of the two rulesets, while in figure 2.2 we perform a comparison of the character distribution per width. We can notice the increase of characters in almost every width group and especially in long pattern groups. What is more, we can see the great increase of the number of characters mostly in long patterns.

#### 2.2 Software Based NIDSs

There have been several software pattern matching algorithms based on Snort opensource rules. Snort NIDSs at its firts versions used bruteforce pattern matching resulting in very slow detection with low throughput. As network speed became

Figure 2.1: The distribution of patterns per pattern width. Comparison of the two rulesets.

Figure 2.2: The distribution of total characters per pattern width. Comparison of the two rulesets.

greater and attacks were increased, more efficient algorithms that would improve performance were necessary.

A first improvement came from the Boyer-Moore algorithm [7], and later the "2- dimensional linked list with recursive node walking". This improved the performance at 200% - 500% [30]. The algorithm scans the characters of the pattern from right to left beginning with the rightmost one. In case of a mismatch (or a complete match of the whole pattern) it uses two precomputed functions to shift the window to the right.

A variant of the Boyer-Moore algorithm came from Coit et al. [15], who implemented a "Boyer- Moore Approach to Exact Set Matching" as described by Gusfield [22], which uses an Aho- Corassic- like tree [1] to store patterns. Another adaptation of Boyer-Moore was introduced by Fisk et al. [18] which is shown to be faster for matching less than 100 patterns. Moreover, the MWM algorithm (Wu- Mander multi-pattern) [35] forms another implementation of Snort [31]. This implementation is the faster of all the above.

Finally, Markatos et al. [2] proposed  $E^2 \times B$  algorithm which provides quick negativeswhen the search pattern does not exist in data. It appears to be faster than the Fisk et al. implementation and for large incoming packets and less than 1-2k rules it is better than MWM too.

For a few handred Mbit/s, these software approaches provide sufficient power to capture and process the data packets. However, for higher-speed links (gigabit and higher), hardware accelerators have become necessary in order to process packets in real-time (or near real-time).

#### 2.3 Hardware Based NIDSs

Hardware bases NIDS is an alternative solution to overcome bandwidth limitations of software approaches. There have been many hardware approaches developed both in ASIC and FPGA systems.

ASIC systems usually store their rules in large memory blocks and examine incoming data packets in integrated design engines. Such systems are generally expensive and altough they achieve much better throughput compared to software systems, they do not impress with their performance. Moreover, the updating to

#### 2.3 Hardware Based

support new rulesets is achieved only by reloading memories with new data with no cpability of upgrading the search engine in case of changes in the kind of rules because of the complexity of attacks.

On the other hand, FPGAs seem more suitable as they are reconfigurable and also provide hardware speed. Thus, the updating process can be done even by entirely change the search engines with new design, with the only constrain to leave the interface intact. However, this is the hardest updating procedure. If only a small part of the design has been changed or added to the existing structure, it might be possible to perform incremental mapping and P&R, or even to partially reconfigure the device.

Most FPGA-based architectures are based on regular expressions (NFAs and DFAs) in order to preform pattern matching [13; 20; 26; 29]. Other researchers preferred to implement discrete comparators [4; 5; 12; 32]. Another straightforward approach for pattern matching is the use of regular CAM [8; 21] using the FPGA integrated block RAMs. Moreover, some designers implemented CAM-like architectures using dedicated logic [33]. Finally, another architectural way is to perform a kind of hashing on the input patterns in order limitize the logic usage [27; 34]. Next, we will present a brief description of these commonly used hardware approaches.

#### 2.3.1 Non Deterministic / Deterministic Finite Automata

The most common FPGA approach is the regular expressions matching, implemented using Finite Automata (NFAs or DFAs) [13; 20; 26; 29]. Regular expressions are an extremely powerful tool for manipulating text and data. Such designs have low cost but at a modest throughput. The basic idea of is to generate regular expressions for every pattern or group of patterns, and implement them with N/DFA.

A deterministic finite automaton (DFA) is a finite state machine where for each pair of state and input symbol there is a deterministic next state. Such a machine has a collection of states. At each point in time it determines which state to visit next based only on its current state and the next input character. The primary difference is that a NFA can potentially encounter a situation where it can make multiple choices. For example, if it's in state 2 and sees an a, it might be able to proceed to either state 3 or state 4. It even has the ability to proceed from one state to another without consuming any input the edges it follows in doing so are called epsilon edges, because they are usually labelled with the Greek letter  $\epsilon$ . Again, it may have a choice between following such an edge or following an edge that does consume input. In other words, in deterministic automata, for each state there is exactly one transition for each possible input, while in non-deterministic automata, there can be none or more than one transition from a given state for a given possible input. Thus, NFAs seems to be easier to design but DFAs are easier to implement as there are no choices to be considered.

The use of parallelism (processing multiple bytes or characters per cycle) is in general difficult in finite-automata implementations that are built with the implicit assumption that the input is checked one byte at a time. One proposed solution to this problem is the usage of packet-level parallelism where multiple pattern matching subsystems operating in parallel can process more than one packets[26]. Finally, finite automata are usually restricted in their operating frequency by the amount of combinational logic for state transitions.

The first hardware implementation was introduced by Floyd and Ullman in 1982, implemented in PLA [23; 19]. Much later, Sidhu and Prassanna introduced regular expressions and Nondeterministic Finite Automata (NFAs) for finding matches to a given regular expression [29]. Their work was primarily concerned with minimizing the time and space required to construct NFAs. For a single regular expression, the constructed NFAs and FPGA circuit could achieve 57.5-93.5 MHz in a Virtex XCV100 FPGA device. Then, Franklin, Carver and Hutchings [20] expanding on Sidhu et al. work, used regular expressions, with more complex syntax and meta- characters in order to cover the large set of expressions found in a Snort database. They managed to include up to 16,000 characters requiring 2.5-3.4 logic cells per matching character. They achieved about 30- 100 MHz on a Virtex XCV1000 and 50-127 MHz on a Virtex XCV2000E, and in the order of 63.5 MHz and 86 MHz respectively on XCV1000 and XCV2000E for a few tens of rules.

Later, Moscola, Lockwood et al. used the Field Programmable Port Extender (FPX) platform, to perform string matching for an Internet firewall [26]. They used regular expressions (DFAs) to store the patterns. They used JLex, a lexical analyzer generator for Java in order to convert regular expressions into DFAs. Initially, this implementation could operate at only 37 MHz on a Virtex XCV2000E and serve 296 Mbps. Finally, they described a way to increase bandwidth from 8 to

32 bits. This approach is capable of operating at speeds of 1.184 Gigabits/second for twenty-one  $\sim$ 20-character regular expressions, and exceeding speeds of 2.5 Gigabits/second for smaller numbers of similar regular expressions. Lockwood also implemented a sample application on FPX constructing a small FSM [24]. Lockwoods FSM had also 32 bits bandwidth. Because of its large input width, this approach is practically unsuitable to implement for many patterns and even more for complicated DFAs. Their circuit operates at 119 MHz on a Virtex V1000E-7 device achieving 3.8 Gbps throughput.

Finally, Clark and Schimmel [13] developed a pattern matching coprocessor that supports the entire SNORT rule-set using NFAs. In order to reduce design area they used centralized decoders instead of character comparators for the NFA state transitions. Their design processes one character per cycle, can match over 1,500 patterns (17,537 characters)achieves frequency 100 MHz having total throughput 0.8 Gbps in a Virtex-1000 device. In FCCM 2004, Clark and Schimmel expanded on their earlier work implementing designs that process multiple incoming bytes per cycle. Their detailed results proved that NFAs and predecoding can produce low cost designs with higher performance, compared to DFAs and simple brute-force approaches.

#### 2.3.2 CAMs and Discrete Comparators

The most straight-forward method to building pattern matching circuits is known as the brute-force approach. The brute-force algorithm produces circuits that perform a full comparison of every target pattern against the input in each clock cycle (discrete comparators). In other words, no match state is saved across cycles. The input text from a packet payload is broadcast to all of the pattern matchers and shifted past the target patterns at a rate of one character per clock cycle. A pattern matcher for a length m string usualy contains an m-character shift register for buffering input characters, m character comparators, and a match output that is true when all of the comparators signal a match between the contents of the input shift register and the target pattern. Once the shift register is full, the pattern matcher performs m parallel character comparisons per clock cycle.

The algorithm can be generalized to process i characters per clock cycle by instantiating i copies of each pattern and shifting the content of the buffer i characters in each cycle. To properly detect all possible positions of the pattern in the input stream, each copy of the pattern must start at a different offset relative to the beginning of the input buffer. The first copy starts at offset 0 and the ith copy starts at offset i-1. Cho et. al. [12] implemented a brute-force design that processed 4 characters (32 bits) per clock cycle. Sourdis et. al. [32] increased the throughput of Chos design significantly through aggressive pipelining, which also resulted in increased latency and lower character density.

Moreover, current FPGAs give designers the opportunity to use integrated block RAMs for constructing regular CAM. This is a simple procedure, that achieves modest performance, in most cases better than simple N/DFAs architectures. Gokhale, et al. [21] used CAM to implement Snort rules NIDS on a Virtex XCV1000E. They performed both header and payload matching on CAMs, however, increasing CAMs depth over 32 entries, resulted in unacceptable operating frequency due to routing. They achieved frequency of 68 MHz wiht 32 bits input data, resulting in 2.2 Gbps.

Cho et al. improved their earlier architecture introducing a ROM-based solution [10] to perform packet filtering. They shared partial data comparators and also dedicated decoders for character matching in combination to the partial matches. A further improvement was presented a little later achieving better results [11]. In their final design they choose the CAM width so as to provide unique prefix signals for each possible match. The match signals for all prefixes are then encoded to provide a memory address where the candidate suffixes are stored. The remaining input is compared against the expected suffix, and the result is the overall match for the pattern. Their approach offers very good memory density and low gate count. The cost of this approach however increases if the patterns have many and long common prefixes.

Finally, another CAM-based solution was introduced by Baker et al. [5]. They perform an entire ruleset processing so they can partition a ruleset in order to optimize the area and time requirements of the system. They apply graph theory techniques early in the circuit design problem, preprocessing the ruleset, in order to achieve high performance. However, this architecture allows false positives, and this is what they trade to rduce logic cost.

#### 2.3.3 Hashing

Hashing may be a promising approach for implementing pattern matching hardware. The idea is based on the fact that using hashing on the input we may retrieve approximate match information. This of course allows false positives, since the hash function does produce the same value for other patterns too.

This idea was firstly used in the Bloom filters by Dharmapurikar et al. The proposed the use of Bloom filters for low cost pattern matching [16]. Bloom filters are very elegant in representing set membership, but have two potential drawbacks: (i) they require multiple hash functions and memories, and (ii) they give an approximate match answer since they allow false positives. Attig et al. proposed the use of external SDRAM memory to augment the bloom filters with exact match, but at extra cost, and without offering worst case guaranteed bandwidth since the external memory is not pipelined [3].

Another architecture that uses hashing to narrow the search character width is introduced by Sourdis et al. This approach is very close to ours as they use a hashing function and memory to retrieve final match information. However, in their architecture they try to extract perfect hashing function in order to perform search pattern encoding. Then they address an indirection memory that directs to the corresponding pattern in the pattern memory. In opposite to our design, they use a centralized, banked memory for efficient pattern storage, and they trade logic to reduce the memory size.

### **Chapter 3**

## **The HashMem Architecture**

In this chapter we descuss the initial idea on which the HashMem approach is based. Then, we describe the initial implementation presenting some issues that affect the efficiency of the approach. Finally, we evaluate the implementation for ways to improve upon it.

#### 3.1 The Basic Idea

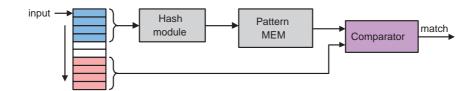

The basic idea of HashMem is to use the input pattern to generate a unique candidate pattern address. Lets assume we want to match a set of patterns of length Lcharacters. We feed L input bytes into a hashing module to generate the unique address of the candidate pattern. We then read the candidate pattern from the memory and compare it with the (delayed) input to verify the match.

This overall structure, shown in figure 3.1, has been used by Cho et al. [11] using prefix match logic, and an encoder to generate the unique address. Unlike this work, we use a CRC-type computation on the entire length of the match and avoid the use of encoders. CRCs have two advantages:

- 1. They are simple functions with small implementation cost,

- 2. They produce a "randomized" result, with a uniform distribution of all possible patterns of a specific width into each CRC value.

Depending on the polynomial used, each CRC function will produce a different mapping of patterns to locations. This gives us a way of adapting to different

Figure 3.1: The basic HashMem idea. To search for a pattern of length N characters, we hash N input characters and produce a memory address. If the stored pattern matches the input pattern, we have a match, otherwise no.

pattern sets. Given a set of patterns, we can select a polynomial that produces distinct CRC values for every search pattern. Since a match can begin anywhere in the input stream, for our L character search, we have to check each of the L-character substrings starting at offsets 0, 1, ..., up to the end of the input packet. To achieve this, we pipeline the CRC generator.

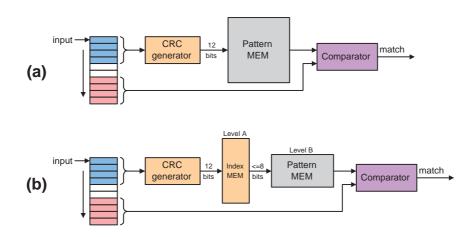

Finding a polynomial that guarantees distinct addresses for each search pattern is easier when the density of the hash space is smaller. Experimentally we found that using 12 bits for Snort patterns, we can use simple polynomials that achieve this guarantee. However, a small memory density means that many memory locations are not used. Using 12-bit polynomials means that the address of the pattern memory is also 12 bits where the memory length is 4096. Supposing that the stored patterns are usually less than 100, the utilazation of the memory is less than 2.5%. This problem is exacerbated for longer patterns since the memory is as wide as the search patterns and more blocks are required to set up the specific memory. To alleviate this overhead, we introduce a level of indirection, using 12 bits of CRC address, and packing the search patterns in a shorter memory to improve its utilization. The width of the indirection memory is related to the number of stored patterns, with 8 bits being more than enough for patterns of a given width. Thus, for the indirection memory, although the length is also 4096 and the utilization will be the same, the necessary memory blocks will be at most two since the width is at most 8 bits. Moreover, the pattern memory has now the minimum number of entries required to accomodate the search patterns, and as a result a better utilization. Figure 3.2 shows the process of using CRC generators as hashing functions and transforming the detection path with the use of the indirection memory level.

Until this point we discussed patterns of equal width (L). Dealing with multiple width patterns requires to (i) know the width of the possible matches, and (ii) the ability to read all these possible patterns. Since any given character of the input

Figure 3.2: The process that turns out to the HashMEM architecture. (a) A CRC generator implements the hash module but the 12-bit output requires long pattern memory. (b) The insertion of the indirection memory level to alleviate the problem and shorten the pattern memory.

Figure 3.3: Detailed HashMem Architecture. The entire structure is replicated to detect multiple width patterns concurrently.

stream can be the last character of a pattern of arbitrary width, we use the simple approach of replicating the entire structure once for each of the different pattern widths. The resulting architecture is show in Figure 3.3.

#### 3.2 Initial Approach

For the construction of a HashMem system, we first group the search patterns according to their width L. Then, for each group, we identify a 12-degree CRC poly-

Figure 3.4: The indirection procedure. Data from the indirection memory is used to address the pattern memory

nomial that produces distinct CRC values for each pattern in the group. Using a software CRC generator based on this polynomial, we calculate the CRC values for all the patterns of each group. Then, the search patterns are packed in a pattern memory of width L without any restriction on their location. Finally, the indirection memory is initialized based on the calculated CRC values and the location of the corresponding patterns in the mattern memory, as shown in figure 3.4.

Initially the indirection memory is initialized to a special value "No- Match". Then for each search pattern P that is stored in location PMAddr(P) in the pattern memory, we set location CRC(P) of the indirection memory to PMAddr(P). This essentially creates a pointer to the stored search pattern, if there is one.

The whole detection process is discrete for each width. Thus, there is one CRC generator for each width group, one memory for the indirection level, one for the pattern group storage and one comparator for the specific width for the final match.

#### 3.3 Efficient CRC Generation

The HashMem architecture uses one CRC generator for each search pattern width, and each generator has to produce the CRC of L characters in one cycle. To achieve a CRC implementation according to these requirements, we first imple-

Figure 3.5: The area cost in gates for various input widths of CRC generators that use the polynomial  $[x^{12} + x^2 + 1]$ .

mented a fully parallel, unpipelined generator, and then we pipelined it to achieve (i) throughput of one full hash per cycle, and (ii) good cycle time.

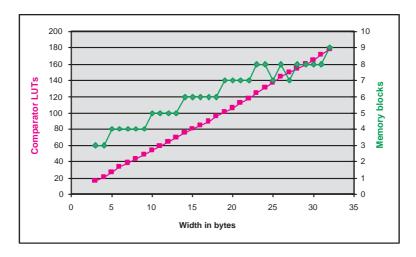

While each CRC generator is relatively simple, its cost is proportional to the input width. Some Snort search patterns exceed 50 characters or 400 input bits, for which even simple CRC generators use many gates. The diagram in figure 3.5 shows the increase of the area cost in gates of variable width generators of the same polynomial  $[x^{12} + x^2 + 1]$ .

To reduce the cost of wide CRC generators, we produce the hash value for wide patterns reusing the narrower CRC values as partial hashes. We implement full CRC generators for the widths of 3, 4, 5 and 6 bytes. Then, to produce a CRC value for say 7 character wide pattern, we perform a CRC function on the CRC results for the first 3, and the next 4 input stream characters. The partial CRC values should be delayed appropriately so that they arrive at the same time to the second level CRC generator. Figure 3.6 illustrates this 7-character wide example.

This hierarchical CRC calculation and the reuse of partial CRC values results in significant area savings reducing the input of the generators to a more manageable width. Particularly, the combinational generators are 24-bits wide for patterns of widths from 7 to 12, while these widths are combined from two width groups, each of which produce a 12-bit CRC. Moreover, the rest groups from 13 to 32 are generated by the combination of four groups which results to a 48-bits wide input

Figure 3.6: Hierarchical CRC generation for a 7 character pattern using the partial CRC results for the first 4 and the next 3 input characters.

for their generators. The reusing organization, which presents the group combinations for widths from 12 to 32 and also the width of the CRC generator required, is shown in table 3.1.

Another parameter affecting the cost of the CRC computation is the width of the CRC value. Smaller widths reduce the size of indirection memory, but make it harder to guarantee distinct addresses for each search pattern. We experimented with various CRC widths, and found that a larger space density, increases the cost (in number of LUTs) of the CRC generators. In practice, we found that the best compromise between CRC implementation cost and memory size is at 12 bits (i.e. using polynomials of degree 12). For small pattern widths, we can use smaller degrees (10 and 11), but in general we used 12 bits for every pattern width.

#### 3.4 Handling Very Short Patterns

Very short patterns (1-2 characters) offer very few input bits, making the CRC calculation an overkill. Furthermore, the total pattern characters are very few, underutilizing the indirection and pattern memories. To address this inefficiency, it would be better to address the pattern memory directly with a minimum amount of logic. To achieve this we use a simple lookup table of 256 entries to match the single character patterns. We use the input byte to address directly the LUT, which is initialized with '1' in the addresses that represent the search patterns.

For the two character patterns, we notice that the total distinct patterns characters are less than 64, allowing an encoding with 6 bits. Based on this observation, we added a recoding function in the unused bits of the single character lookup table, recoding the 8 bits input into a 7 bit code. The most significant bit represents

| group<br>width | CRC input<br>width |

|----------------|--------------------|

| 3              | 3                  |

| 4              | 4                  |

| 5              | 5                  |

| 6              | 6                  |

|                |                    |

| _    | - <b>\</b> |

|------|------------|

| - 13 | a 1        |

| - 19 |            |

| group<br>width | partial<br>groups | CRC input<br>width |

|----------------|-------------------|--------------------|

| 7              | 3, 4              | 3                  |

| 8              | 4, 4              | 3                  |

| 9              | 4, 5              | 3                  |

| 10             | 5, 5              | 3                  |

| 11             | 5, 6              | 3                  |

| 12             | 6, 6              | 3                  |

| • •       |  |

|-----------|--|

| n         |  |

| <b>DI</b> |  |

|           |  |

| group<br>width | partial<br>groups | CRC input<br>width |

|----------------|-------------------|--------------------|

| 13             | 3, 3, 3, 4        | 6                  |

| 14             | 3, 3, 4, 4        | 6                  |

| 15             | 3, 4, 4, 4        | 6                  |

| 16             | 4, 4, 4, 4        | 6                  |

| 17             | 4, 4, 4, 5        | 6                  |

| 18             | 4, 4, 5, 5        | 6                  |

| 19             | 4, 5, 5, 5        | 6                  |

| 20             | 5, 5, 5, 5        | 6                  |

| 21             | 5, 5, 5, 6        | 6                  |

| 22             | 5, 5, 6, 6        | 6                  |

| 23             | 5, 6, 6, 6        | 6                  |

| 24             | 6, 6, 6, 6        | 6                  |

| 25             | 6, 6, 6, 7        | 6                  |

| 26             | 6, 6, 7, 7        | 6                  |

| 27             | 6, 7, 7, 7        | 6                  |

| 28             | 7, 7, 7, 7        | 6                  |

| 29             | 7, 7, 7, 8        | 6                  |

| 30             | 7, 7, 8, 8        | 6                  |

| 31             | 7, 8, 8, 8        | 6                  |

| 32             | 8, 8, 8, 8        | 6                  |

|                |                   |                    |

(c)

Table 3.1: The CRC generation organization. Table (a) shows the straightforward generation groups, table (b) contains the groups that use combination of two already generated CRCs and table (c) the groups that use combination of four CRCs.

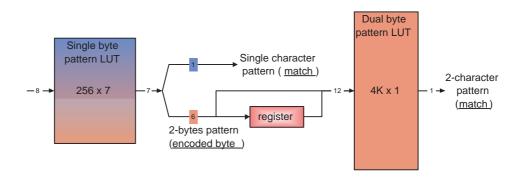

a single character match and the rest 6 bits are the encoded value of the half part of dual-byte patterns. Then, each encoded part is stored in a register and after the appropriate delay of the first encoded part, the two input recoded characters, which amount to 12 bits, address a 4Kx1 lookup table to determine any two-character matches. Each of these two lookup tables uses one memory block and a minimal ammount of logic for the pipeline delay. This procedure is shown in figure 3.7.

Actually, this method for matching dual-byte patterns is usuable for more than 64 patterns too. To be more specific, if these patterns amount at most to 128 they can be recoded in 7 bits each + 1 bit for the single byte match. This does not increase the memory block requirements in none of the two lookup tables, since the memory required for the two-bytes LUT fits in the shortest primitive memory block, which is 16kx1, and the widest block has 512 entries of 36 bits which is more than enough for the single character patterns LUT.

Figure 3.7: Short patterns matching procedure using two LUT memories.

#### 3.5 The Final Implementation - What's Wrong With It

In this first approach of the HashMem architecture we implemented a single-byte throughput design. Data are input in a 1-byte wide shift register once per cycle. Then, one CRC generator for each width begins the pipelined process by calculating one CRC value per cycle feeding the indirection memory. The indirection memory addresses the pattern memory and finally the requested pattern is compared to the corresponding delayed input string.

In this design we implemented the detection of patterns which width varies from 1 to 32 bytes. For the short patterns of 1 and 2 bytes wide we used described the look-up table approach. Then, we implemented the straightforward description shown in figure 3.2 (b) for pattern widths 3-6 and finally we used their CRC generator ouputs to calculate the CRC values for the rest groups.

This whole process, as already been discribed in details, forms a quite simple design to implement but also has two major drawbacks. One is the high area cost in memory blocks, which amounts to 181 for both the two memory levels. The greatest portion of the memory blocks is used in the second memory level, in the pattern memories. Since none of the groups is consisted of more than 128 strings, the primitive memory block we use is the  $512 \times 36$  which is the widest and also the shortest one. This means that the pattern memory utilization is less that 25% and becomes even lower for wide string groups where the strings are even less. Moreover, wide strings require a large number of memory blocks as well.

Another major drawback of the initial implementation of the Hash+Mem architecture is the logic cost. Similarly to above, the greatest cost is particularly at

Figure 3.8: Area cost relatively to the pattern width. The memory block line is shown in green color and in pink is the distribution of the number of the comparator LUTs.

|                                       | implementations |        |        |

|---------------------------------------|-----------------|--------|--------|

| string widths (bytes)                 | 112             | 124    | 132    |

| implemented strings<br>(total: 1,476) | 873             | 1,352  | 1,432  |

| number of bytes (total:<br>18,636)    | 6,526           | 14,633 | 16,879 |

| logic cells                           | 925             | 3,153  | 5,172  |

| MEM blocks                            | 42              | 120    | 181    |

| Logic Cells / char                    | 0.14            | 0.21   | 0.31   |

Table 3.2: The area characteristics of the initial design implementating for variable width groups.

the large comparators since the LUTs required for their implementation is about proportional to the width of the patterns in comparison. Figure 3.8 describes how the cost of the comparators and the number of the memory blocks are increased by the increase of the group width. Finally, it is important to notice that the distribution of the logic cost among the main logic modules used in this implementation is almost 85% for the comparators and only the rest 15% is utilized by the CRC generators.

In table 3.2 we demonstrate the area characteristics of this implementation including the memeory blocks and the logic cells required. There are also values of designs for less width groups implemented. It is clear how the cost increases proportionally to the width included in the design. We notice that the number of the logic cells per character is increases as more groups are added in the design. Moreover, the use of a large FPGA device is obligatory because of the memory needs, since the amount of the memory blocks is very large, eventhough the logic utilization covers only a small percentage of its logic cells.

## **Chapter 4**

# Improvements and further implementations

In this chapter, we address initial approach drawbacks' in order to improve upon the design. Then, we present some new HashMem variants each of which implemement an additional improvement.

#### 4.1 **Processing Two Characters Per Cycle**

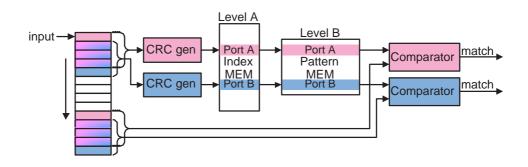

A first improvement to the initial implementation is achieved by processing two characters per cycle. The performance of a HashMem system can be doubled exploiting the fact that Xilinx memory blocks provide two read ports. Hence, we can double the processing throughput to 2 input characters per cycle, processing two patterns at offsets 0 and 1 per cycle. To achieve this, we need to implement a separate hash+mem path for each of the two processing patterns. Since the memories are dual ported we may use the existing memory assigning each port to each one of the two patterns.

Therefore, we need to provide two addresses into the memories per cycle. This means that the CRC generator logic has to be replicated, for offsets 0 and 1 in the input stream. The two CRC values, which are used as addresses, are fed to the two ports of the same memory (as they refer to the same pattern width). The indirection memory provides two pattern memory addresses, which are used at the

Figure 4.1: The 2-bytes per clock cycle overall structure for a given pattern width. The two memory ports are used for the patterns at offsets 0 and 1, while the logic is replicated.

two address ports of the same pattern memory as well. The two possible search patterns provided by the two output ports of the pattern memory must be matched against the input for offsets 0 and 1. As a result there are also required two copies of the comparators. The overall structure for a given pattern width is shown in figure 4.1.

One advantage of this technique is definitely that the throughput is doubled. What is more, the memory requirements remain the same since we take advantage of the dual ported memory blocks. On the other hand, the logic cost is almost doubled. The CRC generator and the comparator at the final stage, which are the main logic units of the design, are now duplicated.

#### 4.2 Reusing Logic and Memory for Wide Patterns

Another improvement may be achieved aiming to a better utilization of the memory blocks and also by decreasing the comparators cost. As I have already mentioned very long strings are few but use very wide pattern memories. The widest Xilinx memory block has 512 entries of 36 bits [36; 38; 37]. The few wide patterns will leave almost the entire memory empty. Even in the indirection memory level which length depends on the CRC width the utilization is also very low.

In addition, most of the logic in the HashMem architecture comes from CRC generators, but mostly from the pattern comparators. Making a more CRC efficient

generation, as discribed in section 3.3, we reduce the cost of wide CRC generators by making use of existing narrower CRC values as partial hashes. However, the higher cost in logic comes from the comparators and especially from the long ones, since their cost is proportional to their width.

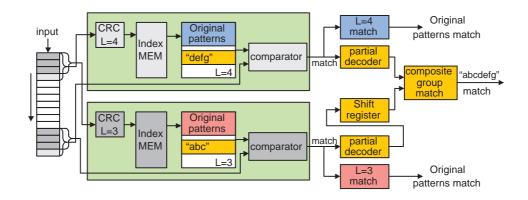

Long patterns, due to their small number in the Snort rule set, offer us with this opportunity to reuse both the memory and the comparator structures instead of replicating them. The idea is that instead of matching a wide pattern in a separate structure, we split it in smaller pieces in order to fit in existing narrower structures. Thus, we match each of them in the existing structures, and use extra glue-logic to identify the long pattern parts and to combine the partial matches into the complete match.

Figure 4.2 depicts a short example where a 7 character pattern in matched as two sub- patterns of 3 and 4 characters. Note that we use this small pattern width only for reasons of clarity and brevity; we actually used this technique for widths 17 and up. The two sub-patterns are added into the existing structures for widths 3 and 4, reusing the CRC generators, memory, and comparators. First of all, we break the 7 character patterns into the 3 and 4 character parts. Mixing the 3-character parts with the original 3-character patterns we may look for a CRC polynomial for the new 3-character set. Then, we initialize the inderection and the pattern memory with the new inderection values and the new pattern set respectively. Finally, whenever a match takes place we have to identify whether is refered to a complete (original 3 or 4 character pattern) pattern match or to a partial match. We also have to be able to pair the correct parts for each long pattern. For that reason we use the indirection address in conjunction to the reported match in order to generate a recoded value. The match of these recoded values generates the composite group match. Still, there are two issues that we have to address in order to make this approach work.

First, in order to add a new pattern in an existing structure, the CRC of each pattern part should not conflict with any preexisting pattern in the original set. The existence of dublicates between parts or between a part and a preexisting pattern is not a problem because we just keep only one of each. However, the above restriction is addressed in two ways: first, the density of the hash space still remains small, so probabilistically our chances are good. Second, if we are indeed unlucky, we can always change the CRC polynomial and find one that removes the conflict. Should both of these options fail, we still have alternatives. We can partition the pattern in a different way (in our example perhaps in 4+3 or 2+5 characters instead

Figure 4.2: A 7 character pattern ("abcdefg") is partially matched as two patterns of 3 ("abc") and 4 ("defg") characters. The partial matches are then combined to determine the overall match.

of the 3+4 used in our example). The reuse of the resources can happen in many different ways increasing our chances of finding a convenient mapping. In our experience, the complicated options are not needed and it is straightforward to add the sub- patterns in existing structures.

The other issue is the glue logic that combines the partial matches into overall matches for the pattern. Since each of the two sub-patterns are detected at offset 0, we must delay the match information for the first sub-pattern to AND it with the corresponding data of the second sub- pattern and determine the overall match. In our example we must delay the first 3 characters match data by 4 clock cycles.

This implementation approach can be extended to further improvement applying the doubling of the throughput as described in the previous section. This means that even the glue logic, used to identify the long pattern parts and to combine the partial matches into the complete match, should be replicated.

### 4.3 Sharing Memory Structures between Different Pattern Widths

To further reduce the amount of memory needed, we can exploit even more two already noticed facts: (i) the low density of the indirection and data memories, and (ii) that the Xilinx memories are dual ported. The idea for sharing the data memory is simple: we partition the memory in two independent portions. The "upper" portion is used for patterns of width X and the "lower" portion is used for patterns of width Y (usually X + 1). Consider for a moment the data memory for say width 3. The minimum dimension of a single Xilinx memory block is 512x36 bits (enough for 4 characters), while the number of patterns of widths 3 and 4 is 33 and 72 patterns respectively. It is clear that both these sets of patterns can coexist in the same memory block, *without* any overhead. However, since we use different CRC generators for 3 and 4 characters, the addresses for each of the widths will be different. Here we can use the two read ports of the memory: we statically assign each read port to a given size, and arrange the patterns in two separate portions of the memory space.

While sharing the data memories is fairly straightforward, sharing the indirection memories is a bit more involved. Consider a simple example where there is only one string for each of the widths 3 and 4. Each of the indirection memories for widths 3 and 4 will have a single non-empty entry at the location determined by the CRC function of the corresponding width. These non-empty locations will point to the data memory locations that the actual strings will be placed, say X and Y. If the locations of the two non-empty entries are distinct, we can merge the two memories, creating a simple indirection memory, with *two* non-empty locations, with contents X and Y at their original locations. Moreover, since we devide the pattern memory in two portions, we may assign the prefix of the addresses of each port directly to a value that declares the memory portion used from each one of the two width sets. This allows as to store in the indirection memory only the relevant part of the pattern address as if they were stored in separate memories. Now we can use the two read ports for each of the pattern widths. Figure 4.3 outlines the sharing of both levels of memory in our architecture.

To show that this scheme does work, we consider two cases, of a pattern match and of a pattern mismatch. First, if a pattern match input appears for say size 3, the hash value will point to the location containing X. The data memory string will be read for width 3 from the specific port, and a match will be reported. For an arbitrary non-match input, the CRC value will most probably point to an empty location, resulting in a mismatch. However, there is the possibility that for some 3 character input, the CRC value will point to the location initialized to the 4 character pattern. To avoid any false matches, we augment the comparator with an additional bit that indicates the portion of the memory that the pattern belongs to. In this way, when we read location Y of the data memory that contains in a 4

Figure 4.3: Sharing of indirection and data memories for patterns of different widths. While conceptually the two ports point to the two original memories, the data is merged and the dashed separating lines indicate the separate read ports and not distinct data

character pattern, it is impossible to report a 3 character match.

If there are same CRC values in patterns of the two sets then we may have a conflict in addressing the pattern memory. In that case we should change one or both of the CRC polynomials to avoid the conflict. Another course of action is to take advantage of the CRC conflict by allocating the conflicting patterns in matching relative addresses according to the portion of the memory that they belong. In practice, in all the cases we found that the two sets did *not* conflict, and we used a simple merging of the memories.

Unfortunately, this implementation approach cannot coexist with the design for doubling the throughput as described in section 4.1. This is absolutely logical because both improvement approaches exploit the dual port characteristic of the Xilinx memories.

#### 4.4 Further Area and Speed Optimizations

#### 4.4.1 Pipeline

In order to achieve better performance and decrease the area cost we used some techniques that are appicable to all our approaches. Firt of all, we pipelined the whole hashmem path using fine-grained pipeline. This pipelining approach is based on the observation that the minimum amount of logic in each pipeline stage can fit in a 4-input device LUT and its corresponding register. This is a primitive characteristic of the structure of Xilinx CLBs and not only, since many Altera devices have also similar structure. Thus, the resulting operating frequency of this pipelining method is limited only by the latency of one logic cell and the interconnection network. Moreover, there is no area cost overhead, since each logic cell contains both the parts of that minimum logic unit, the LUT and the flip-flop. The only drawback of this method is the big pipeline depth which results in higher latency. However, latency is not critical for our design. As a result, we pipelined this way all the logic units that our implementations include. Thus, we pipelined the CRC generators and the comparators at the end of the path, but also the necessary glue-logic required in some of our designs.

#### 4.4.2 Xilinx SRL16

As already described, the same data that are used in the CRC generator are finally compared to the output data of the pattern memory to detect a match. This means that the data must be registered to achieve the required delay until the process reaches the comparator. Moreover, partitioning wide pattern into shorter ones also requires a delay, which is shown in figure 4.2, in order to determine the overall match. These registers are quite many and also wide which increases a lot the logic cost. The Xilinx SRL16 cell is a customizable up to 16 bits shift register. It is an alternative mode for the look-up tables and as a result it is implemented in single logic cell. Moreover, the output of the shift register may be stored in a flip-flop which improves the total performance and also increases the shifts to 17 [36; 25]. As, a result, we used these SRL16 LUTs in order to minimize the logic cost in the necessary delays whenever possible.

#### 4.5 Upgrading

As we have already commented, an important advantage of our architecture is the ability of adapting to new patterns sets. The CRC generation process is very easy

and fully automated due to software assistance and also the initialization both for the indirection and the pattern memories. Moreover, supposing that the utilization of the memory blocks is quite low, our chances in fitting new search patterns are pretty good. Thus, upgrading our designs with new rulesets is an easy task and in some cases with no extra memory cost, but only with limited increase in logic cost.

# **Chapter 5**

# **Evaluation**

We may measure the quality of an FPGA-based intrusion detection system using performance and area metrics. We measure the performance presenting the operating frequency and calculating the throughput of each implementation ( $throughput = frequency \times inputbits$ ). Moreover, using the information about the logic cost we calculate other metrics in order to show the quality of our designs relatively to other parameters such as the number of intrusion patterns implemented and also the total number of their characters.

In our results, we use the number of Logic Cells, i.e.  $ReportedSlices \times 2$ . The area cost is measured in terms of logic cells needed to match a single character, produced by the ratio of the total logic cells over the total search characters implemented. It is also useful to find a metric that takes into account both performance and area cost. Thus, we used a PerformanceEfficiencyMetric(PEM), as already used by other researchers [5; 6; 14] in order to evaluate designs efficiency. PEM is discribed by the ratio of performance over the area cost, in other words we calculate it dividing the throughput by the logic cells per character. Therefore, it rewards architectures that strike a balance between throughput and area cost. Moreover, since we attempt to strike a different balance between memory and logic usage, it would be also important to have a criterion to tell about the efficiency not only rewarding the designs with less area cost but with less memory usage as well. Therefore, introducing PEM/m as a new performance metric gives us the ability to measure the efficiency of our designs according to both of these parameters. PEM/m comes from the ratio of [PEM/(MEM(kbits)/characters)]/100.

We evaluate the HashMem architecture and our implementations using the official Snort rule set [28] dated early 2004 that consists of 1474 rules and a total of 18,636 characters. We implemented the HashMem architecture in VHDL using the Xilinx ISE 6.2 tools using Spartan 3, Virtex 2 and Virtex2Pro devices, all in the highest speed grades (-5, -6, and -7 respectively). We also used automated tools that given a set of patterns discovered the proper 12-bit polynomials, in order to generate the VHDL code for the CRC generators, and the corresponding mapping of patterns to memories.

At first, we will present our architecture results evaluating and comparing the various implementations as been described in previous sections. At the end we will attempt a comparison, in terms of performance and area, with previously published research.

#### 5.1 The HashMem Architecture Variants

Since, in this first part, we want to demonstrate the evaluation results of the variants of our architecture, we decided to use the same device family for all our variants. This puts us in a better point of view in order to be able to make easier comparisons between these implementations. Thus, we used the synthesis results for Virtex2Pro family, choosing the smallest device possible for each implementation.

#### 5.1.1 Performance and Area Evaluation

Table 5.1 compares the variants of the HashMem architecture for a Virtex2Pro device. The first is the basic architecture that uses a full structure for each of the search pattern widths. This variant is complete and scalable and is implemented in two variants which process one and two characters per cycle respectively. We should also take into consideration that in these two approaches we didn't implement the complete Snort ruleset but only the patterns sets of width from 1 to 32 bytes. However, it is also clear that both designs have a significant logic and an excessive memory cost (181 memory blocks). Still these designs fit in a medium Virtex2Pro device. Moreover, they achieve a quite high operating frequency, 292 and 285 MHz. We notice that it is almost same for both variants, which results

| Design                                  | Input<br>bits | Frequency<br>(MHz) | Throughput<br>(Gbps) | Logic<br>Cells | Pattern<br>chars | LC /<br>char | MEM<br>blocks<br>(kbits) | PEM  | PEM/m |

|-----------------------------------------|---------------|--------------------|----------------------|----------------|------------------|--------------|--------------------------|------|-------|

| HashMem                                 | 8             | 292                | 2.336                | 5,172          | 16.879           | 0.31         | 181<br>(3,258)           | 7.5  | 0.39  |

| nashiwem                                | 16            | 285                | 4.560                | 10,160         | 10,079           | 0.60         |                          | 7.6  | 0.39  |

| HashMem + Reuse                         | 8             | 333                | 2.664                | 2,632          |                  | 0.14         | 66                       | 18.9 | 2.96  |

|                                         | 16            | 322                | 5.152                | 5,219          | 0.28             |              | (1,188)                  | 18.4 | 2.89  |

| HashMem + Reuse +<br>Share              | 8             | 338                | 2.704                | 2,570          | 18,636           | 0.14         | 35 (630)<br>31 (558)     | 19.6 | 5.80  |

| HashMem + Reuse +<br>Share + Small CRCs | 8             | 339                | 2.712                | 2,759          |                  | 0.15         |                          | 18.3 | 6.11  |

Table 5.1: Comparison of the HashMem architecture variants.

in almost double throughput for the two-characters per cycle variant, on order of 4.560 Gbps. Finally, the Performance Efficiency Metric (PEM, i.e. ratio of performance over the logic area cost per character) for both designs is around 7.5, while the new efficiency metric PEM/m that includes the memory cost per character is at 0.39.

Adding memory reuse (+Reuse) for wide patterns reduces the number of memory blocks to 66, and requires only  $\sim$ 2,600 logic cells of logic for processing of a single character per cycle, or 0.14 logic cells per character.Considering that in these two variants we implement the complete Snort ruleset from 1 to 107 character width, both the areac cost and the memory usage show a great improvement against the initial approach. Moreover, at a frequency of  $\sim$ 330MHz, the processing throughput exceeds 2.5 Gbps. Doubling the processing throughput doubles the logic cost, but without additional memory use, as expected. The Performance Efficiency Metric (PEM) for these two designs is around 18.9 and 18.4 respectively, which is  $\sim$ 250% grater than above. Finally, the PEM/m value is much larger than the PEM value, achieving2.96 and 2.89 for the two designs of this variant which is  $\sim$ 7.5 times greater than the previous design.

Adding memory sharing between patterns of different widths (+Share) offers a big improvement in the memory use, reducing the number of required blocks to 35. Again we included the complete Snort ruleset as in the +Reuse variants. We have to remind that in this design we cannot take advantage of the dual-ported memory blocks to double the throughput since the two read ports are used to prerform the memory sharing between patterns of different widths. Thus, we input a

| Design                                  | Input Bits | CRC generators Comparators |     | SRLs | Glue Logic |

|-----------------------------------------|------------|----------------------------|-----|------|------------|

| HashMem + Reuse +<br>Share + Small CRCs | 8          | 32%                        | 42% | 13%  | 13%        |

| HashMem + Reuse +<br>Share              | 8          | 32%                        | 42% | 14%  | 12%        |

| HashMem + Reuse                         | 8          | 32%                        | 42% | 14%  | 12%        |

| Hashivieni + Reuse                      | 16         | 33%                        | 43% | 14%  | 10%        |

Table 5.2: Area utilization ratios.

signle character per cycle. However, the logic cost remains about the same, due to the additional glue logic for the overall match determination. The smaller design size pushes the frequency up to about 340 MHz, slightly increasing the processing throughput to 2.704 Gbps and the PEM value to 19.6. Double than the previous design is also the PEM/m value which shows the improvement rate of sharing memories.

The last line of Table 5.1 uses smaller indirection tables for the smaller pattern widths (3-6). For these widths we can identify CRC polynomials of degree 10 and 11 that provide distinct addresses for all patterns. With fewer address bits the indirection memories use 1 instead of 2 memory blocks (2Kx9 instead of 4Kx9 memory), saving a total of 4 memory blocks. This is our best design, and achieves an operating frequency of  $\sim$ 340MHz at a cost of 0.15 logic cells per character, and a PEM value of 18.3. The area cost of the design is divided as follows: CRC generators 32%, comparators 42%, Glue logic 13% and SRLs 13%. Finally, a slight improvement is also shown in the PEM/m value which supports our claim that this design is the most efficient.

In table 5.2 we present ratio of the area cost utilized by CRC generators, comparators, SRLs and glue logic for the three improved HashMem variants. Furthermore, an overall comparison in performance of the described HashMem variants is figured in the graph in figure 5.1, which plots the frequence and the throughput of each implementation. Moreover the diagram in figure 5.2 compares the area cost in terms of logic cell per character, and also the usage in memory blocks of the 6 variants. Finally, the last two diagrams in figures 5.3 and 5.4 perform a graphical comparison of the PEM and PEM/m values respectively.

Figure 5.1: A plotting diagram that compares the preformance in terms of frequency and throughout.

#### 5.1.2 Area Utilization Analysis

Table 5.3 presents the utilization of the implementations for both the logic cost and the memory usage for the corresponding device. As we can easily notice, in the initial implentation the large number of required memory blocks force us to use a device that has enough memory to accomodate our needs. However, this device has more than enough logic cell available for our design. Things seem to be better when we double the input bits per cycle, where the area utilization is doubled for the same device memory utilization for the same device. Still, the memory utilization of the occupied memory blocks is extremely low, under 5%, which proves the chances we had in reusing the memory blocks for partial pattern detection, described in next line.