## TECHNICAL UNIVERSITY OF CRETE

DIPLOMA THESIS

# Accelerating Fully Homomorphic Encryption (FHE) schemes with FPGAs

Author: Georgios AGORITSIS Thesis Committee: Prof. Sotirios IOANNIDIS Prof. Apostolos DOLLAS Prof. Georgios KARYSTINOS

A thesis submitted in fulfillment of the requirements for the diploma of Electrical and Computer Engineer

in the

School of Electrical and Computer Engineering Microprocessor and Hardware Laboratory

September 13, 2023

#### TECHNICAL UNIVERSITY OF CRETE

## Abstract

#### School of Electrical and Computer Engineering

**Electrical and Computer Engineer**

#### Accelerating Fully Homomorphic Encryption (FHE) schemes with FPGAs

by Georgios AGORITSIS

This thesis delves into the exploration of FPGA acceleration possibilities for Fully Homomorphic Encryption (FHE), focusing on the OpenFHE library. Following a software profiling procedure, the thesis centers its attention on the Number Theoretic Transform (NTT) as a key acceleration point and investigates state-of-the-art optimization techniques from the existing literature. The chosen platform is the Xilinx Alveo U50 FPGA card, with the OpenFHE library as the foundation. The study demonstrates how a hardware-based project designed for the Alveo U50 card can be integrated into OpenFHE. Although this research does not introduce a novel acceleration method, it primarily focuses on showcasing the integration of an application developed in Xilinx Vitis IDE with OpenFHE. An essential contribution is the provision of a functional NTT implementation that supports various NTT sizes, complementing OpenFHE. The implementation encompasses an in-place forward NTT with the Cooley-Tukey butterfly and Harvey's modular multiplication optimization, utilizing High-Level Synthesis (HLS). This work stands as the first hardware accelerator for OpenFHE, deployed on a Xilinx FPGA, supporting up to 2<sup>18</sup>-point Number Theoretic Transforms without FPGA reconfiguration. The accelerator is seamlessly integrated with OpenFHE as a hardware component. While the project does not yield an immediate speedup for OpenFHE, it lays a solid foundation for future acceleration endeavors. Future work directions and optimization suggestions are identified and conclude the thesis.

#### TECHNICAL UNIVERSITY OF CRETE

## Abstract

#### School of Electrical and Computer Engineering

**Electrical and Computer Engineer**

#### Accelerating Fully Homomorphic Encryption (FHE) schemes with FPGAs

#### by Georgios AGORITSIS

Αυτή η εργασία διερευνά τη δυνατότητα χρήσης Αναδιατασσόμενης Λογικής (FPGA) για την επιτάχυνση της Πλήρους Ομομορφικής Κρυπτογράφησης (FHE), εστιάζοντας στη βιβλιοθήκη OpenFHE. Μετά από μια software profiling διαδικασία, η εργασία επικεντρώνεται στο Number Theoretic Transform (NTT) ως κύριο στόχο επιτάχυνσης και διερευνά την υφιστάμενη βιβλιογραφία για υπάρχουσες τεχνικές βελτιστοποίησης. Ως πλατφόρμα υλοποίησης επιλέγεται η FPGA κάρτα Xilinx Alveo U50. Η μελέτη δείχνει τον τρόπο με τον οποίο η υλοποίηση ενός αλγορίθμου στην κάρτα Alveo U50 μπορεί να ενσωματωθεί στο περιβάλλον της OpenFHE. Παρόλο που δεν παρουσιάζεται μια νέα μέθοδος επιτάχυνσης, η εργασία επικεντρώνεται κυρίως στην ενσωμάτωση μιας εφαρμογής που αναπτύχθηκε στο περιβάλλον του Xilinx Vitis IDE με τη βιβλιοθήχη OpenFHE. Στα πλαίσια της εργασίας παρέχεται μια πλήρως λειτουργική υλοποίηση του ΝΤΤ που είναι ισοδύναμη με την υπάρχουσα υλοποίηση του NTT από την OpenFHE. Η υλοποίηση γίνεται σε High-Level Synthesis (HLS) και περιλαμβάνει έναν in-place ευθύ NTT μετασχηματισμό, ο οποίος χρησιμοποιεί την πεταλούδα των Cooley και Tukey, καθώς και την βελτιστοποίηση του modular multiplication από τον D. Harvey. Η παρούσα εργασία περιλαμβάνει τον πρώτο επιταχυντή σε αναδιατασσόμενη λογική για την OpenFHE, που εγκαθίσταται σε μια Xilinx FPGA, υποστηρίζει NTT μεγέθους έως και 218, χωρίς επαναπρογραμματισμό της FPGA και ενσωματώνεται απρόσκοπτα στο περιβάλλον της βιβλιοθήκης. Αν και δεν καταφέρνει να επιταχύνει τη βιβλιοθήκη, θέτει τη βάση για μελλοντικές προσπάθειες επιτάχυνσης. Τέλος, η εργασία ολοχληρώνεται με την πρόταση ιδεών βελτιστοποίησης και κατευθύνσεων για μελλοντικές εργασίες.

## Acknowledgements

First and foremost, I would like to express my gratitude to Prof. Sotirios Ioannidis, my supervisor, for enabling me to work on this thesis and for the unwavering trust he placed in me. I would also like to thank Andreas Brokalakis for his guidance and all his support and availability during the past months. His understanding and contribution were substantial. Special thanks to Prof. Apostolos Dollas and Prof. Georgios Karystinos for being members of the thesis committee and for assessing my work. Last but not least, I would like to thank my family and my friends for the support and encouragement throughout my studies. Their presence, feedback and contribution have shaped me to this day.

> Georgios Agoritsis Chania 2023

## Contents

| Al | ostra      | ct                                                        | iii  |

|----|------------|-----------------------------------------------------------|------|

| Al | Abstract v |                                                           |      |

| A  | cknow      | wledgements                                               | vii  |

| Co | onten      | ts                                                        | ix   |

| Li | st of 3    | Figures                                                   | xi   |

| Li | st of '    | Tables                                                    | xiii |

| Li | st of .    | Algorithms                                                | xv   |

| Li | st of .    | Abbreviations                                             | xvii |

| 1  | Intr       | oduction                                                  | 1    |

|    | 1.1        | Motivation                                                | 1    |

|    | 1.2        | Scientific Contributions                                  | 3    |

|    | 1.3        | Thesis Outline                                            | 4    |

| 2  | The        | oretical Background                                       | 5    |

|    | 2.1        | Learning With Errors (LWE) and Lattice-based Cryptography | 5    |

|    | 2.2        | Fully Homomorphic Encryption (FHE) and FHE Schemes        | 6    |

|    | 2.3        | Modular Arithmetic                                        | 9    |

|    | 2.4        | Residue Number System (RNS)                               | 10   |

|    | 2.5        | Number Theoretic Transform (NTT)                          | 11   |

|    | 2.6        | OpenFHE Open-source Library                               | 19   |

| 3  | Rela       | ated Work                                                 | 25   |

|    | 3.1        | Accelerating FHE Schemes                                  | 25   |

|    | 3.2        | The FPGA Perspective                                      | 26   |

|    | 3.3        | Thesis Approach                                           | 28   |

| 4  | Def    | ining tl | he Architecture                               | 29 |

|----|--------|----------|-----------------------------------------------|----|

|    | 4.1    | Open     | FHE Library Profiling                         | 29 |

|    | 4.2    | Accele   | eration Target                                | 32 |

|    | 4.3    |          | t Architecture                                | 36 |

| 5  | FPG    | A Imp    | lementation                                   | 39 |

|    | 5.1    | Tools    | Used                                          | 39 |

|    |        | 5.1.1    | Vitis IDE                                     | 39 |

|    |        | 5.1.2    | High Level Synthesis (HLS)                    | 40 |

|    |        | 5.1.3    | Vitis pragmas and optimizations               | 41 |

|    | 5.2    | FPGA     | Platform                                      | 42 |

|    | 5.3    | Desig    | n Space Exploration                           | 43 |

|    | 5.4    | NTT A    | Accelerator Design                            | 49 |

|    |        | 5.4.1    | Host Code Design                              | 50 |

|    |        | 5.4.2    | Kernel Code Design                            | 51 |

|    | 5.5    | Integr   | ration with OpenFHE                           | 52 |

|    |        | 5.5.1    | Generating an .so file using Xilinx Vitis IDE | 53 |

|    |        | 5.5.2    | Configuring OpenFHE                           | 54 |

| 6  | Res    | ults     |                                               | 57 |

|    | 6.1    | FPGA     | Resource Utilization and Performance          | 57 |

|    | 6.2    | Perfor   | rmance Evaluation                             | 61 |

| 7  | Con    | clusior  | ns and Future Work                            | 69 |

|    | 7.1    | Concl    | usions                                        | 69 |

|    | 7.2    | Futur    | e Work                                        | 70 |

| A  | Ope    | enFHE    | Modified Source Code                          | 73 |

| Re | eferei | nces     |                                               | 77 |

# **List of Figures**

| 2.1 | Cooley-Tukey Butterfly                                       | 15 |

|-----|--------------------------------------------------------------|----|

| 2.2 | Gentleman-Sande Butterfly                                    | 15 |

| 2.3 | Forward 8-point NTT with Cooley-Tukey (CT) butterfly         | 16 |

| 2.4 | Inverse 8-point NTT with Gentleman-Sande (GS) butterfly      | 16 |

| 4.1 | Function execution time % out of C++ code total execution    |    |

|     | time (1/2)                                                   | 31 |

| 4.2 | Function execution time % out of C++ code total execution    |    |

|     | time (2/2)                                                   | 31 |

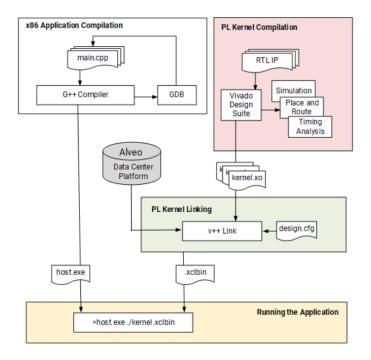

| 5.1 | Xilinx Vitis Development Flow                                | 39 |

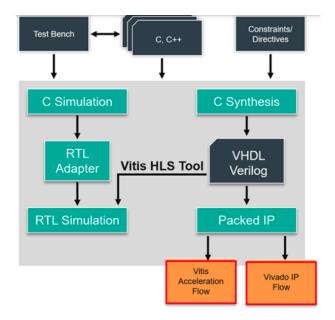

| 5.2 | Xilinx Vitis HLS Development Flow                            | 40 |

| 5.3 | Xilinx Alveo U50 Data Acceleration Card                      | 43 |

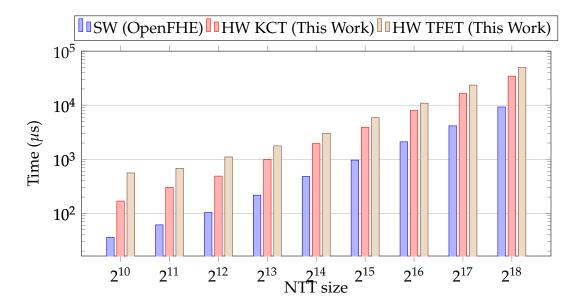

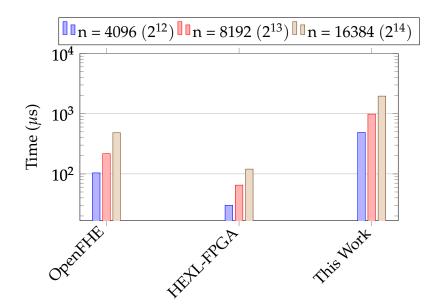

| 6.1 | Performance comparison of software NTT function call (OpenFH | E) |

|     | and hardware NTT function call (This Work). For the hard-    |    |

|     | ware NTT function call the Kernel Computation Time (KCT)     |    |

|     | and Total Function Execution Time (TFET) are included        | 63 |

| 6.2 | Comparison of NTT implementations (NTT computation time      |    |

|     | only)                                                        | 63 |

## List of Tables

| 4.1 | A comparison of existing NTT accelerators with OpenFHE sup-   |    |

|-----|---------------------------------------------------------------|----|

|     | ported parameters                                             | 34 |

| 4.2 | Target platforms and resource utilization of existing NTT ac- |    |

|     | celerators                                                    | 36 |

| 5.1 | Available resources of Xilinx Alveo U50 FPGA                  | 43 |

| 5.2 | Design Space Exploration Resource Utilization Results         | 48 |

| 5.3 | Design Space Exploration Latency Results                      | 49 |

| 5.4 | Target Design Resource Utilization Results                    | 49 |

| 5.5 | Target Design Latency Results                                 | 49 |

| 5.6 | Deployed HLS Pragmas in algorithm 10                          | 52 |

| 6.1 | Alveo U50 Post-Route Resource Utilization                     | 57 |

| 6.2 | NTT Hardware Accelerator Timing Results (KC(%) and DT(%)      |    |

|     | correspond to the percentage of Kernel Computation Time and   |    |

|     | Data Transfer Time out of the Total Function Execution Time   |    |

|     | respectively)                                                 | 59 |

| 6.3 | Program Device Latency                                        | 59 |

| 6.4 | Results and comparison for NTT implementations of size $n =$  |    |

|     | 4096                                                          | 60 |

| 6.5 | Performance of Software NTT (OpenFHE)                         | 61 |

| 6.6 | Performance comparison of Software NTT time (NTT function     |    |

|     | included in OpenFHE library) and Hardware NTT time (ker-      |    |

|     | nel computation, data transfers, total hardware function exe- |    |

|     | cution time)                                                  | 62 |

| 6.7 | Power Consumption and Energy Efficiency comparison of a       |    |

|     | FHE application when NTTs are launched only in Software       |    |

|     | (SW OpenFHE - SW NTT case) and when NTTs are launched         |    |

|     | on the FPGA (SW OpenFHE - HW NTT case) - OpenFHE in           |    |

|     | both cases is launched on Software                            | 66 |

# List of Algorithms

| 1  | Montgomery Modular Multiplication                 | 9  |

|----|---------------------------------------------------|----|

| 2  | Barrett Modular Multiplication                    | 10 |

| 3  | Plantard Modular Multiplication                   | 10 |

| 4  | In-Place Cooley-Tukey Forward NTT                 | 17 |

| 5  | In-Place Gentleman-Sande Inverse NTT              | 18 |

| 6  | Harvey/Shoup Cooley-Tukey Butterfly               | 18 |

| 7  | OpenFHE's In-Place Forward CT-NTT                 | 33 |

| 8  | OpenFHE's Harvey Modular Multiplication           | 34 |

| 9  | HLS-friendly NTT algorithm with GS-butterfly [40] | 45 |

| 10 | Implemented HLS-friendly CT-NTT                   | 47 |

## **List of Abbreviations**

| ASIC | Application Specific Integrated Circuit |

|------|-----------------------------------------|

| BRAM | Block Random Access Memory              |

| CC   | Clock Cycle                             |

| CPU  | Central Processor Unit                  |

| CS   | Computer Science                        |

| CRT  | Chinese Remainder Theorem               |

| DRAM | Dynamic Random Access Memory            |

| DSP  | Digital Signal Processor                |

| DTT  | Data Transfer Time                      |

| FF   | Flip Flops                              |

| FHE  | Fully Homomorphic Encryption            |

| FPGA | Field Programmable Gate Array           |

| GPU  | Graphic Processor Unit                  |

| HBM  | High Bandwidth Memory                   |

| HDL  | Hardware Description Language           |

| HLS  | High Level Synthesis                    |

| KL   | Kernel Latency                          |

| KCT  | Kernel Computation Time                 |

| LUT  | Look Up Table                           |

| NTT  | Number Theoretic Transform              |

| TFET | Total Function Execution Time           |

| PL   | Programmable Logic                      |

| RAM  | Random Access Memory                    |

| SDK  | Software Development Kit                |

| SRL  | Shift Register Logic                    |

| URAM | Ultra Random Access Memory              |

|      |                                         |

Dedicated to my family and friends...

## Chapter 1

## Introduction

### 1.1 Motivation

Cryptography plays a vital role in safeguarding the security and confidentiality of sensitive data across diverse applications. One of the most groundbreaking advancements in cryptography is Fully Homomorphic Encryption (FHE) [12], an encryption scheme that allows users to perform computations on encrypted data without decrypting it. This remarkable property opens up a wide range of possibilities for secure computation in scenarios where privacy is of utmost importance.

The history of FHE dates back to the early 1970s when researchers began exploring the possibility of performing computations on encrypted data. However, it wasn't until Craig Gentry's groundbreaking work in 2009 [24] that FHE became a practical reality. Gentry introduced the concept of bootstrapping, which enabled the evaluation of arbitrary circuits on encrypted data, thus overcoming the limitations of earlier attempts. His work opened up new avenues for secure data processing and sparked widespread interest in FHE research and development.

FHE finds application in numerous domains where data privacy is paramount. Industries such as healthcare, finance, cloud computing, and machine learning can benefit from secure data processing without compromising confidentiality. FHE enables secure outsourcing of computations, confidential data sharing, and privacy-preserving machine learning algorithms.

Several FHE schemes have been developed over the years, including the Brakerski-Gentry-Vaikuntanathan (BGV) scheme [8], the Brakerski/ Fan- Vercauteren (FV) scheme [21], [7], and the Cheon-Kim-Kim-Song (CKKS) scheme [13]. Each scheme has its own strengths and is suited to different types of applications and performance requirements. The underlying mathematical problem that powers most of FHE schemes is the Ring Learning With Errors (RLWE) problem [9]. RLWE provides a foundation for constructing secure and efficient FHE schemes, allowing computations to be performed on encrypted data while maintaining the security guarantees.

To make FHE practical and viable for real-world applications, software libraries implementing FHE have been developed. These libraries provide high-level abstractions and tools for working with FHE schemes, making it easier for developers to integrate FHE into their applications. Examples of existing FHE libraries include OpenFHE [2], Palisade [50] (the predecessor of OpenFHE), and Microsoft SEAL [56].

OpenFHE is a state-of-the-art open-source software library specifically designed to facilitate the use and development of FHE applications. It provides a comprehensive set of tools and functionalities for working with various FHE schemes, including key generation, encryption, and decryption operations, while it also complies with the Homomorphic Encryption postquantum security standards [33]. OpenFHE aims to make FHE accessible and usable for developers, researchers, and practitioners, promoting collaboration and innovation in the field of secure data processing.

While software libraries like OpenFHE make the use of FHE schemes easily accessible to developers, performance issues remain as an adoption obstacle. FHE schemes encrypt plaintexts into high degree polynomials and perform computations over these polynomials, thus increasing the complexity of computations. Number Theoretic Transform (NTT) [38] has been proposed as a way to reduce the complexity of polynomial multiplication from  $O(n^2)$  to  $O(n \log n)$  and has been widely adopted throughout the FHE schemes as a fundamental computational primitive. Indeed, by using performance analysis tools [34], we identified that NTT computations account for more than 30% of the overall computation time in typical scenarios.

In an effort to address the performance issues that plague the adoption of FHE schemes, this work conducts a feasibility study on using reconfigurable hardware accelerators to offload computationally-significant functions of the OpenFHE library. According to our performance measurements, a natural starting point is the offloading of the NTT computations. Our goal is to create hardware accelerated functions that are fully functional and equivalent to those included in the OpenFHE library (i.e. without limitations on specific data sizes or operations) and integrate them in the library in a manner that

developers who employ the OpenFHE library need not be aware of the complications or other issues related to using hardware accelerators. As such, we hope that our work can be used as a reference point for future works targeting OpenFHE library acceleration using Xilinx FPGAs.

In conclusion, Fully Homomorphic Encryption (FHE) has the potential to transform data privacy and security by enabling computations on encrypted data. With the development of schemes such as BGV, FV, and CKKS, FHE is finding applications in various domains. Existing software libraries, such as OpenFHE, provide valuable resources for FHE implementation and development. The integration of FPGA-based accelerators with the OpenFHE library can potentially open up new possibilities for accelerating FHE computations. This work is the first attempt of accelerating the NTT used in OpenFHE with the Xilinx FPGAs (more specifically Xilinx Alveo U50) without any functional limitations.

## **1.2** Scientific Contributions

We use Intel HEXL-FPGA [35] and the work of Mert et al. [40] as the starting point of our work. Our target platform is Xilinx Alveo U50 Data Center Accelerator Card. The goal of this thesis is to design a functional NTT accelerator on Alveo U50 and integrate it with OpenFHE [2]. Our work is the first attempt to accelerate OpenFHE using a Xilinx Alveo FPGA to the best of our knowledge and can be used for future work as a template to further optimize OpenFHE acceleration. In more details:

- We confirm that NTT can be a bottleneck operation in OpenFHE, due to multiple NTT transformations used in internal high-level functions. Note that the NTT is a critical component among all FHE high-level functions and is the starting point of any existing FHE accelerator.

- We provide an alternative way of integrating our design with OpenFHE library, instead of using the library's Hardware Abstraction Layer (HAL), to simplify hardware acceleration research on OpenFHE.

- We provide a functional and OpenFHE-equivalent NTT implementation supporting NTT sizes up to 2<sup>18</sup> in Xilinx Vitis HLS, using and combining existing work for NTT in literature, in order to create a baseline for future research.

• We identify further optimization approaches and future work directions at the last chapters of this document.

## 1.3 Thesis Outline

- **Chapter 2 Theoretical Background:** Chapter 2 provides the necessary theoretical background concepts related to the goal of this thesis.

- **Chapter 3 Related Work:** Chapter 3 provides a brief overview of existing works in literature and the thesis approach.

- **Chapter 4 Defining the Architecture:** Chapter 4 includes OpenFHE library software profiling results and presents the proposed accelerator's architecture.

- **Chapter 5 FPGA Implementation:** Chapter 5 report on the FPGA-based design and implementation of the proposed accelerator.

- **Chapter 6 Results:** Chapter 6 reports the performance and resource utilization results of the proposed FPGA design.

- **Chapter 7 Conclusions:** Chapter 7 concludes the thesis and provides the final conclusions, alongside proposals for future work directions.

## Chapter 2

## **Theoretical Background**

## 2.1 Learning With Errors (LWE) and Lattice-based Cryptography

**Learning With Errors (LWE)** [9] is a lattice-based cryptographic problem that was introduced in 2005 and forms the basis of many homomorphic encryption schemes, including FHE. In the LWE problem, one must find a small integer secret vector hidden within a set of noisy linear equations. These equations introduce errors to make it computationally difficult to recover the secret vector from the noisy data.

The problem formulation is as follows:

$$c[i] = (a[i], a[i] * s + e[i]) \mod q$$

for  $i = 0, 1, 2, ...$

where:

c[i] is a ciphertext,

a[i] is a random vector chosen uniformly from a discrete set,

s is the secret vector (small integer vector) that the adversary aims to find,

e[i] is a small noise term,

*q* is a large modulus.

The noise term e[i] is generated from a probability distribution, and it is what adds the "noise" to the equations. The LWE problem involves finding the secret vector *s* from a collection of such noisy equations.

LWE has a search version and a decision version:

- Search LWE problem: Given a set of computed pairs of points (*a*[*i*], *a*[*i*] \* *s* + *e*[*i*]), find *s*.

- Decision LWE problem: Given a set of computed pairs of points (*a*[*i*], *a*[*i*] \* *s* + *e*[*i*]) and some random points, determine the points that originate from *s*. The random points are generated using a uniform distribution.

The main challenge in the LWE problem is that the noise terms make it computationally difficult to directly recover the secret vector s. The security of LWE relies on the assumption that solving the system of equations and extracting the secret vector s is hard even for powerful adversaries.

LWE has been widely used to demonstrate the security of various cryptosystems. However, their efficiency is limited by the fact that their keys are matrices randomly generated over a small integer q in the ring  $Z_q$ , causing their dimension to increase linearly as security parameters grow. To address this efficiency concern, ring variants have been introduced.

In 2009, a variant of LWE called **Ring Learning with Errors (Ring-LWE)** was proposed as a solution [9]. RLWE extends the LWE problem to polynomial rings. Instead of using vectors, RLWE operates on polynomials within a ring, such as the polynomial ring modulo a power of two. The RLWE problem involves finding the secret polynomial amidst errors introduced through the polynomial ring.

One significant advantage of Ring-LWE over its LWE counterpart is the reduction in key size by a factor of *n*. For a message that would require several thousand bits to be secured using LWE, Ring-LWE accomplishes the same with only hundreds of bits. This makes Ring-LWE a more feasible and efficient system, especially for implementations with constrained computational resources. OpenFHE uses Ring-LWE as its main security guarantee.

## 2.2 Fully Homomorphic Encryption (FHE) and FHE Schemes

Fully Homomorphic Encryption (FHE), is an encryption scheme that allows users to perform computations on encrypted data without decrypting it. Whilst FHE was initially introduced in the 1970s, it was in 2009 that Craig Gentry [24] proved that FHE can be used in practise. Starting from a Somewhat Homomorphic Encryption (SWHE) scheme, Gentry proved how it can be transformed in a FHE scheme using the bootstrapping technique [8]. In SWHE schemes one can evaluate a ciphertext in the form of a low-degree polynomial until the noise increases up to a point that any further operation on the ciphertext will make it undecryptable. In a FHE scheme, the ciphertext can be a polynomial of any size and boostrapping is used as a noise maintenance technique, to allow more computations on the encypted data.

Bootstrapping can be defined as a ciphertext refresh operation that reduces the generated noise into levels that allow more operations to be performed [66]. In schemes like CKKS, bootstrapping is performed in a periodic manner [10] and is a memory and compute intensive operation. In schemes like CGGI, bootstrapping is performed after each bit-wise operation. As bootstrapping can be a bottleneck operation for FHE, a great part of the community has focused in accelerating this high level function, and the main focus usually is the intensive memory access required by the algorithm. Following their existing work [10], the same research team recently proposed an FPGA accelerator that supports bootstrapping [1] by optimizing the required memory access pattern.

Following Gentry's work, multiple FHE schemes have been proposed in literature, the Brakerski-Gentry-Vaikuntanathan (BGV) [8], the Fan-Vercauteren (FV) [7], the Cheon-Kim-Kim-Song (CKKS) [13] and the Chillotti - Gama -Georgieva - Izabachene (CGGI) [14] schemes to name the most important. Choosing the right FHE scheme for an application depends on both the application (machine learning computations, encrypted queries in databases, etc.) and the data type used in the application (integer numbers, floating point numbers, etc.).

Grouping FHE schemes based on the supported data type, three classes of schemes are formed [2]. The first include the BGV and BFV schemes and support modular arithmetic over finite fields in the form of vectors of integers modulo a number. The second group include among others the CGGI scheme and support boolean circuits. The third and most recent group is the one that comprises of the CKKS scheme. In this scheme, vectors of real and complex numbers are supported, enabling approximate computations. All these groups, are based on the hardness of the RLWE problem [9], due to the noise added during homomorphic operations, such as encryption and key generation.

Plaintexts in FHE depend on the scheme used and can have the form of vectors of integers, vectors of real/complex numbers or boolean values. A parameter p, called the plaintext modulo, is also defined based on the worst multiplication scenario of the dataset. This parameter is later used to define the ciphertext modulo q, which is used internally in FHE operations. The bigger the ciphertext modulo, the more operations can be performed on the ciphertext without using bootstrapping. Ciphertexts are arrays of hundreds or thousands of integers in all schemes that map to polynomial coefficients, which means that plaintexts are encrypted into polynomials and the size of the polynomials is a power of two, typically in the range  $[2^{10}, 2^{17}]$ . In FHE, the basic mathematical structure used is a polynomial ring (denoted by  $R_a$ ) of dimension  $n = \phi(m)$ , where *m* is the index of the m - th cyclotomic polynomial,  $\phi$  is Euler's totient function, and *q* is the coefficient modulus of the ring. *n*,*m*, and *q* are all positive integers. One can view this ring as the set of polynomials of degree less than n with integer coefficients in  $\{-q/2, \ldots, q/2\}$ . The nature of the ciphertexts pose a challenge for FHE on its own, due to the fact that polynomial arithmetic can be expensive as the polynomial size increases.

To tackle this challenge, multiple techniques are used. Regarding modular arithmetic, efficient modular reduction algorithms such as Barrett reduction [26] or Montgomery reduction [41] have been proposed. To accelerate the main bottleneck, the polynomial multiplication, the Number Theoretic Transform (NTT) [38] has been used. There is a great variety of NTT algorithm optimizations in the literature [39], [32], [53], [51]. Using the NTT, the complexity of polynomial multiplication is reduced from  $O(n^2)$  to  $O(n \log n)$ . To further accelerate the NTT and its efficiency, a Residue Number System (RNS) representation is used on the initial polynomial [25]. This means, that multiple polynomials with smaller coefficients are calculated and NTTs can be performed in parallel. The set of RNS calculated polynomials represent the original polynomial. The main advantage of this approach is that it can bound arithmetic to be performed for example in 64 bits variables without overflow, regardless of the initial coefficient bit requirements (that can be up to multiple hundreds bits). All these approaches have been integrated in all state-of-the-art software libraries available.

### 2.3 Modular Arithmetic

A key component of lattice-based cryptography and hence FHE, is the modular arithmetic operations. Among those modular arithmetic operations, the modular multiplication is of specific interest. That is due to the fact that multiplication greatly increases the size of the result which often exceeds the target modulo, thus modular reduction will be applied more frequently during multiplication compared to modular addition. In addition, the Number Theoretic Transform (NTT), one of the main bottlenecks for FHE, utilizes modular multiplication to form its result. Consequently, modular reduction techniques are of specific interest for FHE, the most important of which include the Montgomery modular multiplication [43], the Barrett modular multiplication [26] and a recently proposed algorithm from Plantard [48]. Plantard's publication also includes an overview of a variety of modular reduction algorithms for unsigned arithmetic. Modular reduction algorithms for signed arithmetic have also been proposed [4]. Below, we present Montgomery (algorithm 1), Barrett (algorithm 2) and Plantard (algorithm 3) modular multiplication algorithms.

A common approach between these methods is using the fact that multiplications and divisions with powers of two are implemented using bit-shift operations in hardware. In addition, the mod operation can be viewed as a bit masking operation that maintains only the target bits of a word. Regarding Montgomery's method, one of the most used algorithms for modular multiplication [48], its result is scaled by the factor  $2^{-n}$ . On the contrary, Barrett's method returns directly the correct result, but is slightly more expensive than Montgomery multiplication in terms of computational resources.

#### Algorithm 1 Montgomery Modular Multiplication

**Require:** X, Y (0 < X, Y < q) as input values. q is an odd modulus ( $q < 2^n$ ). R such that  $R = (-P^{-1}) \pmod{2^n}$ . **Ensure:**  $Z = XY2^{-n} \pmod{q}, (0 \le Z \le q)$ . **function** MONTGOMERYMODMUL(X, Y, R, q, n)  $Z \leftarrow (XY + q \cdot (XYR \pmod{2^n}))/2^n$  **if**  $Z \ge q$  **then**   $Z \leftarrow Z - q$ **return** Z

Plantard's method is in fact a special case of the Montgomery modular multiplication [4], which operates on 2n-bit words and computes the multiplication result in a *n*-bit word, taking advantage of the property that 2n-bit word

#### Algorithm 2 Barrett Modular Multiplication

**Require:** X, Y (0 < X, Y < q) as input values. *q* is a modulus. *R* such that  $R = \lfloor 2^{2n}/q \rfloor$ . **Ensure:**  $Z = XY \pmod{q}, (0 \le Z \le q)$ . **function** BARRETTMODMUL(X, Y, R, q, n)  $Z \leftarrow (XY - q \cdot (((XY)/2^{n-1})R)/2^{n+1}))$  **if**  $Z \ge 2q$  **then**   $Z \leftarrow Z - 2q$  **else if**  $Z \ge q$  **then**   $Z \leftarrow Z - q$ **return** Z

multiplication can be viewed as a modular multiplication modulo  $2^{2n}$ . In Plantard modular multiplication, one less multiplication is performed compared to Montgomery's method.

#### Algorithm 3 Plantard Modular Multiplication

**Require:** X, Y (0 < X, Y < q) as input values. *q* is a modulus. *R* such that  $R = q^{-1} \pmod{2^{2n}}$ . **Ensure:**  $Z = XY(-2^{-2n}) \pmod{q}, (0 \le Z \le q)$ . **function** PLANTARDMODMUL(*X*, *Y*, *R*, *q*, *n*)  $Z \leftarrow \lfloor (q \cdot (\lfloor XYR \pmod{2^{2n}}/2^n \rfloor + 1)/2^n \rfloor$  **if** Z = q **then**   $Z \leftarrow Z - q$ **return** *Z*

### 2.4 Residue Number System (RNS)

When polynomial multiplication is studied, the Residue Number System (RNS) representation is the starting point of any acceleration attempt. An introduction to the properties of the RNS can be found at [22]. In the RNS domain, a polynomial with coefficients modulo Q is decomposed into multiple polynomials with coefficients modulo  $q_i$  for i = 0, 1, 2, ... In other words, the moduli  $q_i$  are chosen so as  $Q = \prod(q_i)$  for i = 0, 1, 2, ... The foundation of the RNS system is the Chinese Remainder Theorem [45]. Operations such as addition, subtraction and multiplication can be performed for every  $q_i$  in parallel, as:

$$[c_1, c_2, c_3] = [(a_1 \oplus b_1) modq_1, (a_2 \oplus b_2) modq_2, (a_3 \oplus b_3) modq_3]$$

where  $\oplus$  is one of the following operations [+, -, \*].

Choosing the smaller moduli  $q_i$  values is also important and depends on the effective range of numbers that the initial modulo Q covers. A great effort has been put in studying what are the best candidates for a moduli set selection. [45] includes a summary of different moduli sets found in the literature up to 2011. While more recent works have been published, we do not focus more on it, as choosing a moduli set was out of the scope of this thesis.

### 2.5 Number Theoretic Transform (NTT)

The Number Theoretic Transform (NTT) is a special case of the Discrete Fourier Transform (DFT) over finite fields [49] and it is also used to efficiently compute the polynomial multiplication between high degree polynomials [38]. That is due to the fact that using the NTT the complexity of polynomial multiplication drops from  $O(n^2)$  to  $O(n \log n)$ . A comprehensive review of NTT and state-of-the-art optimizations can be found at [55]. Prior to explaining the NTT, we describe the polynomial multiplication over the rings  $\mathbb{Z}_q[X], \mathbb{Z}_q[X]/(X^n - 1), \mathbb{Z}_q[X]/(X^n + 1)$  and then we will also define the primitive n - th root of unity.

Let A(x) and B(x) be two polynomials of degree n - 1 in the ring  $R_q = \mathbb{Z}_q[X]$ :

$$A(x) = a_0 + a_1 x + \dots + a_{n-2} x^{n-2} + a_{n-1} x^{n-1}$$

$$B(x) = b_0 + b_1 x + \dots + b_{n-2} x^{n-2} + b_{n-1} x^{n-1}$$

The polynomial multiplication is defined as:

$$C(X) = A(X) \cdot B(X) = \sum_{k=0}^{2n-2} c_k x^k$$

where  $c_k = \sum_{i=0}^k a_i b_{k-i} \pmod{q} \in \mathbb{Z}_q[X]$ . Thus, polynomial multiplication can also be viewed as the linear convolution between the coefficients of A(x) and B(x). In addition to the linear convolution, the cyclic convolution and the negacyclic convolution should also be defined.

For the cyclic convolution, consider that A(x) and B(x) are again two polynomials of the same degree, but in the  $R_q = \mathbb{Z}_q[X]/(X^n - 1)$  ring. Then, the

polynomial multiplication is defined as:

$$C(X) = A(X) \cdot B(X) = \sum_{k=0}^{n-1} c_k x^k$$

where  $c_k = \sum_{i=0}^k a_i b_{k-i} + \sum_{i=k+1}^{n-1} a_i b_{k+n-i} \pmod{q} \in \mathbb{Z}_q[X]/(X^n - 1).$

The negacyclic convolution for A(x) and B(x) is defined in the ring  $R_q = \mathbb{Z}_q[X]/(X^n + 1)$  instead.

$$C(X) = A(X) \cdot B(X) = \sum_{k=0}^{n-1} c_k x^k$$

where  $c_k = \sum_{i=0}^k a_i b_{k-i} - \sum_{i=k+1}^{n-1} a_i b_{k+n-i} \pmod{q} \in \mathbb{Z}_q[X]/(X^n+1).$

To form the cyclic or the negacyclic convolution of C(x), where C(x) is the result of the linear convolution, one has to perform a modular reduction using  $(x^n - 1)$  or  $(x^n + 1)$  respectively:

$$C(x)_{cyclic} = C(x) \mod (x^n - 1)$$

$C(x)_{negacyclic} = C(x) \mod (x^n + 1)$

Regarding the primitive n - th root of unity, we follow the definition provided by [55]. Note that a ring can have multiple primitive n - th roots of unity.

Definition 2.1: Let  $\mathbb{Z}_q$  be an integer ring modulo q, and n - 1 the polynomial degree of the aforementioned polynomials A(x) and B(x). Define  $\omega$  as primitive n - th root of unity in  $\mathbb{Z}_q$  if and only if:

$$\omega^n \equiv 1 \pmod{q}$$

and

$$\omega^k \not\equiv 1 \pmod{q}$$

for k < n.

For the forward cyclic NTT, let  $a(x) = a_0 + a_1x + \ldots + a_{n-2}x^{n-2} + a_{n-1}x^{n-1} \in \mathbb{Z}_q[X]/(X^n - 1)$  be our polynomial of degree n - 1 and  $\omega$  a primitive n - th root of unity in  $\mathbb{Z}_q[X]$ .

$$\hat{a} = NTT(a)$$

where  $\hat{a}_i = \sum_{j=0}^{n-1} a_j \omega^{ij} \mod q$  for  $i = 0, 1, \dots, n-1$

The inverse cyclic NTT can be defined as:

$$a = INTT(\hat{a})$$

where  $a_i = \frac{1}{n} \sum_{j=0}^{n-1} \hat{a}_j \omega^{-ij} \mod q$  for  $i = 0, 1, ..., n-1$

The polynomial multiplication of A(x) and B(x) using the NTT is defined as:

$$C(x) = INTT(NTT(A(x)) \cdot NTT(B(x))) \in \mathbb{Z}_{q}[X]/(X^{n}-1)$$

where  $\cdot$  represents the coefficient-wise multiplication between each coefficient of the initial polynomials. Note that the result of the cyclic transforms is in  $\mathbb{Z}_q[X]/(X^n - 1)$ , while FHE operates in  $\mathbb{Z}_q[X]/(X^n + 1)$ , mentioned as  $R_q$  in section 2.2. In order for the polynomial multiplication to produce a result in the  $\mathbb{Z}_q[X]/(X^n + 1)$  ring, a negacyclic NTT transform has to be used.

In the negacyclic NTT the primitive 2n - th root of unity in  $\mathbb{Z}_q$  must be defined as:

$$\psi^{2n} \equiv 1 \pmod{q}$$

The following property must also be true:

$$\psi^2 \equiv \omega \pmod{q}$$

To perform the negacyclic polynomial multiplication, one has to multiply each coefficient of the initial polynomials A(x) and B(x) with a power of  $\psi$ . Powers of  $\psi$  are also called twiddle factors. The modified polynomials are:

$$A'(x) = a_0 + \psi a_1 x + \ldots + \psi^{n-2} a_{n-2} x^{n-2} + \psi^{n-1} a_{n-1} x^{n-1}$$

$$B'(x) = b_0 + \psi b_1 x + \ldots + \psi^{n-2} b_{n-2} x^{n-2} + \psi^{n-1} b_{n-1} x^{n-1}$$

and the negacyclic polynomial multiplication is now computed as:

$$C(x) = (1, \psi^{-1}, \dots, \psi^{-(n-1)}) \cdot INTT(NTT(A'(x)) \cdot NTT(B'(x)))$$

where  $C(x) \in \mathbb{Z}_q[X]/(X^n + 1)$  and  $\cdot$  represents the coefficient-wise multiplication between each coefficient of the polynomials and between the multiplied coefficients and the inverse powers of  $\psi$ . In other words, the negacyclic forward NTT can be defined as:

$$\hat{A} = NTT^{\psi}(A)$$

where  $\hat{a}_i = \sum_{j=0}^{n-1} a_j \psi^i \omega^{ij} \mod q$  for  $i = 0, 1, \dots, n-1$

and the inverse negacyclic NTT as:

$$A = INTT^{\psi}(\hat{A})$$

where  $a_i = \frac{1}{n} \sum_{j=0}^{n-1} \hat{a}_j \psi^{-i} \omega^{-ij} \mod q$  for  $i = 0, 1, ..., n-1$

Following the naive approach, multiple optimizations have been proposed in literature [39]. To avoid multiplying each input coefficient with the appropriate power of  $\psi$  and then performing the NTT, Roy et al. [53] proposed that powers of  $\psi$  can be merged with the powers of  $\omega$  as  $\psi^i \omega^{ij} = \psi^{2ij+i}$ , using the property  $\psi^2 \equiv \omega \pmod{q}$ . The negacyclic NTT can now be defined as:

$$\hat{A} = NTT^{\psi}(A)$$

where  $\hat{a}_i = \sum_{j=0}^{n-1} a_j \psi^{2ij+i} \mod q$  for  $i = 0, 1, ..., n-1$

A similar optimization is available due to Pöppelmann et al. [51] for the inverse negacyclic NTT, which can now be defined as:

$$A = INTT^{\psi}(\hat{A})$$

where  $a_i = \frac{1}{n} \sum_{j=0}^{n-1} \hat{a}_j \psi^{-(2ij+i)} \mod q$  for  $i = 0, 1, ..., n-1$

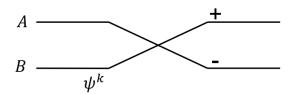

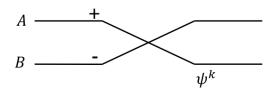

To further accelerate the NTT, a divide and conquer technique was proposed by Cooley and Tukey [16] in 1965 and is called Cooley-Tukey (CT) butterfly (figure 2.1) in literature. The turning point of their work was using the same power of  $\psi$  in two calculations, thus reducing the number of calculations in the entire NTT. Terms like  $(A - \psi^k B)$  and  $(A + \psi^k B)$  are calculated once and used by other butterfly units as the transform progresses. Using the CT butterfly is possible as long as *n* is a power of two for a n-point NTT.

FIGURE 2.1: Cooley-Tukey Butterfly.

A similar technique, mainly applied to the inverse NTT, was published by Gentleman and Sande [23] in 1966 and is called Gentleman-Sande (GS) buttefly (figure 2.2) in literature.

FIGURE 2.2: Gentleman-Sande Butterfly.

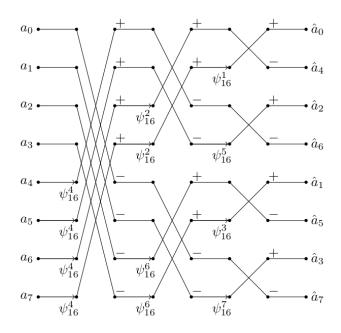

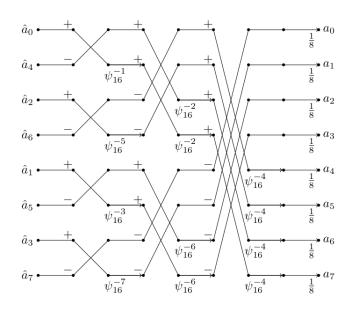

Using many butterflies, one can form high-degree NTT and INTT transforms. We refer the reader to figures 2.3 and 2.4, where a 8-point forward CT-based NTT and a 8-point GS-based INTT are displayed. Note that both transforms use the powers of  $\psi$  in the way proposed by Roy et al. [53] and Pöppelmann et al. [51].

An important remark on the below figures is the order of the input and output coefficients. One can notice that in the case of CT-based forward NTT the input is in normal order, while the output's order is mixed. On the contrary, the GS-based inverse NTT has its input in mixed order and the output in normal order. In literature, researchers refer to this mixed order as bit-reversed order [6] [55] [38]. The bit-reversed order applies to the index *i* used to access each coefficient in the coefficient vector  $[a_0, a_1, \ldots, a_{n-1}]$ . For an index *i* with binary representation  $0bi_0i_1 \ldots i_{log_2(n)}$  this process can be defined as:

$$BitReverse(0bi_0i_1\ldots i_{log_2(n)}) = 0bi_{log_2(n)}i_{log_2(n)-1}\ldots i_1i_0$$

For example, for the 8-point NTT transform (n = 8), index 0 in binary is 0*b*000 and in bit-reversed representation is 0*b*000 = 0*d*0, while index 1 in binary representation is 0*b*001 and in bit-reversed representation is 0*b*100 = 0*d*4, and so on.

FIGURE 2.3: Forward 8-point NTT with Cooley-Tukey (CT) butterfly

FIGURE 2.4: Inverse 8-point NTT with Gentleman-Sande (GS) butterfly

Combining the CT-based forward NTT and the GS-based inverse NTT, we manage to avoid reordering the output coefficients, as the GS INTT restores the bit-reversed ordered coefficients that the CT NTT produced [39]. We take the Cooley-Tukey Radix-2 NTT transform and the Gentleman-Sande Radix-2

inverse transform from [39] and present it in algorithms 4 and 5. We modify the presentation of the algorithms slightly, so as to follow the conventions used in OpenFHE library. Both of CT and GS-based NTT/INTTs can be found in their reverse forms (from bit-reversed ordered input to normal ordered output and normal ordered input to bit-reversed ordered output respectively). However, we omit presenting them here, as both of these versions are out of the scope of this work.

```

Require: a = (a_0, a_1, ..., a_{n-1}) \in \mathbb{Z}_q^n in normal-ordering. n is a power of two.

q is a prime such that q \equiv 1 \pmod{2n}. \psi_{rev} \in \mathbb{Z}_q^n are the powers of \psi in

bit-reversed order.

Ensure: a \leftarrow NTT^{\psi}(a) in bit-reversed order.

function COOLEYTUKEYRADIX2NTT(a, \psi_{rev}, n, q)

t \leftarrow n \gg 1

\log t1 \leftarrow \log 2(t)

for m = 1; m<n; m=2*m do

for i = 0; i<m; i++ do</pre>

j1 \leftarrow i \ll \text{logt1}

j2 \leftarrow j1 + t

indexOmega \leftarrow m + i

omega \leftarrow \psi_{rev}[indexOmega]

for indexLo = j1; indexLo<j2; ++indexLo do</pre>

indexHi \leftarrow indexLo + t

X_0 \leftarrow a[indexLo]

X_1 \leftarrow a |indexHi|

▷ Cooley-Tukey Butterfly

a[indexLo] \leftarrow X_0 + omega \cdot X_1 \pmod{q}

a[indexHi] \leftarrow X_0 - omega \cdot X_1 \pmod{q}

t \leftarrow t \gg 1

logt1 \leftarrow logt1 - 1

return

```

Further optimizing the butterflies has also been studied. Harvey in his paper [32] utilizes Shoup's butterfly method used in NTL library [58] to optimize the CT and GS butterflies. This technique uses precomputed values based on the powers of  $\psi$ , so as to accelerate the modular multiplication used in each butterfly and reduce the modular correction steps. Algorithm 6 below presents the optimized CT butterfly. Note that in Harvey's paper algorithm 6 is presented as the inverse butterfly, while in our case we use this version for the forward transform. To efficiently use this approach, the powers of  $\psi$  and the preconditioned powers of  $\psi$  should have been precomputed and provided as input to the algorithm.

Algorithm 5 In-Place Gentleman-Sande Inverse NTT

```

Require: a = (a_0, a_1, ..., a_{n-1}) \in \mathbb{Z}_q^n in bit-reversed ordering. n is a power of

two. q is a prime such that q \equiv 1 \pmod{2n}. \psi_{rev}^{-1} \in \mathbb{Z}_q^n are the powers of

\psi^{-1} in bit-reversed order.

Ensure: a \leftarrow INTT^{\psi}(a) in normal ordering.

function GENTLEMANSANDERADIX2INTT(a, \psi_{rev}^{-1}, n, q)

t \leftarrow 1

logt1 \leftarrow 1

for m = n; m > 1; m = m/2 do

for i = 0; i<m; i++ do</pre>

j1 \leftarrow i \ll \text{logt1}

j2 \leftarrow j1 + t

indexOmega \leftarrow m + i

omega \leftarrow \psi_{rev}^{-1}[indexOmega]

for indexLo = j1; indexLo<j2; ++indexLo do</pre>

indexHi \leftarrow indexLo + t

X_0 \leftarrow a | indexLo |

X_1 \leftarrow a[indexHi]

▷ Gentleman-Sande Butterfly

a[indexLo] \leftarrow X_0 + X_1 \pmod{q}

a[indexHi] \leftarrow (X_0 - X_1) \cdot omega \pmod{q}

t \leftarrow t \ll 1

logt1 \leftarrow logt1 + 1

for i = 0; i<n; i++ do</pre>

a[i] \leftarrow a_i \cdot n^{-1} \pmod{q}

return

```

#### Algorithm 6 Harvey/Shoup Cooley-Tukey Butterfly

**Require:** X, Y (0 < X, Y < 4 \* q) as input values and q as modulus. A root of unity W such that 0 < W < q and  $W' = \lfloor W\beta/q \rfloor$ ,  $(0 < W' < \beta)$ , where  $\beta$  is the processor word bit-size (e.g.  $\beta = 64$  for 64-bit word-size). **Ensure:**  $X' = X + WY \pmod{q}$ ,  $Y' = X - WY \pmod{q}$ ,  $(0 \le X', Y' \le 4q)$ . **function** HARVEYCTBUTTERFLY(X, Y, W, W', q) **if**  $X \ge 2q$  **then**   $X \leftarrow X - 2q$   $Q \leftarrow \lfloor W'Y/\beta \rfloor$   $T \leftarrow WY - Qq \pmod{\beta}$   $X' \leftarrow X + T$   $Y' \leftarrow X - T + 2q$ **return** X', Y'

# 2.6 OpenFHE Open-source Library

Moving from the theoretical investigation of FHE to the practical one, there is a great variety of software libraries implementing FHE schemes. These libraries provide high-level abstractions and APIs for working with FHE schemes, making it easier for developers to integrate FHE into their applications. Among all available libraries, we choose to work with OpenFHE [2], a C++ open-source library implementing all major FHE schemes (BGV, BFV, CKKS, CGGI and more). OpenFHE follows the design of the PALISADE library [50], merged with selected capabilities of HElib [31], HEAAN [11] and FHEW [18]. The latest stable version release is 1.0.4.

OpenFHE also complies with the Homomorphic Encryption post-quantum security standards available in [33] and currently supports only RNS variants of each scheme. OpenFHE is also the first FHE library that supports OpenMP multithreading. The main advantage of these libraries is the fact that by providing a non-scheme-specific API, the user does not need to understand the implementation of the internal low level functions, neither worry for their performance.

When using OpenFHE, the user should choose the plaintext modulo P for the input data of the FHE application. The encrypted data operate on a different modulus Q which is larger than the modulus P. The plaintext modulus P and the ciphertext modulus Q serve different purposes in the homomorphic encryption scheme. In more details:

- Plaintext Modulus (P): The plaintext modulus P is a parameter that determines the range of values that can be encrypted and operated on in the plaintext space. It defines the maximum value that can be represented in the plaintext domain. Any plaintext value to be encrypted must be smaller than the plaintext modulus P. The choice of P depends on the application requirements and the desired precision or granularity of computations.

- Ciphertext Modulus (Q): The ciphertext modulus Q is a parameter that defines the size of the ciphertext space and affects the security level and noise growth during homomorphic operations. It determines the maximum value of the encrypted ciphertexts. The choice of Q is typically larger than the plaintext modulus P to accommodate the intermediate results and noise introduced during homomorphic operations.

When performing homomorphic computations, the ciphertexts are manipulated using homomorphic operations (e.g., addition, multiplication) without decrypting them. The operations are performed on the encrypted data, preserving the confidentiality of the underlying plaintext. During the homomorphic operations, the ciphertext modulus Q is critical as it affects the noise growth. As the homomorphic operations are executed, the noise in the ciphertext accumulates, potentially leading to decryption errors or reduced security. Hence, choosing an appropriate ciphertext modulus Q is important to balance security and efficiency. In summary, the plaintext modulus P determines the maximum value that can be encrypted in the plaintext space, while the ciphertext modulus Q affects the security level and noise growth during homomorphic operations in the encrypted ciphertext space.

A high-level view of the steps one needs to follow so as to use OpenFHE's API in the target application is:

- 1. Select FHE parameters (plaintext modulo, etc.)

- 2. Generate public-private key pair

- 3. Encode plaintext data

- 4. Encrypt

- 5. Perform computations

- 6. Decrypt (optional)

- 7. Decode (optional)

Another advantage of OpenFHE is the very active community of researchers working on it. A forum is available and users can submit questions and discuss on FHE related topics, facilitating further someone's introduction to the library. OpenFHE also includes all performance optimization features mentioned in previous sections, such as the modular reduction techniques, the RNS system and the NTT. Regarding the modular reduction, the library internally implements the Barrett and Montgomery reduction, which are mainly used in modular multiplication operations.

In section 2.2, the basic mathematical structure of FHE was presented, the polynomial quotient ring  $R_q$  of dimension  $n = \phi(m)$ , where m is the index of the m - th cyclotomic polynomial,  $\phi$  is Euler's totient function, and Q or q is the coefficient modulus of the ring. OpenFHE uses a specific quotient ring that is defined as  $R_q = \mathbb{Z}_q[X]/(X^n + 1)$ . This ring can be also

viewed as the set of polynomials of degree less than *n* with integer coefficients in  $\{-q/2, ..., q/2\}$ . OpenFHE defines three data representation types: Poly, NativePoly and DCRTPoly. Based on the definitions provided in the OpenFHE documentation:

- A Poly is a single-CRT representation using big integer types (e.g. 128 bit) as coefficients, and supporting a large modulus *q*.

- A NativePoly is a single-CRT representation using native integer types, which limits the size of the coefficients and the modulus *q* to 64 bits.

- A DCRTPoly is a double-CRT representation.

This means that while Poly uses a single large modulus *q*, DCRTPoly uses a set of smaller moduli. Hence, computations with DCRTPoly data type is much faster than with Poly data types, because DCRTPoly operations can fit into the native bitwidths of commodity processors.

OpenFHE internally represents polynomial ring elements as being either in COEFFICIENT or EVALUATION format. It is generally computationally less expensive to carry on all operations in the evaluation form. Multiplication is currently implemented only in the EVALUATION format. The coefficient representation of *a* is a vector containing the coefficients in normal order:

$$a = [a_0, a_1, ..., a_{\phi(m)-1}] \in \mathbb{Z}_q$$

By selecting *m* and *q* as two integers in a way that the ring  $R_q = \mathbb{Z}_q[X]/(X^n + 1)$  contains a primitive m - th root of unity (denoted by  $\omega$ ), we construct vector *b* for the evaluation representation as:

$$b = [b_0, b_1, \ldots] \quad \in \mathbb{Z}_q$$

where

$b_i = a(\omega^i) \pmod{q}$  for  $i \in \mathbb{Z}_q^*$

As a note for all *i* we have the equality  $(a \mod (X-\omega^i)) = a(\omega^i) = b_i$ , meaning that the evaluation representation of *a* is just a Chinese Remainder Theorem-based polynomial representation [25].

In RLWE-based FHE schemes (BGV, BFV and CKKS), the coefficient modulus q is a very large integer and can be a few hundred bits in size. That means we would need to use multi-precision arithmetic to perform polynomial arithmetic in  $R_q$ . Multi-precision arithmetic is known to be inefficient due to its

serial nature. DCRT helps us convert these multi-precision arithmetic operations into native arithmetic that uses processor-register-size operations. DCRTPoly can be in both coefficient and evaluation format. Having a polynomial in  $R_q$ , the procedure to create a DCRTPoly starts by decomposing the modulo q as a product of (t + 1) small primes  $(p_0, p_1, ..., p_t)$ . The size of each small prime is typically 32, 40, 50 and up to 60 bits. This allows us to factor our polynomial into smaller polynomials using the Chinese Remainder Theorem. The result is a matrix of dimensions  $(t + 1) \times n$  where n is the ring size or the polynomial degree. The coefficients of this matrix are native integers and in coefficient format.

Having two polynomials, coefficient-wise modular addition or subtraction can be performed directly in their coefficient representation as:

$$C_{ij} = A_{ij} \oplus B_{ij} \pmod{p_i}$$

where  $\oplus$  can be [+, -] and i = 0, 1, ..., t.

However, polynomial multiplication between two polynomials in  $R_q$  is currently supported only in evaluation format. Switching formats requires using the Number Theoretic Transform (NTT). NTT and Inverse NTT operations take  $O(n \log n)$  time using current best known algorithms, where n is the ring dimension. Applying the NTT transform into our  $(t + 1) \times n$  matrix, yields another matrix of dimension  $(t + 1) \times n$ . The key-point here is that the schoolbook polynomial multiplication can now be substituted by a coefficient-wise modular multiplication:

$$C_{ij} = A_{ij} * B_{ij} \pmod{p_i}$$

where i = 0, 1, ..., t.

We remind that addition and subtraction can also be computed in the evaluation format in the same way as in the coefficient format. The conversion back from evaluation format to coefficient format may not always be needed, and we can do further operations in the evaluation representation.

In OpenFHE, in-place and out-of-place Number Theoretic Transform variants are available. The library implements the negacyclic NTT transform in order to perform transformations within the  $R_q = \mathbb{Z}_q[X]/(X^n + 1)$  ring. For the forward NTT transform, the Cooley-Tukey radix-2 butterfly with normalordered input and bit-reversed output is used. To avoid, reordering the output, the Gentleman-Sande radix-2 butterfly with bit-reversed input and normal-ordered output is used for the inverse NTT. The library also precomputes the necessary roots-of-unity for each modulo  $q_i$  and stores it, so as to avoid re-computing the roots if the same modulo is used in the same application run. This approach is also followed for the preconditioned roots of unity factors that are used for Harvey's efficient modular multiplication algorithm.

OpenFHE internally sets the necessary parameters. For the negacyclic Number Theoretic Transform (NTT), the library sets a modulo Q that is decomposed into a number of smaller moduli  $q_i$  and a ring of a constant size. Selecting Q and  $q_i$  as prime numbers, the library ensures that the modular arithmetic system satisfies certain desirable properties. Prime numbers have the property that every non-zero element is invertible modulo Q, meaning that there exists a unique multiplicative inverse for each non-zero element in the ring. This property is crucial for performing division and inversion operations in the polynomial quotient ring. The size of the ring, which is usually a power of two and determined by the parameter Q, should be large enough to accommodate the input data and to preserve the desired precision in the transformed domain. This choice ensures that the polynomial remains within the ring during the NTT computation.

Overall, OpenFHE is in the center of attention in the Fully Homomorphic Encryption community, as it implements all available FHE schemes and integrates most of available optimizations both in the algorithmic level (e.g. NTT optimizations) and in the software implementation level (e.g. deploying acceleration techniques such as multithreading). OpenFHE also includes benchmarks for all important low-level and high-level functions, under the benchmark folder of its source files. Researchers aiming to compare OpenFHE performance with other existing libraries, using some reference benchmarks, can you use the work of Gouert et al. [28] by modifying slightly the PAL-ISADE's benchmarks provided. Instructions of how to migrate a project from PALISADE to OpenFHE are provided in OpenFHE's documentation.

# Chapter 3

# **Related Work**

### 3.1 Accelerating FHE Schemes

While the usefulness of FHE schemes is undeniable and consolidated efforts like the OpenFHE library are a step towards their wider adoption, there is a significant barrier that hinders their practical use: their real-world performance. When measuring the performance of FHE compute, a comparison is typically made against equivalent computations on the plain text version of the data. The encryption methods to enable FHE can increase the size of the data by 100-1000x, and then compute on that data is 10000x to 1 million times slower than conventional compute. To put this into perspective, one second of compute on the raw data can take from 3 hours to 12 days.

As such, FHE scheme acceleration is a significantly active field of research within the FHE community. Two main components are targeted: the computational intensive polynomial operations and the highly time consuming ciphertext maintenance operations. There is a plethora of accelerators designed for different hardware platforms, such as CPUs, GPUs, FPGAs and ASICs [54], [59], [61], [52], [1], [6], [35], [37], [17], [57]. A systematic comparison of existing FHE accelerators is provided in [66], while an overview of researched acceleration methods can be found in [27].

No matter the targeted platforms, accelerators are usually designed either to accelerate high-level functions of a specific FHE scheme, such as keyswitching, modulus switching and bootstrapping [59], [61], [1], or optimize low-level functions, common among different FHE schemes, such as the Number Theoretic Transform (NTT) and the polynomial multiplication [52], [6], [35], [5], [42].

### **3.2 The FPGA Perspective**

A Field Programmable Gate Array (FPGA) is an integrated circuit (IC) designed to be configured after manufacturing. Similarly to an ASIC device, an FPGA implements custom circuits that perform a specified logic functionality. This is achieved by programming its logic elements and signal routing instead of etching a circuit on a silicon substrate. As such, FPGAs cannot provide neither the performance nor the energy efficiency that can be achieved with ASIC devices. But at the same time, due to its reconfiguration capabilities, an FPGA can be vastly more flexible, adaptable and easier to deploy and use post fabrication. Modern solutions that employ High Level Synthesis design tools and standardized deployment environments (in SoCs or PCIe-based accelerator boards) further lower the design and deployment difficulties for FPGA-based solutions.

Compared to software programmable devices such as CPUs or GPUs, a compute function implemented in an FPGA is realised at a far lower level (logic gate level) with significantly less overheads attributed to software elements. This apparently means that performance and energy efficiency can be significantly higher but programmability, ease of development and flexibility are to a certain degree sacrificed. Therefore, an FPGA can be seen as a middle ground between general-purpose processors and application-specific circuits in terms of performance, energy efficiency and programmability. This makes them ideal for accelerating compute functions that cannot be effectively handled by CPUs or GPUs and at the same time they are not standardised enough or fixed to the extend that an ASIC design cost may be justified.

This is the reason that the FHE research community has heavily relied on using FPGA devices to explore acceleration opportunities in order to make the FHE schemes significantly faster. For example, the Intel proposed HEXL library [6], tries to take advantage of the AVX-512 Instruction Set to accelerate the NTT and the polynomial multiplication on general purpose processors (CPU). However, while it achieves high single core acceleration, when multithreading is enabled, the overall performance decreases mainly due to the caused heat dissipation that forces the CPU to reduce its working frequency.

To overcome these limitations, Intel has also published a High Level Synthesis (HLS) FPGA-based accelerator (Intel HEXL-FPGA [35]) that supports the same functionality as Intel HEXL and is open-source. Their work supports operations on polynomials of degree in range [2<sup>10</sup>, 2<sup>15</sup>]. The FPGA approach

improves another limitation of HEXL, the slow memory access, but the HLS design does not manage to optimally utilize the FPGA resources. Microsoft proposed HEAX [52] in 2020, a multi core FPGA-based architecture targeting the NTT, the modular multiplication and the key-switching function through different hardware modules. HEAX needs to be reconfigured to support different cryptographic parameters, such as different polynomial degree, however it outperforms Intel HEXL-FPGA. HEAT [59], another FPGA-based accelerator, was designed to accelerate primitive operations of the BFV scheme (e.g. addition, subtraction, multiplication, modulus switching, NTT). HEAT operates on polynomials of degree up to 4096 (2<sup>12</sup>), limiting its practical use.

The main disadvantage of many FPGA accelerators is the fact that the supported parameters are fixed and limited, leading to designs of limited generality. Dedicated architecture (ASIC) accelerators supporting different FHE schemes have also been proposed (F1 [54] supporting polynomials of maximum degree 2<sup>14</sup>, ARK [37] supporting polynomials of maximum degree  $2^{16}$ ). A common issue regarding ASIC approaches is the designs' throughput. FHE applications launched on ASICs will not always succeed in fully utilizing its available resources, leading to highly underutilized designs. While it is obvious that accelerating low-level functions propagates to high-level functions as well, accelerating directly the ciphertext maintenance operations is crucial so as to make FHE practical. FAB [1] is a recently proposed FPGA accelerator supporting bootstrapping and polynomials of degree up to  $2^{16}$ . FAB outperforms F1 ASIC-based design for a logistic regression application but does not manage to reach the performance of ARK. ARK also targets FHE high-level functions and deploys on-the-fly data generation to reduce the size of the plaintexts used in bootstrapping.

Accelerating only the NTT is also common in the literature. Various accelerators have been proposed for different platforms, targeting different NTT algorithm versions [40], [19], [5], [42], [44]. These works are the result of many NTT proposed optimizations [39], [32], [53], [51] and they usually support a limited range of NTT parameters (e.g. polynomial degree, ciphertext modulo bits, etc.). For example, the work of Mert et al. [40] includes designing a NTT accelerator on a Xilinx Virtex-7 FPGA, using Verilog, High-Level Synthesis (HLS) and a RISC-V ISA and compare the resuls of each design approach. The maximum supported polynomial degree is 2<sup>12</sup>. Note that most works implement a different NTT algorithm for the forward transform, indicating the variety of NTT-related works in the literature. HLS designs for the

NTT have also been proposed, each focusing on optimizations based on the supported NTT parameters and the available FPGA platform [40], [47], [36] [46].

Recent works on Number Theoretic Transform (NTT) accelerators have also focused on area efficient [19] and configurable designs [20]. As accelerating the NTT is only one part of FHE acceleration attempts, area efficient and configurable designs are essential in the case where someone attempts to accelerate more functions beyond the NTT. For example, supporting fast and efficient NTTs of size 2<sup>17</sup> can utilize a significant amount of resources for some designs in an FPGA. If more kernels are to be included, such as an inverse NTT kernel or a key-switching kernel, area efficiency of the kernels design is paramount. Overall, optimizing hardware designs for the NTT depends on the use-case, the platform used and the experience of the designer with the available technology and implementation methods.

### 3.3 Thesis Approach

According to the aforementioned, we believe that offloading computationally intensive parts of the FHE computations on hardware accelerators implemented in FPGA is a viable path towards increasing the performance of FHE schemes. However, in order to ensure adoption and increase the impact of these efforts, we need to ensure that compatibility with the de-facto standard FHE library (OpenFHE) is maintained, while ease of use and deployment remains high without introducing any significant restrictions (e.g. limited functionality, support only for specific data sizes, etc).

Therefore, in this work we aim to provide a hardware-based accelerator integrated into OpenFHE. We employ a Xilinx Alveo U50 available in our data center and mainly focus on showing how a Xilinx Vitis IDE-developed application can be integrated with OpenFHE. We are going to provide a functional NTT implementation supporting various NTT sizes that can be tested alongside OpenFHE with the goal that applications employing the vanilla OpenFHE library can seamlessly employ its hardware-accelerated version as well.

# Chapter 4

# **Defining the Architecture**

# 4.1 **OpenFHE Library Profiling**

Software profiling is the process of analyzing the runtime behavior of a software application to gather information about its execution characteristics, such as function calls, memory usage and execution time. Profiling helps developers identify performance bottlenecks, memory leaks, and areas of the code that can be optimized for better efficiency. Profiling tools, like *gperftools* (Google Performance Tools) [34], provide insights into how the program is actually running, helping developers make informed decisions about code optimization and resource allocation. We use *gperftools* as our main profiling tool, in order to determine the computational bottlenecks of OpenFHE library. *gperftools* is an open-source collection of profiling and performance optimization tools developed by Google. It includes tools for CPU and heap profiling, memory debugging, and code coverage analysis.

To configure OpenFHE for *gperftools*, one needs to add the below code lines in the CMakeLists.txt included in the OpenFHE source directory.

```

set( CMAKE_CXX_FLAGS "${CMAKE_CXX_FLAGS} -lprofiler")

set( CMAKE_EXE_LINKER_FLAGS "${CMAKE_EXE_LINKER_FLAGS} -lprofiler")

set( CMAKE_SHARED_LINKER_FLAGS "${CMAKE_SHARED_LINKER_FLAGS} -lprofiler")

```

Following this step, the user needs to open a new terminal session in the gperftools directory ( $\sim$ /gperftools) and execute the below code lines:

Using the code above, the results will be displayed in a new web browser session. Alternatives for different result format can be found at [30]. To ensure the best results, OpenFHE's multithreading must be disabled by setting the OMP\_NUM\_THREADS terminal environment variable to 1.

We use the above settings to get profiling results for the different schemes of OpenFHE using the following files: *example.cpp*<sup>1</sup> (C++ code developed during the thesis, which includes the same dataset computations for BGV, BFV, CKKS schemes), *logistic\_regression\_a16\_int.cpp/ logistic\_regression\_a16\_fp.cpp* (modified C++ code files compatible with OpenFHE out of T2 benchmarks [28]), *boolean.cpp/ boolean-ap.cpp* (C++ code example included in OpenFHE), *simple- ckks- bootstrapping.cpp/ iterative- ckks- bootstrapping.cpp/ advanced-ckks-bootstrapping.cpp* (C++ code example included in OpenFHE).

We keep track of the most called functions and we identify the key operations of each scheme. Our results can be found in the figures 4.1 and 4.2. Our profiling results are in line with those presented in Section 3.2 confirming the focus on accelerating functions such as the NTT. We focus on the BFV, BGV and CKKS scheme results, to avoid memory bound problems of TFHE/FHEW schemes, due to large key sizes and large intermediate data of these schemes.

Based on figures 4.1 and 4.2, we notice that the majority of our code examples consume a significant amount of time at the *SwitchFormat* function, because of multiple function calls. Bootstrapping (*EvalBootstrap* function) and multiplication (*EvalMult* function) are other bottleneck operations. However, *EvalBootstrap* is solely used for the CKKS scheme, while the *EvalMult* high-level function consists of some *SwitchFormat* function calls. Having no prior experience with Fully Homomorphic Encryption, we choose to work with accelerating the *SwitchFormat* function, which breaks down to the forward and the inverse Number Theoretic Transform (NTT). The NTT has been identified as an FHE bottleneck operation multiple times in literature. For the rest of this thesis, we focus on the forward NTT, however our work can be modified to apply for the inverse NTT as well.

<sup>&</sup>lt;sup>1</sup>example.cpp is provided in the private GitHub repository for this thesis (https://github.com/parasecurity/FHE\_FPGA/tree/main/OpenFHE\_FPGA)

|                                                       | <u>File (.cpp)</u> |                  |                   |                                       |                                       |  |  |  |

|-------------------------------------------------------|--------------------|------------------|-------------------|---------------------------------------|---------------------------------------|--|--|--|

| OpenFHE Function name                                 | example<br>(BFV)   | example<br>(BGV) | example<br>(CKKS) | logistic_regression<br>_a16_int (BFV) | logistic_regression<br>_a16_fp (CKKS) |  |  |  |

| lbcrypto CryptoContextImp Encrypt                     | 24.7%              | 29.3%            | 13.7%             | 20.3%                                 | 22.5%                                 |  |  |  |

| lbcrypto CryptoContextImp Decrypt                     | 12.3%%             | 20.9%            | 57.5%             | -                                     | -                                     |  |  |  |

| lbcrypto CryptoContextImp EvalMult                    | 60%                | 45.7%            | 24.6%             | 43.1%                                 | 25%                                   |  |  |  |

| lbcrypto CryptoContextImp EvalRotate                  | -                  | -                | -                 | -                                     | -                                     |  |  |  |

| lbcrypto CryptoContextImp EvalBootstrap               | -                  | -                | -                 | -                                     | -                                     |  |  |  |

| lbcrypto LeveledSHEBFVRNS RelinearizeCore             | 12.7%              | -                | -                 | 12.5%                                 | -                                     |  |  |  |

| lbcrypto BinFHEScheme BootstrapGateCore               | -                  | -                | -                 | -                                     | -                                     |  |  |  |

| lbcrypto LeveledSHECKKSRNS ModReduceInternalInPlace   | -                  | -                | 9.3%              | -                                     | -                                     |  |  |  |

| lbcrypto SchemeBase KeySwitchCore                     | 6.4%               | 26.3%            | 13.7%             | 6.2%                                  | 20.8%                                 |  |  |  |

| lbcrypto DCRTPolyImpl ApproxModDown                   | -                  | 14.7%            | 7%                | -                                     | 6.7%                                  |  |  |  |

| Ibcrypto DCRTPolyImpl ModReduce                       | -                  | 19%              |                   | -                                     | -                                     |  |  |  |

| lbcrypto DCRTPolyImpl SwitchFormat                    | 38.1%              | 25.9%            | 12.7%             | 23.4%                                 | 14.2%                                 |  |  |  |

| Ibcrypto PolyImpl SwitchFormat                        | 49.9%              | 39%              | 19%               | 43.8%                                 | 33.3%                                 |  |  |  |

| lbcrypto DiscreteUniformGeneratorImpl GenerateInteger | -                  | -                | -                 | 10.9%                                 | 19.2%                                 |  |  |  |

| lbcrypto PseudoRandomNumberGenerator GetPRNG          | 1.9%               | 2.5%             |                   | 4.7%                                  | 7.5%                                  |  |  |  |

| intnat NativeVectorT SwitchModulus                    | -                  | 4.3%             | 2.3%              | -                                     | -                                     |  |  |  |

| intnat NativeVectorT ModMulEq                         | 6.8%               | 10.4%            | 3.9%              | 4.7%                                  | 10.8%                                 |  |  |  |

| intnat NumberTheoreticTransformNat                    | 27.2%              | 22.7%            | 10.8%             | 35.9%                                 | 29.2%                                 |  |  |  |

| ForwardTransformToBitReverseInPlace                   | 27.270             | 22.170           | 10.070            | 33.970                                | 23.270                                |  |  |  |

| intnat NumberTheoreticTransformNat                    | 22.7%              | 17.20/           | 9.3%              | 7.8%                                  | 4.2%                                  |  |  |  |

| InverseTransformFromBitReverseInPlace                 | 23.7%              | 17.2%            | 8.2%              | 1.8%                                  | 4.2%                                  |  |  |  |

<20% 20-30% 30-40% 40-50% >50%

| FIGURE 4.1: | Function execution time % out of C++ code total |

|-------------|-------------------------------------------------|

|             | execution time $(1/2)$                          |