## TECHNICAL UNIVERSITY OF CRETE

DIPLOMA THESIS

# A Preliminary Accuracy Analysis of Simulated RISC-V Systems

Author: Evangelos KIOULOS Thesis Committee: Prof. Apostolos DOLLAS Assoc. Prof. Sotirios IOANNIDIS Dr. Angelos IOANNOU (FORTH and LBNL)

A thesis submitted in fulfillment of the requirements for the diploma of Electrical and Computer Engineer

in the

School of Electrical and Computer Engineering Microprocessor and Hardware Laboratory

December 18, 2023

#### TECHNICAL UNIVERSITY OF CRETE

## Abstract

#### School of Electrical and Computer Engineering

**Electrical and Computer Engineer**

#### A Preliminary Accuracy Analysis of Simulated RISC-V Systems

by Evangelos KIOULOS

The RISC-V Instruction Set Architecture (ISA) maintains a surging interest both in industry and academia due to its simplicity, extensibility, and open license. The integration of RISC-V ISA in the widely used gem5 simulator bridges the gap between RTL and ISA (Spike, QEMU) simulation, as it offers a micro-architectural simulator to the RISC-V ecosystem. This, however, raises uncertainty regarding the accuracy degree of the RISC-V related model implementations in gem5. Especially if we consider that they are still premature due to their recent adoption. The modeling accuracy is crucial as it is responsible for guiding properly research studies and pinpointing areas for optimization on various architectural design spaces. In this thesis, we aim to match the performance and energy costs of an ASIC RISC-V implementation, namely CVA6 (formerly known as Ariane), with a simulated RISC-V system in gem5. We present our experimental setup where we use the gem5 simulator to obtain the performance statistics and McPAT to estimate power and energy metrics. Afterwards, we proceed with an analysis plan to identify potential inaccuracies and flaws of the gem5 simulator. We then evaluate the performance of our simulated system using benchmarks from the RISC-V ecosystem and compare the results to published hardware implementations.

#### TECHNICAL UNIVERSITY OF CRETE

### Abstract

#### School of Electrical and Computer Engineering

**Electrical and Computer Engineer**

#### A Preliminary Accuracy Analysis of Simulated RISC-V Systems

#### by Evangelos KIOULOS

Η αργιτεκτονική RISC – V προκαλεί αυξανόμενο ενδιαφέρον, τόσο στη βιομηγανία όσο και στην ακαδημαϊκή κοινότητα, λόγω της επεκτασιμότητας της, του απλού συνόλου εντολών που προσφέρει και του ανοιχτού της κώδικα. Η ενσωμάτωση της αρχιτεχτονιχής RISC – V στον ευρέως χρησιμοποιημένο προσομοιωτή gem5 γεφυρώνει το χάσμα μεταξύ της RTL προσομοίωσης και της προσομοίωσης επιπέδου συνόλου εντολών (ISA, όπως τα Spike, QEMU), καθώς εισάγει στο οικοσύστημα της αρχιτεχτονιχής RISC - V την προσομοίωση επιπέδου μίκρο-αρχιτεχτονιχής. Ωστόσο, η εν λόγω εφαρμογή εγείρει ζητήματα ως προς τον βαθμό αχρίβειας της υλοποίησης της αρχιτεκτονικής RISC – V στο gem5, ειδικά αν λάβουμε υπόψη ότι βρίσκεται αχόμα σε πρώιμο στάδιο. Η αχρίβεια στην μοντελοποίηση έχει ιδιαίτερη αξία τόσο στην καθοδήγηση της σχετικής έρευνας, όσο και στην ανάδειξη πεδίων βελτιστοποίησης των διαφόρων αρχιτεκτονικών. Σε αυτή τη διπλωματική εργασία προσπαθούμε να παραγάγουμε την απόδοση και τα κόστη σε ισχύ και ενέργεια μιας ASIC υλοποίησης ενός επεξεργαστή αρχιτεκτονικής RISC – V, του CVA6 (παλαιότερα γνωστός και ως Ariane), σε ένα προσομοιωμένο σύστημα στον προσομοιωτή gem5. Παρουσιάζουμε την πειραματική διαδικασία όπου χρησιμοποιούμε τον προσομοιωτή gem5 για τον υπολογισμό της απόδοσης του συστήματος και τον προσομοιωτή McPAT για τον υπολογισμό της ισχύος και της ενέργειας. Στη συνέχεια, αξιολογούμε τα αποτελέσματά μας χρησιμοποιώντας βενςημαρκς από το οικοσύστημα της αρχιτεκτονικής RISC – V και συγκρίνοντάς τα με τα δημοσιευμένα.

# Acknowledgements

First of all, I would like to thank my supervisors Prof. Apostolos Dollas and Dr. Angelos Ioannou for their support and guidance during this thesis. Assoc. Prof. Sotirios Ioannidis from the thesis committee for his feedback on the text.

I would also like to express my gratitude to Sotiris Totomis for his guidance and insights throughout this thesis. His valuable feedback, help with the tools and comments on the thesis text were vital for the completion of this project.

Last but not least, I would like to thank Prof. Nikolaos Tampouratzis and Dr. Andreas Brokalakis for their helpful comments and advice regarding the use and errors of McPAT.

# Contents

| Al | bstrac  | ct      |                                            | iii  |

|----|---------|---------|--------------------------------------------|------|

| A  | bstrac  | ct      |                                            | v    |

| A  | cknov   | wledge  | ments                                      | vii  |

| Co | onten   | ts      |                                            | ix   |

| Li | st of ] | Figures | 3                                          | xiii |

| Li | st of ' | Tables  |                                            | xv   |

| Li | st of . | Abbrev  | viations                                   | xvii |

| 1  | Intr    | oductio | n                                          | 1    |

|    | 1.1     | Motiv   | ration                                     | 1    |

|    | 1.2     | Objec   | tives                                      | 2    |

|    |         | 1.2.1   | Contributions                              | 3    |

|    | 1.3     | Thesis  | S Outline                                  | 4    |

| 2  | The     | oretica | l Background                               | 5    |

|    | 2.1     | RISC-   | V Architecture and Simulation Environments | 5    |

|    |         | 2.1.1   | RISC-V Instruction Set Architecture        | 5    |

|    |         | 2.1.2   | CVA6 (former Ariane)                       | 9    |

|    |         | 2.1.3   | Alternative RISC-V Hardware                | 13   |

|    | 2.2     | Bench   | ımarks                                     | 14   |

|    |         | 2.2.1   | RISCV-Tests suite                          | 15   |

|    |         | 2.2.2   | Dhrystone                                  | 16   |

|    | 2.3     | The g   | em5 Simulator                              | 18   |

|    |         | 2.3.1   | Key Features and Capabilities              | 18   |

|    |         | 2.3.2   | CPU and Memory models                      | 20   |

|    |         | 2.3.3   | ISA Independence                           |      |

|    |         | 2.3.4   | RISC-V ISA support                         | 23   |

|   | 2.4  | Powe    | r and Area simulation with McPAT                            | 23 |

|---|------|---------|-------------------------------------------------------------|----|

|   |      | 2.4.1   | Power, Area and Timing Models                               | 25 |

|   |      | 2.4.2   | Accuracy Errors and Calibration                             | 25 |

| 3 | Rela | ated W  | ork                                                         | 27 |

|   | 3.1  | gem5    | Simulations of ARM and x86 Processors                       | 27 |

|   | 3.2  | gem5    | applications and implementation on the RISC-V ISA $\ . \ .$ | 30 |

|   | 3.3  | Powe    | r modeling using McPAT                                      | 33 |

|   | 3.4  | Thesi   | s Approach and Motivation                                   | 34 |

| 4 | Sim  | ulation | n Environment Setup and Implementation                      | 35 |

|   | 4.1  | Conce   | ept and Tool Work-Flow                                      | 35 |

|   |      | 4.1.1   | Tool Work-Flow                                              | 36 |

|   | 4.2  | Bench   | marks                                                       | 37 |

|   |      | 4.2.1   | Setting up the tests                                        | 37 |

|   | 4.3  | Imple   | ementing the core model for simulation in gem5              | 38 |

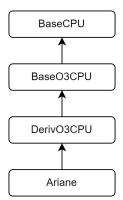

|   |      | 4.3.1   | CPU Configuration                                           | 39 |

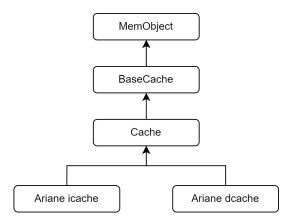

|   |      | 4.3.2   | Instruction/Data Caches                                     | 40 |

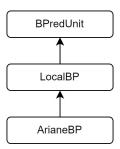

|   |      | 4.3.3   | Branch Prediction Unit                                      | 40 |

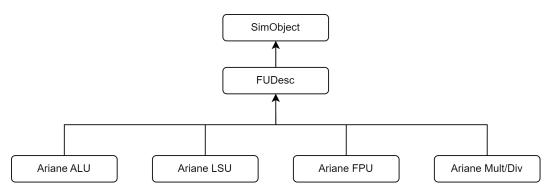

|   |      | 4.3.4   | Functional Units                                            | 41 |

|   |      | 4.3.5   | Choosing Parameter Values For The Base Model                | 43 |

|   | 4.4  | Confi   | guration files setup                                        | 46 |

|   |      | 4.4.1   | System object and configuration script setup                | 47 |

|   |      | 4.4.2   | Creating a run script                                       | 49 |

|   |      | 4.4.3   | Running the simulation                                      | 49 |

|   | 4.5  | Settin  | g up McPAT for power and energy modeling                    | 51 |

|   |      | 4.5.1   | Creating the input file for McPAT                           | 52 |

|   |      | 4.5.2   | Running McPAT                                               | 52 |

| 5 | Res  | ults an | d Performance Analysis                                      | 53 |

|   | 5.1  | Perfo   | rmance Experiments and Results                              | 53 |

|   |      | 5.1.1   | IPC Results from the Dhrystone Benchmark                    | 54 |

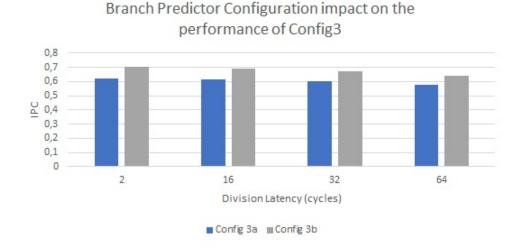

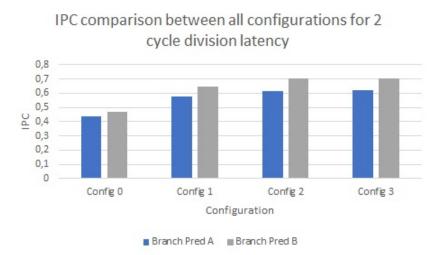

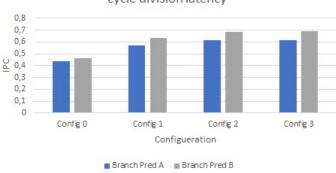

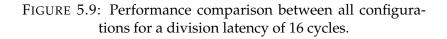

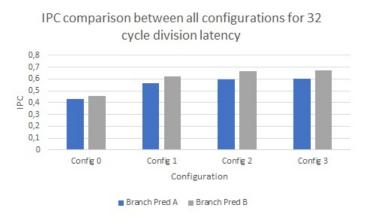

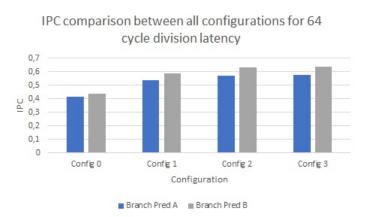

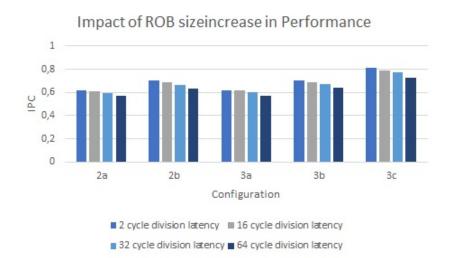

|   |      | 5.1.2   | Performance comparison between configurations               | 57 |

|   |      | 5.1.3   | Matching the reported performance                           | 62 |

|   |      | 5.1.4   | Discussion                                                  | 63 |

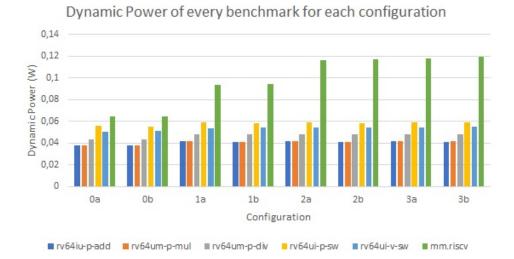

|   | 5.2  | Powe    | r and Energy Experiments and Results                        | 63 |

|   |      | 5.2.1   | Leakage Power Results                                       | 64 |

|   |      | 5.2.2   | Dynamic Power and Energy Results                            | 65 |

|   |      | 5.2.3   | Discussion                                                  | 73 |

х

| 6  | Con   | clusions and Future Work                                       | 75 |

|----|-------|----------------------------------------------------------------|----|

|    | 6.1   | Conclusions                                                    | 75 |

|    | 6.2   | Future Work                                                    | 76 |

| A  | Env   | ironment Setup and Running the Scripts                         | 77 |

|    | A.1   | Building the RISC-V GNU compiler toolchain                     | 77 |

|    | A.2   | Building the RISC-V tests                                      | 78 |

|    | A.3   | Obtaining the kernel binary and disk image from gem5-resources | 78 |

|    | A.4   | Running the Scripts                                            | 79 |

|    | A.5   | Changing Parameter Values                                      | 83 |

|    | A.6   | Running McPAT                                                  | 84 |

| B  | Con   | mon Errors during setup and development with gem5 and pos-     |    |

|    | sible | e solutions                                                    | 85 |

|    | B.1   | Errors on compilation                                          | 85 |

|    | B.2   | Errors during development with gem5's Full-System mode         | 86 |

|    | B.3   | Errors when using McPAT                                        | 87 |

| Re | ferer | ICES                                                           | 89 |

# **List of Figures**

| 2.1                                                                                                                | RISC-V Base Instruction Formats                                                                                                                                                                                                                                                                                    | 7                                      |

|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 2.2                                                                                                                | RISC-V Instruction Formats including SB and UJ                                                                                                                                                                                                                                                                     | 8                                      |

| 2.3                                                                                                                | Ariane's 6-stage Pipeline                                                                                                                                                                                                                                                                                          | 11                                     |

| 2.4                                                                                                                | Simplest system that can be simulated in SE mode                                                                                                                                                                                                                                                                   | 19                                     |

| 2.5                                                                                                                | Speed vs Accuracy trade-offs                                                                                                                                                                                                                                                                                       | 22                                     |

| 2.6                                                                                                                | Block diagram of the McPAT framework                                                                                                                                                                                                                                                                               | 24                                     |

| 4.1                                                                                                                | Tool work-flow                                                                                                                                                                                                                                                                                                     | 36                                     |

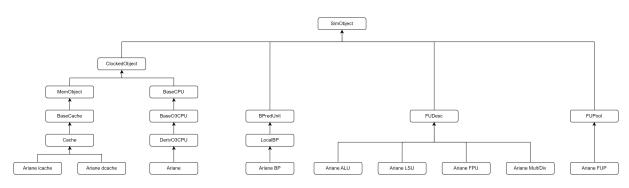

| 4.2                                                                                                                | CPU class inheritance diagram                                                                                                                                                                                                                                                                                      | 40                                     |

| 4.3                                                                                                                | Cache class inheritance diagram                                                                                                                                                                                                                                                                                    | 40                                     |

| 4.4                                                                                                                | Branch Prediction class inheritance diagram                                                                                                                                                                                                                                                                        | 41                                     |

| 4.5                                                                                                                | Functional Units class inheritance diagram                                                                                                                                                                                                                                                                         | 41                                     |

| 4.6                                                                                                                | Class inheritance diagram of objects in ariane.py                                                                                                                                                                                                                                                                  | 42                                     |

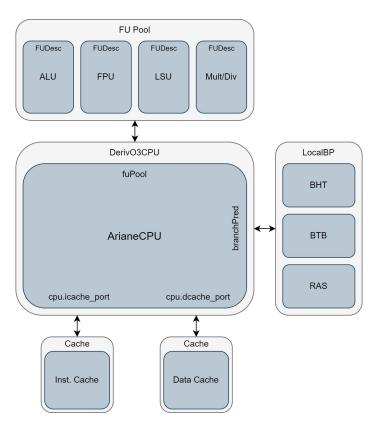

| 4.7                                                                                                                | CPU configuration for simulation in gem5                                                                                                                                                                                                                                                                           | 42                                     |

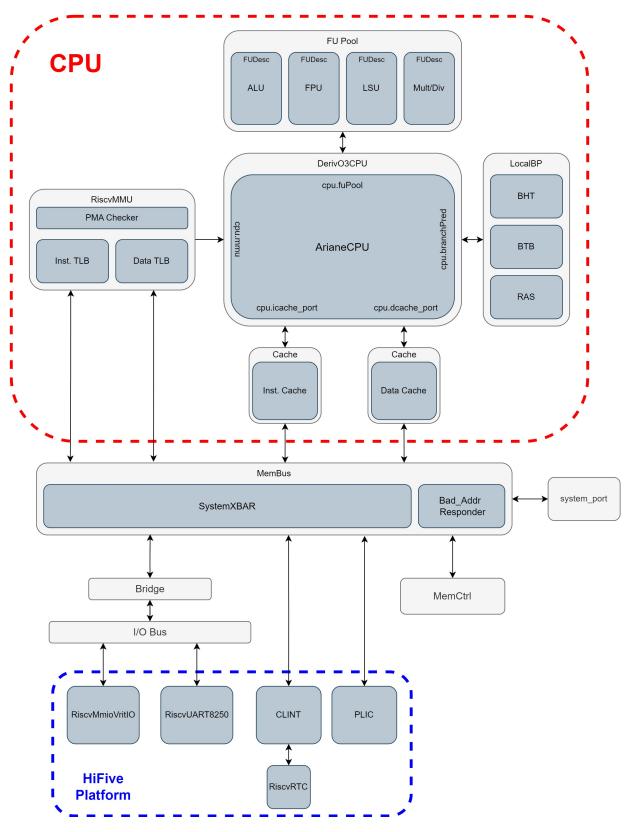

| 4.8                                                                                                                | System configuration for Full System simulation in gem5                                                                                                                                                                                                                                                            | 50                                     |

|                                                                                                                    |                                                                                                                                                                                                                                                                                                                    |                                        |

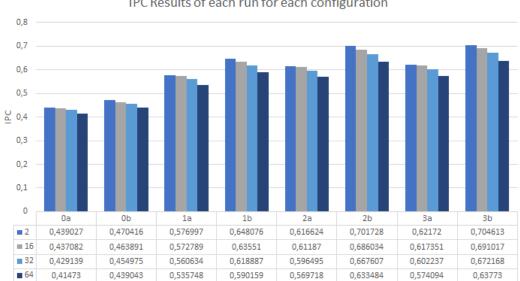

| 5.1                                                                                                                | IPC and DMIPS/MHz results graph for all the configurations                                                                                                                                                                                                                                                         | 56                                     |

| 5.1<br>5.2                                                                                                         | IPC and DMIPS/MHz results graph for all the configurations<br>Performance comparison between configurations with the orig-                                                                                                                                                                                         | 56                                     |

|                                                                                                                    |                                                                                                                                                                                                                                                                                                                    | 56<br>57                               |

|                                                                                                                    | Performance comparison between configurations with the orig-                                                                                                                                                                                                                                                       |                                        |

| 5.2                                                                                                                | Performance comparison between configurations with the orig-<br>inal Branch Prediction Unit Setup.                                                                                                                                                                                                                 |                                        |

| 5.2                                                                                                                | Performance comparison between configurations with the orig-<br>inal Branch Prediction Unit Setup                                                                                                                                                                                                                  | 57                                     |

| 5.2<br>5.3                                                                                                         | Performance comparison between configurations with the orig-<br>inal Branch Prediction Unit Setup                                                                                                                                                                                                                  | 57<br>58                               |

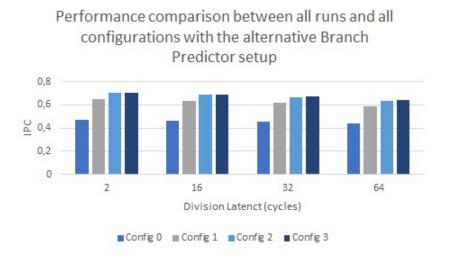

| <ul><li>5.2</li><li>5.3</li><li>5.4</li></ul>                                                                      | Performance comparison between configurations with the orig-<br>inal Branch Prediction Unit Setup Performance comparison between configurations with the al-<br>ternative Branch Prediction Unit Setup                                                                                                             | 57<br>58<br>58                         |

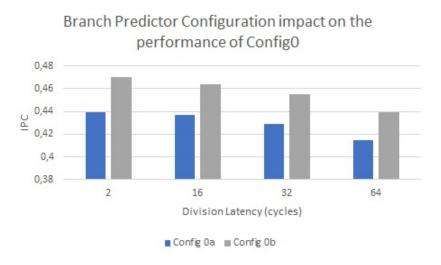

| <ol> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> </ol>                                                     | Performance comparison between configurations with the orig-<br>inal Branch Prediction Unit Setup Performance comparison between configurations with the al-<br>ternative Branch Prediction Unit Setup                                                                                                             | 57<br>58<br>58<br>59                   |

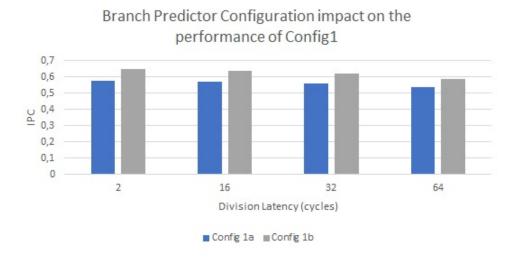

| <ol> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> <li>5.6</li> </ol>                                        | Performance comparison between configurations with the orig-<br>inal Branch Prediction Unit Setup Performance comparison between configurations with the al-<br>ternative Branch Prediction Unit Setup Performance results from all runs for Configuration 0 Performance results from all runs for Configuration 1 | 57<br>58<br>58<br>59<br>59             |

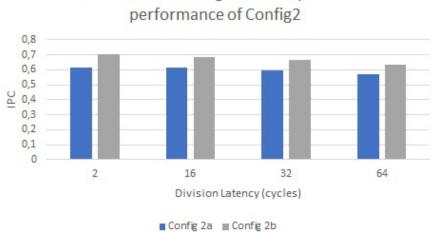

| <ol> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> <li>5.6</li> <li>5.7</li> </ol>                           | Performance comparison between configurations with the orig-<br>inal Branch Prediction Unit Setup Performance comparison between configurations with the al-<br>ternative Branch Prediction Unit Setup                                                                                                             | 57<br>58<br>58<br>59<br>59             |

| <ol> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> <li>5.6</li> <li>5.7</li> </ol>                           | Performance comparison between configurations with the orig-<br>inal Branch Prediction Unit Setup Performance comparison between configurations with the al-<br>ternative Branch Prediction Unit Setup Performance results from all runs for Configuration 0 Performance results from all runs for Configuration 1 | 57<br>58<br>58<br>59<br>59<br>60       |

| <ol> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> <li>5.6</li> <li>5.7</li> <li>5.8</li> </ol>              | Performance comparison between configurations with the orig-<br>inal Branch Prediction Unit Setup Performance comparison between configurations with the al-<br>ternative Branch Prediction Unit Setup                                                                                                             | 57<br>58<br>58<br>59<br>59<br>60       |

| <ol> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> <li>5.6</li> <li>5.7</li> <li>5.8</li> <li>5.9</li> </ol> | Performance comparison between configurations with the orig-<br>inal Branch Prediction Unit Setup Performance comparison between configurations with the al-<br>ternative Branch Prediction Unit Setup                                                                                                             | 57<br>58<br>58<br>59<br>59<br>60<br>60 |

| 5.11  | Performance comparison between all configurations for a di-     |    |

|-------|-----------------------------------------------------------------|----|

|       | vision latency of 64 cycles                                     | 61 |

| 5.12  | Performance comparison between configuration 3c and con-        |    |

|       | figurations 2 and 3                                             | 62 |

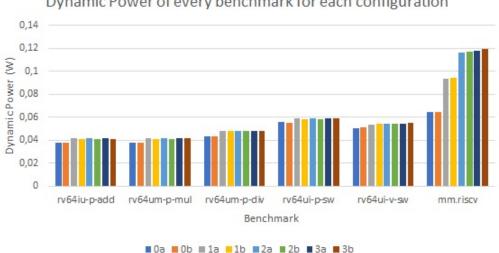

| 5.13  | Dynamic Power results of each configuration on every bench-     |    |

|       | mark                                                            | 66 |

| 5.14  | Dynamic Power results of each configuration on every bench-     |    |

|       | mark, comparing the benchmarks.                                 | 67 |

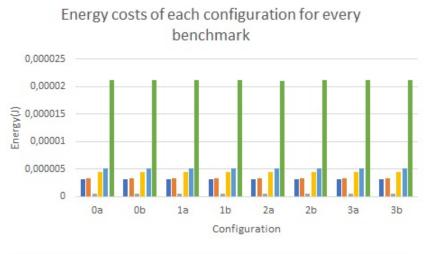

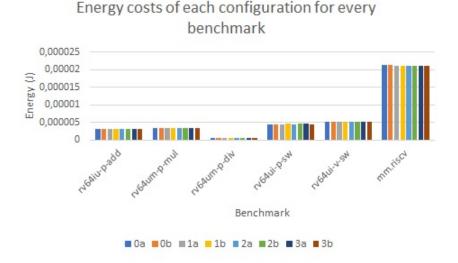

| 5.15  | Energy costs of each configuration on every benchmark           | 68 |

| 5.16  | Energy costs of each configuration on every benchmark, com-     |    |

|       | paring the benchmarks.                                          | 69 |

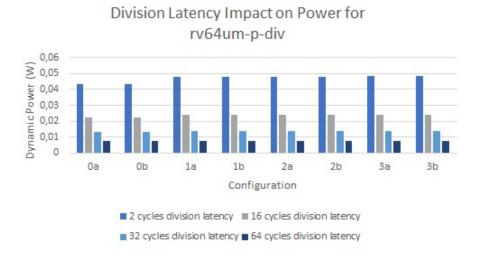

| 5.17  | Dynamic Power results chart of the rv64um-p-div test for dif-   |    |

|       | ferent division latency values                                  | 70 |

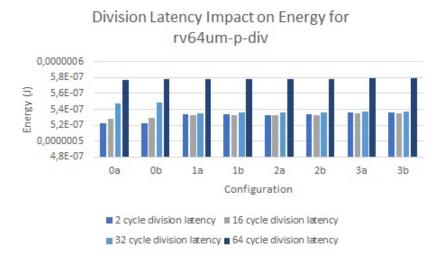

| 5.18  | Energy results chart of the rv64um-p-div test for different di- |    |

|       | vision latency values.                                          | 71 |

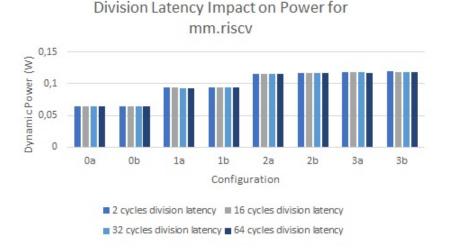

| 5.19  | Dynamic Power results chart of the mm.riscv benchmark for       |    |

|       | different division latency values.                              | 72 |

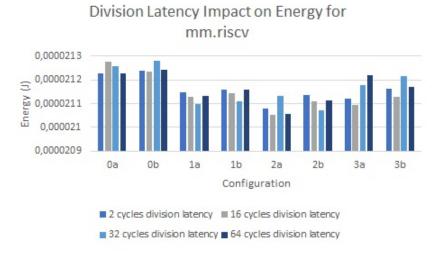

| 5.20  | Energy results chart of the mm.riscv benchmark for different    |    |

|       | division latency values                                         | 73 |

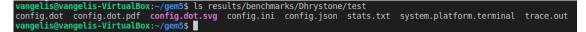

| A.1   | File structure of the experimental environment                  | 79 |

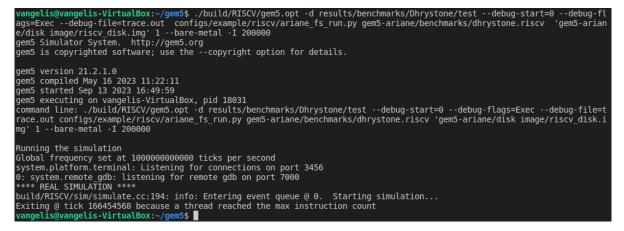

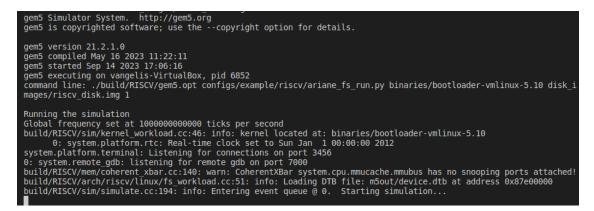

| A.2   | gem5's command line output when running the bare-metal          | 1) |

| 11.2  | simulation                                                      | 80 |

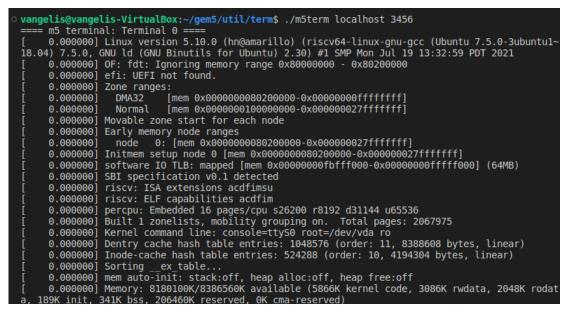

| A.3   |                                                                 | 80 |

| A.4   | gem5's command line output when running FS simulation           | 81 |

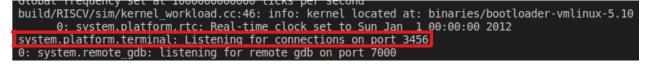

| A.5   | Port indication for the serial terminal                         | 81 |

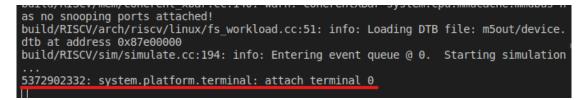

|       | Serial Terminal attached prompt                                 | 82 |

| A.7   |                                                                 | 82 |

|       | Log-in screen and command line of the simulated system          | 83 |

| 1 1.0 | Log in beloch and communication of the binterated system        | 00 |

# List of Tables

| 2.1  | RISC-V base ISA and extensions.                                | 6  |

|------|----------------------------------------------------------------|----|

| 2.2  | RISC-V privilege levels.                                       | 8  |

| 2.3  | List of RISC-V defined TVMs                                    | 15 |

| 2.4  | List of available target environments                          | 15 |

| 4.1  | Architectural design parameters reported in [2]                | 39 |

| 4.2  | Chosen Functional Unit parameters.                             | 43 |

| 4.3  | Chosen Branch Prediction Unit parameters                       | 44 |

| 4.4  | Chosen Cache parameters                                        | 45 |

| 4.5  | Chosen Pipeline Width values.                                  | 45 |

| 4.6  | Chosen CPU parameter values.                                   | 46 |

| 5.1  | Parameter values of all configurations tested                  | 54 |

| 5.2  | IPC results from the Dhrystone benchmark in bare-metal sim-    |    |

|      | ulation                                                        | 55 |

| 5.3  | Dhrystones per second and DMIPS/MHz score from the Dhry-       |    |

|      | stone benchmark in Full-System simulation.                     | 56 |

| 5.4  | Leakage Power of each configuration on every benchmark in W.   | 65 |

| 5.5  | Dynamic Power of each configuration on every benchmark in      |    |

|      | W                                                              | 66 |

| 5.6  | Energy of each configuration on every benchmark in J.          | 67 |

| 5.7  | Dynamic Power results of the rv64um-p-div test for different   |    |

|      | division latency values.                                       | 69 |

| 5.8  | Energy results of the rv64um-p-div test for different division |    |

|      | latency values.                                                | 70 |

| 5.9  | Dynamic Power results of the mm.riscv benchmark for differ-    |    |

|      | ent division latency values.                                   | 71 |

| 5.10 | Energy results of the mm.riscv benchmark for different divi-   |    |

|      | sion latency values.                                           | 72 |

|      |                                                                |    |

# List of Abbreviations

| ALU    | Arithmetic Logic Unit                               |

|--------|-----------------------------------------------------|

| ASIC   | Application Specific Integrated Circuit             |

| API    | Application Programming Interface                   |

| BHT    | Branch History Table                                |

| BTB    | Branch Target Buffer                                |

| BOOM   | Berkley Out of Order Machine                        |

| CSR    | Control and Status Registers                        |

| CMOS   | Compilmentary Metal Oxide Semiconductor             |

| CPI    | Cycles Per Instruction                              |

| CLINT  | Core Local Interrupt Controller                     |

| CPU    | Central Processor Unit                              |

| DDR3   | Double Data Rate type 3 memory                      |

| DMIPS  | Dhrystone Million Instructions Per Second           |

| DSL    | Domain Specific Language                            |

| DVFS   | Dynamic Voltage Frequency Scaling                   |

| DTB    | Device Tree Blob                                    |

| ELF    | Executable and Linkable Format                      |

| FS     | Full System                                         |

| FPGA   | Field Programmable Gate Array                       |

| FU     | Functional Unit                                     |

| FPU    | Floating Point Unit                                 |

| FD-SOI | Fully Depleted-Silicon On Insulator                 |

| FIFO   | First In First Out                                  |

| FESVR  | Front-End Server                                    |

| GCC    | GNU Compiler Ccollection                            |

| IPC    | Instructions Per Cycle                              |

| ISA    | Instruction Set Architecture                        |

| ITRS   | International Technology Roadmap for Semiconductors |

| KVM    | Kernel-based Virtual Machine                        |

| LSU    | Load Store Unit                                     |

| MMU    | Memory Management Unit                              |

|        | -                                                   |

xviii

| MIPS   | Million Instructions Per Second     |

|--------|-------------------------------------|

| OS     | Operating System                    |

| 03-000 | Out-Of-Order                        |

| PC     | Program Counter                     |

| PTW    | Page Table Walker                   |

| PMA    | Physical Memory Attribute           |

| PLIC   | Platform-Level Interrupt Controller |

| RISC   | Reduced Instruction Set Computer    |

| ROB    | Reorder Buffer                      |

| RTL    | Register Transfer Level             |

| RAS    | Return Address Stack                |

| RAM    | Random Access Memory                |

| SoC    | System-on-Chip                      |

| SE     | Systemcall Emulation                |

| SDK    | Software Development Kit            |

| SIMD   | Single Instruction Multiple Data    |

| TDP    | Thermal Design Power                |

| TLB    | Translation Lookaside Buffer        |

| TVM    | Test Virtual Machine                |

| VLIW   | Very Long Instruction Word          |

Dedicated to my family and friends...

### Chapter 1

# Introduction

#### 1.1 Motivation

With the demand for computer chips growing, the design and simulation can become a complex, costly, and time-consuming process. There are different approaches when designing computer hardware. Designers, usually use hardware description languages (HDL), such as VHDL or SystemVerilog, to implement their architectures and simulate them using register-transfer level (RTL) simulators. RTL simulators can simulate real hardware designs in great detail and cycle accuracy and also provide accurate estimations on power consumption and hardware area. However, implementing the designs can be a complex process that limits design space exploration, and simulations can be very time-consuming, even taking up to days, when simulating real-world applications, depending on the complexity of the simulated system. Another approach is to run their RTL designs on FPGAs. The simulation times can be orders of magnitude faster compared with the RTL simulators due to the execution taking place on real hardware. Nonetheless, implementation of the designs and acquisition of performance statistics can be a complex task, and investing in FPGA hardware can be costly. Furthermore, in-depth testing demands tailored OS support with its associated software development effort across the stack.

Micro-architectural simulators offer faster simulations, compared to RTL simulators, by modeling hardware modules at higher levels of abstraction. This, allows designers to easily simulate and measure the performance of various architectures at relatively fast simulation speeds, making them great for design space exploration. Also, most of these architectural simulators offer complete OS support, thus their use eliminates software developmentrelated costs. Their capability to simulate both hardware and OS implementations and to measure their interaction, makes them suitable for softwarehardware co-design exploration, too. Notably, such simulators are widely used as implementation and measurement tools by the research community. However, high-level abstraction models can lead to a great loss of accuracy, because they omit low-level details that can affect performance. The gem5 Simulator is a micro-architectural simulator that has gained popularity in both academia and industry. gem5 offers a great variety of instruction set architectures and highly configurable hardware models, an easy-to-use frontend interface and the capability to simulate a full operating system. Furthermore, gem5's open-source license makes it accessible to researchers, students and the industry.

Despite gem5 being open source, most of the ISAs supported have proprietary licenses. A solution to this comes with the addition of the RISC-V ISA to gem5. RISC-V offers an open and simple instruction set that can implement numerous architectures, from low-cost embedded to high-end processors, through its ISA extensions. The addition of RISC-V to gem5, offers an alternative simulation framework for RISC-V, bridging the gap between RTL simulation and ISA simulation with simulators such as Spike [1]. With the growing popularity of RISC-V, the accuracy of gem5's models in the context of RISC-V becomes of great importance. Especially, if we consider that the RISC-V related implementations in the gem5 simulator are still premature.

### 1.2 Objectives

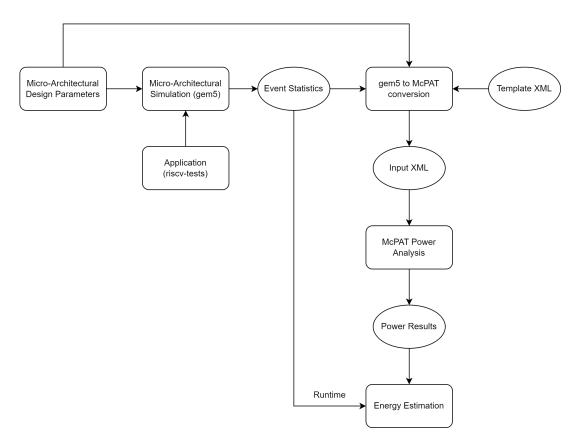

This work focuses on the issue of micro-architectural simulator accuracy, specifically for the recently added RISC-V framework of gem5. The main objective of this thesis is to match the energy costs and performance of an ASIC implementation of a RISC-V CPU, particularly Ariane, with a simulated RISC-V system and point out weaknesses and possible accuracy loss sources of the simulator.

First of all, the author developed configuration scripts on gem5's front-end that set up the simulated system and run the simulation, on gem5's Full-System and bare-metal modes. In addition, the author developed scripts that model Ariane's pipeline and main architectural modules, using gem5's detailed CPU models, that can either be combined with the configuration scripts developed by the author or gem5's default configuration scripts with minimal modifications, to simplify the configuration and calibration of the system's micro-architectural design parameters. Furthermore, in order to run in Full-System mode, the author used a RISC-V built Linux kernel along with a compatible disk image.

Since gem5 does not produce power and energy statistics, the author used scripts that integrate gem5 with a power simulator, and in particular McPAT. Specifically, the author used scripts that use gem5's output files along with an input template and produce an input file that can be used by McPAT. Moreover, the author modified the template XML file in order to match Ariane's specifications and enable it to be used with gem5's latest version, specifically in this study, version 21.2.1.

To evaluate the performance of the simulated system, the author created a baseline configuration of the simulated system and simulated benchmarks from the *riscv-tests* suit on the base configuration and on multiple configurations of the base model with calibrated micro-architectural design parameters. Particularly, the author selected several tests and benchmarks from the suite that match the workload described in [2], modified the assembly tests to run longer in order to obtain more meaningful power and performance statistics and ported them in order to be used with the gem5 simulator, using the cross-compilers of the RISC-V toolchain. Last but not least, the author compared the results of the simulation to the published performance, power and energy statistics and analyzed the possible causes of accuracy loss in the gem5 simulator.

#### 1.2.1 Contributions

This study offers an early-stage analysis of possible accuracy errors of the gem5 simulator in the context of the recent RISC-V related implementations. It provides a starting point for further research on the support of RISC-V in gem5 pointing out weaknesses of the simulator.

Furthermore, this project provides an in-depth guide on development with gem5's RISC-V framework on bare-metal and Full-System simulation, show-casing possible challenges during development. Specifically, it offers details on the use and implementation of configuration scripts on gem5's front-end, that setup and the simulation of the target system, utilizing gem5's detailed

models. In addition, we present the utilization of the *gem5-resources* library and the compatibility of the RISC-V toolchain with gem5. Moreover, we demonstrate the integration of gem5 with external tools, in this case, McPAT, along with the challenges that occur.

### 1.3 Thesis Outline

- Chapter 2 Theoretical Background: provides a theoretical basis on the RISC-V instruction set architecture and the RISC-V software and hardware ecosystem, the RISC-V core used in this study (CVA6 Ariane), the benchmarks and the tools used, gem5 and McPAT.

- Chapter 3 Related Work: explores related work on micro-architectural simulation and accuracy evaluation using gem5 and McPAT. Specifically, it presents previous work on the accuracy evaluation of the gem5 simulator in the context of the ARM instruction set, the implementation, functional validation and accuracy evaluation of the RISC-V instruction set in gem5, the integration of gem5 with external tools and McPAT and accuracy evaluation of the McPAT power simulation.

- Chapter 4 Simulation Environment Setup and Implementation: describes the experimental environment setup and the simulation framework, providing detail on the implementation of the configuration scripts, the setup and the modifications on the benchmarks used, the implementation and the micro-architectural design parameter selection for the baseline model.

- Chapter 5 Results and Performance Analysis: describes the calibration of the micro-architectural design parameters of the baseline model and the parameter selection for the calibrated configurations, the experiments conducted in order to obtain the performance, power and energy statistics and comparison between the results and the published statistics.

- Chapter 6 Conclusions and Related Work: draws conclusions and gives directions for future work.

### Chapter 2

# **Theoretical Background**

## 2.1 RISC-V Architecture and Simulation Environments

#### 2.1.1 **RISC-V Instruction Set Architecture**

RISC-V is a freely licensed and open standard instruction set architecture, introduced by the University of California, Berkeley in 2010. It offers a simple load-store instruction set with principals similar to other RISC architectures. It has gained popularity both in industry and academia through its simplicity and its improvements compared to other open ISAs [3]. RISC-V provides both 32-bit and 64-bit instruction sets along with various extensions (e.g. compressed instructions, vector operations, and more that are ongoing work at the time of writing this thesis). The base instruction set is split into user-level and privileged instructions, with the latter enabling additional functionality required for running an operating system.

#### **RISC-V** Instruction set organization

The RISC-V ISA consists of three base instruction sets that support 32 and 64-bit registers and a variety of extensions that can be added to one of the base instruction sets. This allows RISC-V to be implemented in a wide range of applications from low-cost embedded processors to high-end processors with sophisticated designs and multi-core configurations. A common form of the base ISA with standardized extensions is *RV64IMAFD*, which implements the RV64I base integer ISA with the M extension for multiply/divide support, A extension for atomic memory operations and F for single and D for double precision IEEE floating point support. This is often abbreviated

as *RV64G*, G meaning general purpose, with *RV32G* being the 32-bit subset. Table 2.1 lists base instruction sets and standard extensions with their descriptions.

| Name   | Functionality                                                                  |  |  |  |  |  |  |

|--------|--------------------------------------------------------------------------------|--|--|--|--|--|--|

| RV32I  | Base 32-bit integer instruction set, with 32 registers                         |  |  |  |  |  |  |

| RV32E  |                                                                                |  |  |  |  |  |  |

| RV64I  | Base 64-bit integer instruction set                                            |  |  |  |  |  |  |

| RV128I | Base 128-bit integer instruction set                                           |  |  |  |  |  |  |

| М      | Adds integer multiply and divide instructions                                  |  |  |  |  |  |  |

| А      | Adds support for atomic instructions                                           |  |  |  |  |  |  |

| F      | Adds single precision (32-bit) IEEE floating point                             |  |  |  |  |  |  |

| D      | Extends floating point to double precision                                     |  |  |  |  |  |  |

| Q      | Further extends floating point to add support for quad precision               |  |  |  |  |  |  |

| L      | L Adds support for 64- and 128-bit decimal floating point for the IEEE standar |  |  |  |  |  |  |

| С      | Defines a 16-bit compressed version of the instruction set                     |  |  |  |  |  |  |

| В      | Standard extension for bit manipulation                                        |  |  |  |  |  |  |

| J      | Adds support for Dynamically Translated Languages                              |  |  |  |  |  |  |

| Т      | Adds support for Transactional Memory                                          |  |  |  |  |  |  |

| Р      | Adds Packed-SIMD instruction support                                           |  |  |  |  |  |  |

| V      | Adds support for Vector operations                                             |  |  |  |  |  |  |

| Ν      | Standard extension for user-level interrupts                                   |  |  |  |  |  |  |

| Н      | Standard extension for Hypervisor                                              |  |  |  |  |  |  |

| S      | Standard extension for Supervisor-level instructions                           |  |  |  |  |  |  |

TABLE 2.1: RISC-V base ISA and extensions.

#### **RISC-V** Registers, Data structures and Addressing modes

RV64G uses 32 64-bit general-purpose registers, *x0*, *x1*,...,*x31*, also known as *integer* registers, with x0 being the *zero* register. The supported data types for integer data are 8-bit bytes, 16-bit half-words, 32-bit words and 64-bit for double-words. Half-words are included as they are commonly found in languages like C and are popular in programs, such as operating systems. Bytes, half-words and words are loaded to the general-purpose registers with either zeros or the sign bit repeated to fill the 64 bits of the register.

The F and D extensions add 32 floating point registers, *f0*, *f1*,...,*f31*, that can hold 32-bit single precision or 64-bit double precision values. When holding single-precision values, the upper half of the register is unused. Operations for single and double-precision floating-point are provided.

There are two data addressing modes, immediate and displacement, both with 12-bit fields. Placing 0 in the 12-bit field enables register indirect mode, while using the *zero* register as a base register enables limited absolute addressing. The RV64G memory is byte addressable with a 64-bit address and uses little-endian byte numbering. RISC-V is a load-store architecture and

| 31        | $25 \ 24$ | 20 19  | 15 14 12 | 2 11 7   | 6      | 0      |

|-----------|-----------|--------|----------|----------|--------|--------|

| funct7    | rs2       | rs1    | funct3   | rd       | opcode | R-type |

|           |           |        |          |          |        |        |

| imr       | n[11:0]   | rs1    | funct3   | rd       | opcode | I-type |

|           |           |        |          |          |        |        |

| imm[11:5] | rs2       | rs1    | funct3   | imm[4:0] | opcode | S-type |

|           |           |        |          |          |        |        |

|           | imm[3     | 51:12] |          | rd       | opcode | U-type |

FIGURE 2.1: RISC-V Instruction Formats, taken from [5].

all references between the memory and the general-purpose or floating point registers are through load-stores. Memory accesses don't have to be aligned, however, unaligned accesses are extremely slow [4].

#### **RISC-V Instruction Formats**

There are four core instruction formats R, I, S and U, as shown in Figure 2.1, all of which have a fixed length of 32-bits with a 7-bit opcode. All instructions must be aligned on a 4-byte boundary memory. A misaligned taken branch or unconditional jump can generate an *instruction address misaligned* exception if the target address is not 4-byte aligned.

The source (rs1 and rs2) and destination (rd) registers are in the same positions throughout all instruction formats except for the 5-bit immediate Control/Status Register (CSR) instructions. Immediate values are always sign extended and the sign bit is always bit 32. The *opcode* specifies the instruction type while the *funct* specifies the specific operation. Several formats can encode multiple types of operations, such as the I-format which can encode both ALU immediate and load instructions and the S-format for stores and conditional branches.

There are two additional formats, B and J, that are used based on the handling of the immediate. The B format is a variant of the S format, written also as SB, and it is used for conditional branches, and the J format is a variant of the U format, written also as UJ, used for jump instructions. Figure 2.2 shows all RISC-V instruction formats along with SB and UJ.

#### **RISC-V** Privilege modes

The privileged instruction set is independent from the user-level ISA and it includes different levels of hardware support needed to run an operating system.

| 31                       | 30                               | 25  | 24 2                      | 1 20                           | 19     |       | 15   | 14  | 12        | 11    | 8                   | 7      | б   | U   |         |

|--------------------------|----------------------------------|-----|---------------------------|--------------------------------|--------|-------|------|-----|-----------|-------|---------------------|--------|-----|-----|---------|

|                          | funct7                           |     |                           | rs2                            |        | rs1   |      | fu  | unct3     |       | $\operatorname{rd}$ |        | opc | ode | R-type  |

|                          | 1                                | -1  |                           | 1                              |        |       |      |     |           |       |                     |        |     |     |         |

| imm[1]                   | $\left  \text{ imm}[10] \right $ | :5] | imm[4:1                   | $] \mid \operatorname{imm}[0]$ |        | rs1   |      | fu  | inct3     |       | $\mathbf{rd}$       |        | opc | ode | I-type  |

| imm 11                   | []  imm[10]                      | :5] |                           | rs2                            |        | rs1   |      | fu  | inct3     | imm[4 | :1                  | imm[0] | ODC | ode | S-type  |

| L                        | ][                               | ]   |                           |                                |        |       |      |     |           |       | 1                   | [_]    | -1- |     |         |

| $\operatorname{imm}[12]$ | 2 imm[10]                        | :5] |                           | rs2                            |        | rs1   |      | fu  | unct3     | imm[4 | l:1] i              | mm[11] | opc | ode | SB-type |

|                          |                                  |     | ,                         |                                |        |       |      |     |           |       |                     |        |     | -   |         |

| $\operatorname{imm}[3]$  | .]                               | in  | m[30:20]                  |                                | im     | m[19: | 15   | imn | n[14:12]  |       | rd                  |        | opc | ode | U-type  |

| [ . [or                  |                                  |     | . [                       | 11. [44                        | 11.    | [10   | 1 21 |     | [1 4 1 2] |       |                     |        |     |     |         |

| $\operatorname{imm}[20]$ | $0] \mid \text{imm}[10]$         | :5] | $\operatorname{imm}[4:1]$ | ]   imm[11                     | ]   im | m[19: | 15   | ımn | n[14:12]  |       | $\mathbf{rd}$       |        | opc | ode | UJ-type |

FIGURE 2.2: RISC-V Instruction Formats including SB and UJ, taken from [5].

There are four currently available main privilege levels, user, supervisor, hypervisor and machine. The privilege levels provide protection between components in the software stack. Operations that are not permitted in a specific privilege level can raise an exception, which is handled by a trap.

TABLE 2.2: RISC-V privilege levels.

| Level | Encoding | Name             | Abbreviation |

|-------|----------|------------------|--------------|

| 0     | 00       | User/Application | U            |

| 1     | 01       | Supervisor       | S            |

| 2     | 10       | Hypervisor       | Н            |

| 3     | 11       | Machine          | М            |

Machine level (M-mode) has the highest privileges and it is the only mandatory level required in an RISC-V machine. Code that runs in machine mode is trusted and it has low-level access to the machine implementation. The M-mode is used to manage secure execution environments in RISC-V systems. All implementations must provide M-mode, the simplest implementation can provide only M-mode, however, this implementation lacks protection.

User mode (U-mode) and supervisor mode (S-mode) are intended for conventional applications and operating system usage respectively. Hypervisor mode (H-mode) is intended for virtual machine monitors. S-mode provides isolation between the operating system and the supervisor execution environment and hardware abstraction layer code, while H-mode provides isolation between the virtual machine monitor and hypervisor execution environment and hardware abstraction layer running in machine mode.

A hardware thread runs in U-mode until a trap forces a switch to a trap handler. The thread will execute the trap handler and resume at or after the original instruction that caused the trap in U-mode. Traps that increase the privilege level are called *vertical traps*, while traps that remain at the same level are called *horizontal traps*.

Implementations may include a debug mode (D-mode) that supports offchip debugging and manufacturing tests. D-mode gives even more access than M-mode, thus, it can be considered an additional privilege mode. It may reserve CSR addresses and portions of physical memory.

#### **RISC-V Software Ecosystem**

RISC-V software compilation is supported through *GCC* and *LLVM*, with the *RV32GC* and *RV64GC* instruction set extensions being implemented and the *RV32E* base ISA supported only on *GCC*. The GNU C library, *Glibc*, along with the *Newlibc*, which is the C standard library implementation for embedded systems, are supported. Furthermore, the GNU *Binutils*, which is a collection of binary tools, is supported and debugging is provided via the GDB (GNU Debugger). Although the base instruction sets and standard extensions have been implemented, they have not yet been fully optimized.

Emulation of RISC-V systems can be achieved using *QEMU* [6]. QEMU is a free and open-source machine emulator and can support full-system emulation for RISC-V systems. It supports both 32 and 64-bit base instruction sets and standard extensions, along with privileged and unprivileged instruction specifications. Furthermore, RISC-V systems can be simulated using *Spike* [1]. Spike is the RISC-V ISA simulator and implements a functional model. It supports the latest versions of privileged and unprivileged instruction specifications and all base RISC-V instruction sets along multiple standard and non-standard extensions. This enables Spike to be used as a reference model. Spike can simulate RISC-V systems with one or more hardware threads.

#### 2.1.2 CVA6 (former Ariane)

CVA6 is an application-class 64-bit RISC-V CPU core, fabricated under *GlobalFoundries* 22nm FD-SOI technology [2]. The core runs at 1.7GHz and, as they report [2], achieves an efficiency of up to 40Gop/sW. Ariane implements the *RV64GC* ISA and has a 6-stage, single issue, in-order pipeline with full hardware support for multiply/divide, atomic memory operations as well as an IEEE-compliant floating point unit. It supports the compressed as well as the full privileged instruction set extensions. The instructions are issued

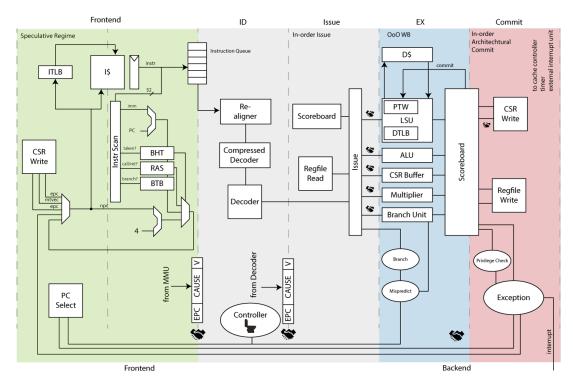

in-order and executed out-of-order. The core's front-end consists of a *PC generation* stage and the instruction *Fetch* stage, while the back-end consists of the *Decode*, instruction *Issue*, *Execute* and *Commit* stages. Figure 2.3 shows Ariane's 6-stage pipeline.

The *PC generation* stage is responsible for selecting the next PC. The next PC can originate from a return from an environment call, an interrupt or exception, a branch prediction or a falsely predicted branch, a pipeline flush due to CSR side effects, the debug interface, or a consecutive fetch. The *Fetch* stage contains fetch and pre-decode logic, the instruction cache, and the branch prediction units. It receives information from the PC stage, asks the MMU for an address translation on the requested PC and controls the instruction cache. The data coming from the instruction cache, are registered before being predecoded. As a result, a cycle is lost, even on a correct control flow prediction, as the next PC cannot be calculated in the same cycle that the data from the instruction cache is received. They report that, due to the compressed instruction set extension, they fetch on average 1.5 instructions, thus, the lost cycle does not cause a problem. The pipeline's front-end is fully decoupled from the back-end using the instruction queue, which is implemented as a FIFO of configurable depth. The instruction queue stores the instructions in compressed form.

The first stage of the core's back-end is the *Decode* stage. The decode stage realigns potentially unaligned instructions, decompresses them and decodes them, The decoded instructions are then put in an issue queue. The *Issue* stage houses the issue queue, the scoreboard and the Reorder Buffer (ROB). When the operands are ready the instructions are issued in the execute stage. The *Execute* stage contains all the functional units. Ariane has six functional units, the ALU, a multiplier/divider, a CSR buffer, a Branch Unit, a Load-/Store unit (LSU) and a floating point unit (FPU). Every functional unit is handshaken and readiness is taken into account during the instruction issue. The instructions can retire out-of-order from the functional units and writeback conflicts are resolved through the ROB. Finally, the *Commit* stage reads from the ROB and commits all instructions in program order and the register file is updated. The commit stage can commit two instructions per cycle.

Ariane's main units and key features:

• **Branch Prediction:** A Branch History Table (BHT) with 8 entries and a 2-bit saturating counter, a Branch Target Buffer (BTB) with 8 entries and a Return Address Stack (RAS).

FIGURE 2.3: Ariane's 6-stage Pipeline.

- Virtual Memory: Full hardware support for address translation via the Memory Management Unit (MMU). The MMU contains data and instruction TLBs with 16 entries each as well as a Page Table Walker (PTW). Ariane implements a 39-bit, page-based virtual memory scheme, *SV39*.

- **Register Files:** Two physically different register files for integer and floating-point registers, containing 32 64-bit registers.

- Scoreboard/Re-order Buffer: Implemented as a circular buffer, contains issued, decoded, in-flight instructions and speculative results written back by various FUs.

- **Caches:** 16kB 4-way instruction cache with a latency of 1 cycle, 32kB 8-way data cache with a latency of 3 cycles. Both data and instruction caches are virtually indexed and physically tagged and include an additional pipeline stage on their outputs. The data cache is a write-back cache and supports hit under miss functionality.

- Memory and Control Interfaces: Advanced eXtensible Interface (AXI)

5 master port and four interrupt sources, Machine External Interrupts, Supervisor External Interrupts, Machine Timer Interrupts, Machine Software Interrupts.

#### • Functional Units:

- ALU: Covers most of the base RISC-V ISA, including branch target calculations.

- Load/Store Unit (LSU): Integer and floating-point load/stores as well as atomic memory operations.

- Floating-point Unit (FPU): IEEE compliant floating-point unit with custom trans-precision extensions.

- Branch Unit: An extension to the ALU, handles branch-prediction and branch-correction.

- CSR: RISC-V mandates atomic operations on its CSR, corresponding write data is buffered in this unit and read again when the instruction retires.

- Multiplier/Divider: Fully pipelined 2-stage multiplier and a bitserial divider with input preparation, takes 2-64 cycles depending on the operands.

Ariane supports the privileged ISA specification and implements user, supervisor and machine privilege levels as well as a RISC-V compliant *Debug* interface. The debug interface requires one additional instruction, *dret*, to return from debug mode. The communication with the external debugger is done through a debug module peripheral.

The core has been taped-out in *GlobalFoundries* 22 FDX technology node and uses a shared System on Chip(SoC) for off-chip communication. Ariane can communicate with the SoC via a full-duplex 64-bit AXI interconnect. The SoC contains 520kB of on-chip scratchpad memory, HyperRAM, SPI, UART and I2C. The core is separately clocked, supplied and powered and the logic cells can be forward body biased to increase speed at the expense of leakage power. The design has been signed-off at 902 MHz at 0.72 V, 125 C, SSG with the final netlist containing 75.34% low voltage threshold and 24.66% super low voltage threshold cells.

With this architecture, they report up to 1.65 DMIPS/MHz depending on the branch-prediction configuration and load latency and an IPC of 0.82 on the *Dhrystone* benchmark with a 128-entry BHT and 64-entry BTB configuration. They report a total leakage of 1.08 mW and a total energy of 51.80 pJ for a generalized matrix multiplication.

A version of Ariane has also been fabricated with *Ara* [7] in *GlobalFoundries* 22 FDX technology. Ara is a 64-bit vector co-processor that implements RISC-V's vector extension. It runs at more than 1GHz and achieves a performance of 33 DP-GFLOPS and energy efficiency of 41 DP-GFLOPS/W.

#### 2.1.3 Alternative RISC-V Hardware

Since the RISC-V ISA was introduced, there have been multiple cores and SoCs that implement the RISC-V architecture. [8] lists several RISC-V cores and SoCs along with their status.

A notable platform widely used in research is the *Rocket Chip generator* [9], developed at UC Berkeley. The Rocket Chip generator is an SoC generator, written in Chisel HDL [10], that uses configurable chip-building libraries for constructing RISC-V based SoCs. It provides a core generator, with optional FPUs, configurable FU pipelines and branch predictors, cache and TLB generators with configurable size, associativity and replacement policies and a generator for peripherals. The generator supports multicore configurations, cache-coherence and heterogeneity through the tile generator and a Rocket Custom Co-processor interface (*RoCC*) for application-specific co-processors. It uses the Rocket Core by default and can also be configured to use the BOOM out-of-order core.

The *Rocket Core* is a 5-stage in-order scalar core that implements the RV32G and RV64G instruction sets, written in Chisel HDL. Rocket has a non-blocking data cache and supports branch prediction through a BHT, a BTB and a RAS in its instruction fetch stage. The core uses the Chisel floating-point implementations for its' floating point units. Address translation is supported by the MMU, with a page-based virtual memory, and supports the RISC-V machine, supervisor and user privilege levels. The Rocket core can also be used as a component library, and many of Rocket's modules can be used in different designs. The Rocket Chip, and Rocket Core, have been taped out multiple times and produced functional silicon chips capable of running Linux.

The *Berkley Out-of-Order Machine (BOOM)* [11] is an open-source synthesizable and parametric out-of-order superscalar RISC-V core that implements the RV64GC instruction set. The first version of BOOM was used for educational purposes, it was similar to the *MIPS R10k* core and featured a simple pipeline with a unified register file. The second version, *BOOM v2* [12], expanded the front-end pipeline stages, modified the branch prediction units, separated the floating-point into an independent pipeline and split the issue queue into separate queues for integer, memory and floating-point operations. BOOM v2 was fabricated in the *BROOM* chip [13], in 28 nm TSMC technology. The third version of BOOM, *SonicBOOM* [14], improved upon bottlenecks of the previous versions, modifying the instruction fetch unit, execution back-end and load/store unit, and added a high performance *TAGE* branch predictor. Furthermore, they added support for the RISC-V compressed instruction set. BOOM was written in Chisel HDL and adopts components from the in-order *Rocket Core*, such as the MMU, L1 caches and execution units.

#### 2.2 Benchmarks

Benchmarks are computer programs used to measure, compare and evaluate the relative performance of a computer system. There are different types of benchmarks such as kernels, small programs that include key aspects of realworld programs, or toy programs, however, they could be characterized into two main categories: synthetic benchmarks and application ("real-world") based. Synthetic benchmarks are fake programs, usually small in size, that try to mimic the behavior of real-world applications, often used to measure or debug specific features of a system. Application based benchmarks use software from real applications and are used to measure the overall performance of a system. Usually, they have large code and data storage requirements.

Collections of benchmark applications are called *benchmark suites*, and they are a popular measure of the performance of processors with a variety of applications. A key advantage of benchmark suites is that the weakness of any benchmark is lessened by the presence of the others. [4] Popular benchmarks and benchmark suites commonly used in academia and the industry include the *Standard Performance Evaluation Corporation* (SPEC) suite, with its' current version being the *SPEC2017*, the EEMBC CoreMark benchmark and CoreMark Pro suite, the PARSEC suite and many more.

For this project, based on the reported workload used in [2], we used tests from the *riscv-tests* suite and the *Dhrystone* benchmark, to match the reported energy costs and performance of Ariane, respectively.

#### 2.2.1 RISCV-Tests suite

RISC-V tests is an extensive assembly test suite in the open-source RISC-V toolchain. The test suite is designed to run on bare-metal machines without any OS support and communicates to a host machine via a front-end server (FESVR) to inform the results. It consists of ISA compliance tests and low-level C tests. The tests are built on various *Test Virtual Machines (TVM)* and can run on different target environments depending on the number of cores and type of memory on the system.

| TVM Name | Description                                          |

|----------|------------------------------------------------------|

| rv32ui   | RV32 user-level, integer only                        |

| rv32si   | RV32 supervisor-level, integer only                  |

| rv64ui   | RV64 user-level, integer only                        |

| rv64uf   | RV64 user-level, integer and floating-point          |

| rv64uv   | RV64 user-level, integer, floating-point, and vector |

| rv64si   | RV64 supervisor-level, integer only                  |

| rv64sv   | RV64 supervisor-level, integer and vector            |

TABLE 2.3: List of RISC-V defined TVMs.

Each test uses only features of a given *TVM*. Table 2.1 lists the TVMs currently defined for RISC-V, all of which only support a single hardware thread. These features are defined as the set of registers and instructions that can be used, the portions of memory that can be accessed, the way execution starts and ends and the test data input and output. Each test is contained within a single assembly file which is passed through the C pre-processor and should include the *riscv\_test.h* header file which defines macros used by the given *TVM*. This header file differs depending on the target environment. Table 2.2 shows all available target environments. All assembly directives can be used in the test file.

TABLE 2.4: List of available target environments.

| Target Env. | Description                                                  |

|-------------|--------------------------------------------------------------|

| p           | physical memory only, only core 0 boots up                   |

| pm          | physical memory only, all cores boot up                      |

| pt          | physical memory only, timer interrupt fires every 100 cycles |

| v           | virtual memory is enabled, only core 0 boots up              |

Each test program should include the appropriate TVM macro, which specifies the TVM that the test is built on. The format of the macro that defines the possible TVMs is: *RVTEST\_RV[32/64]U(F/V)* or *RVTEST\_RV[32/64]S*. The 32 or 64 defines 32 or 64-bit instruction decoding, the U is for user space while S is for supervisor. When using user space, F means that the floating point unit is enabled and V is used to enable the vector unit. On supervisor, it is assumed that floating point and vector units are enabled.

Execution begins when the *RVTEST\_CODE\_BEGIN* macro is reached and continues until it reaches the *RVTEST\_PASS* or *RVTEST\_CODE\_END* macros, if the test succeeds, or *RVTEST\_FAIL* if the test fails. The end macros signal the appropriate execution code to the *FESVR* through the *tohost* register to end the execution. The least significant bit of the *tohost* register indicates whether the message sent to the *FESVR* is a system call that needs to be executed if the value is 0, or program termination if the value is 1.

A test data section should be contained in each test, this section is contained within the *RVTEST\_DATA\_BEGIN* and *RVTEST\_DATA\_END*. There is no guaranteed alignment for the start and end of the data section, so regular assembly alignment instructions can be used to ensure desirable alignment of data values. The region of memory which holds the test data section, will be captured at the end of each test to act as a signature from the test.

All test programs contain self-checking code to check the result of the instruction tested. However, this cannot be the only testing strategy since it relies on the correct functioning of the processor instructions used to implement the check.

A timeout facility should be included in any given target environment for running the tests. Tests that do not complete their execution within a given time threshold are classed as failing.

#### 2.2.2 Dhrystone

*Dhrystone* [15], is a synthetic computing benchmark program created by Reinhold P. Weicker in 1984. The benchmark was first published in Ada in 1984 and later a C version was published by Rick Richardson. The C version of Dhrystone is the most popular one used in industry to measure CPU performance. Dhrystone only measures the performance of integer operations, thus it was named as an integer counterpart of the then popular benchmark *Whetstone*, which was used for floating point operations.

To develop Dhrystone, Weicker gathered information from a wide range of then-popular software and characterized them in terms of various common constructs. It is designed to statistically mimic the processor usage of common sets of programs. Dhrystone's code consists of simple integer arithmetic and logic operations, string operations and memory accesses in order to reflect CPU activity in the most general-purpose computing applications.

Dhrystone produces a *Dhrystones per Second* result, which indicates how many times the program's main loop was executed within a second. A common representation of the program is *DMIPS*, which is obtained by dividing the Dhrystone score by 1757. The number 1757 is the score produced on *VAX 11/780*, which is nominally a 1 MIPS machine. To enable processor performance comparison at different clock speeds, the *DMIPS* measure can be further normalized into *DMIPS/MHz* by dividing the *DMIPS* value by the CPU's clock speed.

Dhrystone possesses features that have allowed it to gain popularity. These features are The portability of its code, allowing it to be easily ported to a large number of platforms and applications, small and easy-to-use and understand code, single easy-to-report score and a free license. Furthermore, its integer code can make it useful as an 8 and 16-bit micro-controller benchmark.

However, Dhrystone has a lot of notable weaknesses [16], [17]. Its' small code can fit into a modern processor's L1 cache memory, minimizing or eliminating the stress on the memory system. Furthermore, compiler optimizations can greatly affect its performance with optimizations such as inline code and dead code removal. A large portion of the benchmark consists of string operations using standard C library functions such as *strcpy()* and *strcmp()* which are highly optimized in common compilers. As a result, Dhrystone's performance and results can vary depending on the compiler used. To address some of these issues an improved version of Dhrystrone [18] was released by Weicker and Richardson in 1988 (Version 2.1). Although this version improves upon compiler optimization dependencies of the benchmark, it does not eliminate them completely. Version 2.1 is the latest version of the benchmark released to date.

In addition, due to its focus on integer operations, it cannot test and demonstrate the capabilities of modern CPUs. It confines itself in the micro-architectural level and does not take into account features commonly used by modern systems such as RISC architectures, sophisticated floating point and vector units, super-scalar RISC designs, VLIW processors, real-time operating systems with sophisticated APIs and graphical user interfaces, failing to represent real-life applications.

Despite its shortcomings, Dhrystone remains quite popular to this day, however, it should not be the only benchmark used when measuring the performance of a system.

#### 2.3 The gem5 Simulator

The gem5 Simulator [19, 20] is a modular discrete event-driven computer system simulator platform, created by merging the best aspects of *M*5 [21] and *GEMS* [22] simulators. It offers a flexible, modular and highly configurable design, allowing it to simulate a wide range of systems, that cover a wide range of speed/accuracy trade-offs. gem5 provides a variety of ISA-independent components, such as CPUs, memory models and peripheral devices, and two execution modes with the capability to simulate a full operating system. gem5 supports most commercial ISAs, including ARM, x86, MIPS, ALPHA, Power, SPARC and RISC-V.

#### 2.3.1 Key Features and Capabilities

gem5 is mostly written in *C*++ and provides a *Python* interface. All major simulation objects are *SimObjects*, including models of hardware components, such as processor core, caches, buses and peripheral devices, as well as more abstract entities such as workload. Every SimObject is represented by two classes, one in C++ and one in Python. The C++ class defines the SimObject's implementation, state and behavior, while the Python class is used for instantiation, naming and setting the object's parameter values. The simulated system is built using a Python configuration script which provides initialization, configuration and simulation control. All simulated components are defined and configured in the Python script. The standard *main()* function, along with all command-line processing and start-up code is written in Python. When the simulation begins, the Python script is executed almost immediately in start-up.

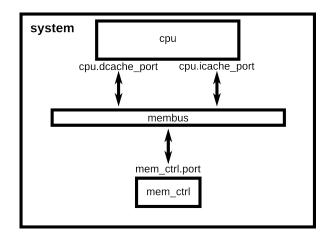

gem5 supports two simulation modes, System-call Emulation (SE) and Full-System (FS) mode. In SE mode, gem5 executes user-level binaries without executing the kernel-mode system calls of a real operating system. When

FIGURE 2.4: Simplest system that can be simulated in SE mode, adapted from gem5.org.

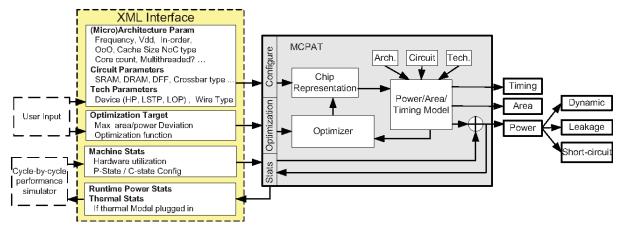

the program executes a system call, gem5 traps it and emulates it by passing it to the host operating system. Only Linux system calls are supported in SE mode, and as a result, supports only user-level code. SE mode requires a Python configuration script and a workload binary to run. The simplest system that can be simulated in SE mode is a CPU and a memory system connected with a memory bus, as shown in Figure 2.4. SE mode provides higher simulation speeds and is much simpler to configure since it doesn't simulate all the devices in a system and focuses on the CPU and memory system, however, it is not as accurate as FS mode.