### TECHNICAL UNIVERSITY OF CRETE

DIPLOMA THESIS

# Methodology and Experiments for Large Scale Distributed Computation on Reconfigurable Logic – Based Platform

Author: Christini Tzortzakı Thesis Committee: Prof. Apostolos Dollas Assoc. Prof. Vasilis Samoladas Asst. Prof. Vasileios PAPAEFSTATHIOU (UOC)

A thesis submitted in fulfillment of the requirements for the diploma of Electrical and Computer Engineer

$in \ the$

School of Electrical and Computer Engineering Microprocessor and Hardware Laboratory

February 8, 2024

#### TECHNICAL UNIVERSITY OF CRETE

### Abstract

#### School of Electrical and Computer Engineering

Electrical and Computer Engineer

### Methodology and Experiments for Large Scale Distributed Computation on Reconfigurable Logic – Based Platform

by Christini TZORTZAKI

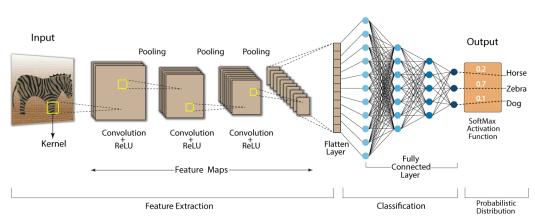

Hardware accelerators have become crucial due to their superior performance and energy efficiency. One noteworthy example is the application of hardware accelerators to Convolutional Neural Networks (CNNs), which are computationally intensive and highly parallelizable. Recent research has demonstrated significant performance improvements when implementing CNNs with hardware accelerators. This study builds upon the CNN hardware accelerator developed by G. Pitsis [1] and C. Loukas [2] for the Xilinx ZCU102 and the QFDB multi-FPGA prototype board, respectively, and aims at the migration of the accelerator to the Alveo U50 Data Center Card and investigates opportunities for further scaling.

Through a series of experiments, the performance of the migrated CNN architecture on the Alveo U50 is evaluated and compared with its implementations on the Xilinx ZCU102 and the QFDB. Not only were the tools changed to enable the architecture's execution on the Alveo platform, but modifications were also necessary for the architecture itself. As a result, using a similar FPGA, a 22% improvement in throughput was achieved. The migration to the Alveo U50 is shown to result in improved computational efficiency, showcasing the platform's enhanced capabilities for large-scale distributed computation. Furthermore, the utilization of multiple compute units is explored as a means of achieving parallelization, leading to enhanced throughput and overall better performance.

#### TECHNICAL UNIVERSITY OF CRETE

### Abstract

#### School of Electrical and Computer Engineering

Electrical and Computer Engineer

### Methodology and Experiments for Large Scale Distributed Computation on Reconfigurable Logic – Based Platform

by Christini TZORTZAKI

Οι επιταχυντές υλικού έχουν γίνει κρίσιμοι λόγω της υπερέχουσας επίδοσης και της ενεργειακής τους απόδοσης. Ένα αξιοσημείωτο παράδειγμα είναι η εφαρμογή επιταχυντών υλικού σε συνελικτικά νευρωνικά δίκτυα (CNN), τα οποία είναι υπολογιστικά εντατικά και εξαιρετικά παραλληλίσιμα. Πρόσφατες έρευνες έχουν δείξει σημαντικές βελτιώσεις στην απόδοση κατά την εφαρμογή συνελικτικού νευρωνικού δικτύου (CNN) με επιταχυντές υλικού. Αυτή η μελέτη βασίζεται στον επιταχυντή υλικού CNN που αναπτύχθηκε από τους Γ. Πίτση [1] και Χ. Λουκά [2] για την Xilinx ZCU102 και την πρωτότυπη πλακέτα πολλαπλών FPGA QFDB, αντίστοιχα. Αυτή η διατριβή στοχεύει στην μετεγκατάσταση του επιταχυντή στην Alveo U50 και διερευνά ευκαιρίες για περαιτέρω κλιμάκωση.

Μέσα από μια σειρά πειραμάτων, αξιολογείται η απόδοση της αρχιτεχτονιχής CNN στο Alveo U50 και συγκρίνεται με τις υλοποιήσεις της στο ZCU102 και το QFDB. Δεν χρειάστηκε μόνο να αλλάξουν τα εργαλεία για να καταστεί δυνατή η εκτέλεση της αρχιτεχτονικής στην πλατφόρμα Alveo, αλλά και τροποποιήσεις ήταν απαραίτητες για την ίδια την αρχιτεχτονική. Ως αποτέλεσμα, χρησιμοποιώντας FPGAs παρόμοιας τεχνολογίας, επιτεύχθηκε 22% βελτίωση στην απόδοση. Η μετάβαση στο Alveo U50 φαίνεται να έχει ως αποτέλεσμα βελτιωμένη υπολογιστική απόδοση, επιδειχνύοντας τις βελτιωμένες δυνατότητες της πλατφόρμας για κατανεμημένους υπολογισμούς μεγάλης κλίμακας. Επιπλέον, η χρήση πολλαπλών υπολογιστικών μονάδων διερευνάται ως μέσο για την επίτευξη παραλληλισμού, που οδηγεί σε βελτιωμένη απόδοση και συνολικά καλύτερη απόδοση.

### Acknowledgements

First of all, I would like to thank my supervisor, Prof. Apostolos Dollas, for his constant support and guidance both during my work on this thesis and throughout the course of my studies.

This thesis could of course not have been completed without the valuable help of the staff of the MHL laboratory in TUC. I would also like to thank Prof. Vasilis Samoladas and Prof. Vasileios Papaefstathiou for being members of my committee, and evaluating my work Most of all I would like to thank Dr. Pavlos Malakonakis for valuable advice and his insightful input on my work.

Last but not least I would like to express my deepest gratitude to the people who have always been there for me, my family and friends.

Christini Tzortzaki, Chania, 2024

## Contents

| Ał | ostrac  | ct       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | iii  |

|----|---------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Ac | cknow   | ledgem   | ents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | vii  |

| Co | onten   | ts       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ix   |

| Li | st of : | Figures  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | xiii |

| Li | st of ' | Tables   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | xv   |

| Li | st of . | Algoritl | nms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | xvii |

| Li | st of . | Abbrev   | iations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | xix  |

| 1  | Intr    | oductio  | n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1    |

|    | 1.1     | Thesis   | Outline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3    |

| 2  | Rela    | ated Wo  | rk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5    |

|    | 2.1     | Convo    | lutional Neural Networks (CNNs)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5    |

|    |         | 2.1.1    | Convolutional Layers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6    |

|    |         | 2.1.2    | Fully Connected Layers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6    |

|    | 2.2     | Accele   | rations on FPGAs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7    |

|    |         | 2.2.1    | CNNs on ZCU102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 7    |

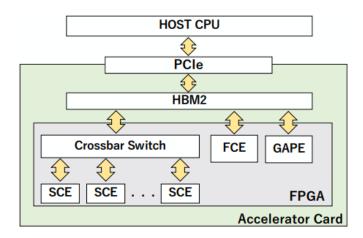

|    |         | 2.2.2    | CNNs on Alveo U50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 8    |

|    |         | 2.2.3    | Descroption of the CNN Model Used in the Present Thesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | s 9  |

| 3  | Ana     | lysis of | Design Vitis/Vivado Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 11   |

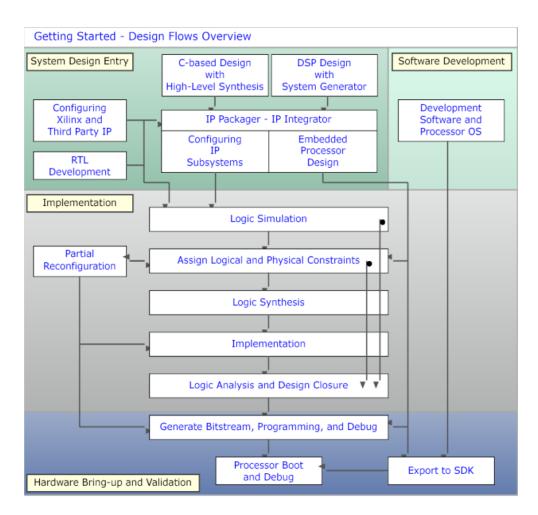

|    | 3.1     | Vivado   | )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 11   |

|    |         | 3.1.1    | Vivado Tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 11   |

|    |         |          | Vivado High Level Synthesis (HLS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 11   |

|    |         |          | Vivado IDE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 12   |

|    |         |          | Xilinx SDK and Xilinx Vitis IDE $\hfill \ldots \hfill \hfill \ldots \hfill \hfill \ldots \hfill \hfil$ | 13   |

|    |         | 3.1.2    | Vivado Design Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 14   |

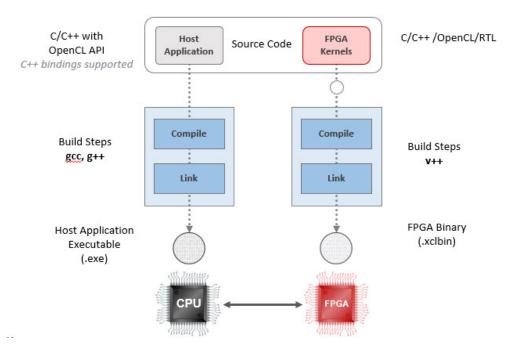

|   | 3.2 | Vitis                                                   | 15 |

|---|-----|---------------------------------------------------------|----|

|   |     | 3.2.1 Vitis Tools                                       | 15 |

|   |     | Vitis Unified Software Platform                         | 15 |

|   |     | 3.2.2 Vitis Design Flow                                 | 16 |

|   | 3.3 | Discussion                                              | 18 |

| 4 | Met | bodology to Transform Vivado Designs to Vitis Designs   | 21 |

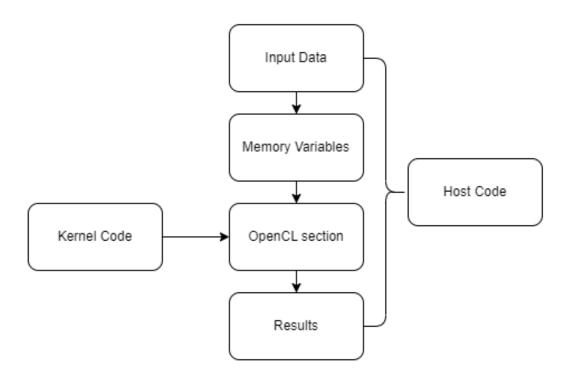

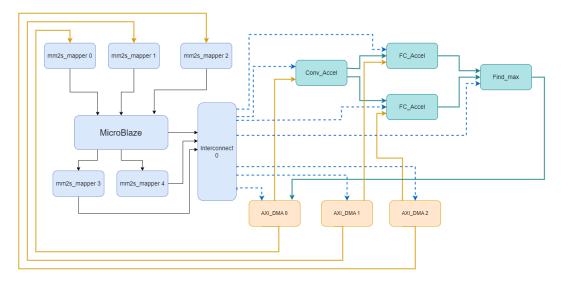

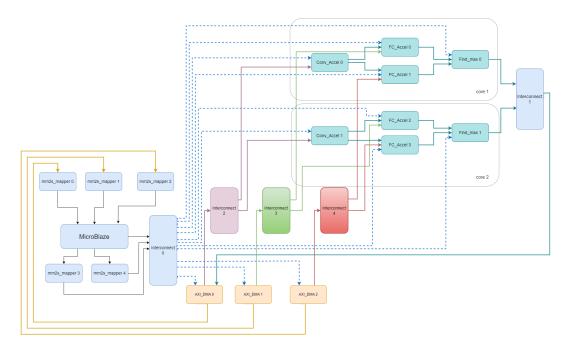

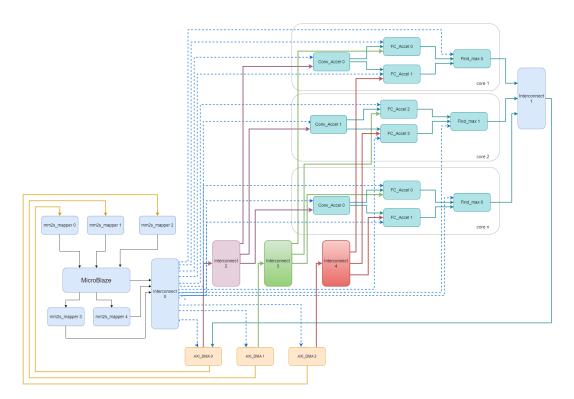

|   | 4.1 | Structure of Design                                     | 22 |

|   | 4.2 | Host Code                                               | 23 |

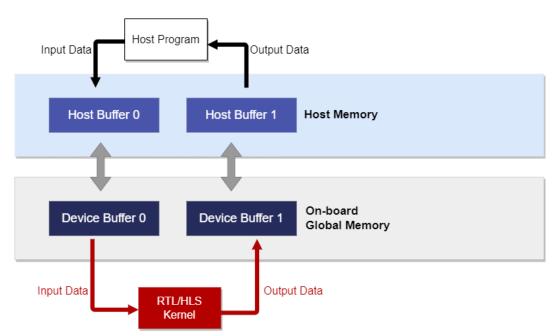

|   |     | 4.2.1 CL buffers                                        | 23 |

|   | 4.3 | Kernel Code                                             | 27 |

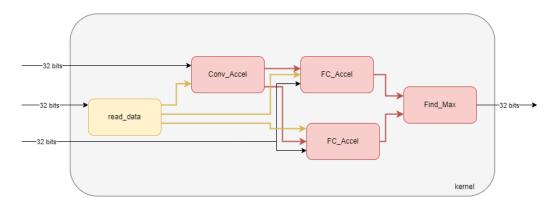

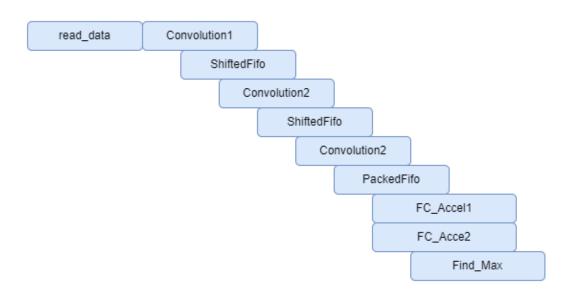

|   |     | 4.3.1 Streaming data                                    | 28 |

|   |     | 4.3.2 Changes in Kernel                                 | 30 |

|   | 4.4 | Optimization                                            | 32 |

|   |     | 4.4.1 Wide Memory Access                                | 33 |

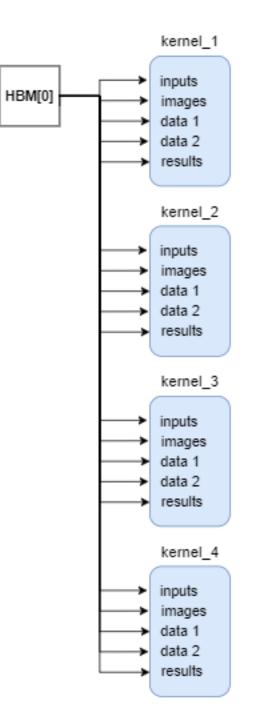

|   |     | 4.4.2 Multiple Compute Units                            | 34 |

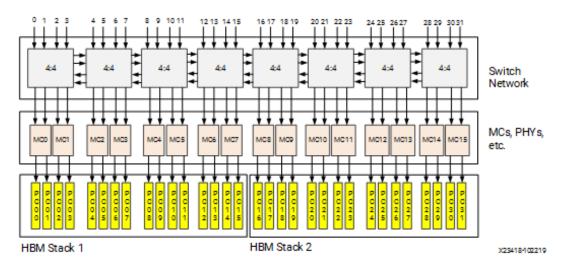

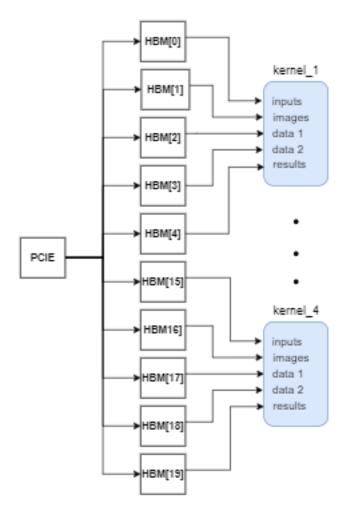

|   |     | High Bandwidth Memory                                   | 39 |

|   |     | 4.4.3 Mapping Kernel Ports to Memory                    | 39 |

|   | 4.5 | Review of The Process                                   | 40 |

| 5 | FPO | GA Implementation                                       | 43 |

|   | 5.1 | FPGA Platforms                                          | 43 |

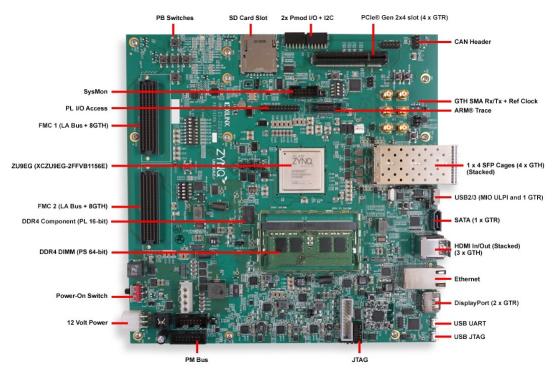

|   |     | 5.1.1 Xilinx Zynq UltraScale+ MPSoC ZCU102              | 43 |

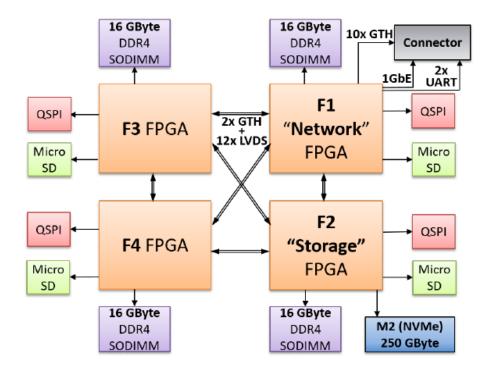

|   |     | 5.1.2 Quad FPGA Daughter Board                          | 44 |

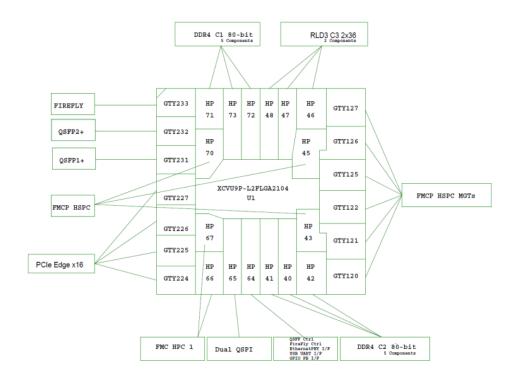

|   |     | 5.1.3 AMD Virtex UltraScale+ FPGA VCU118 Evaluation Kit | 46 |

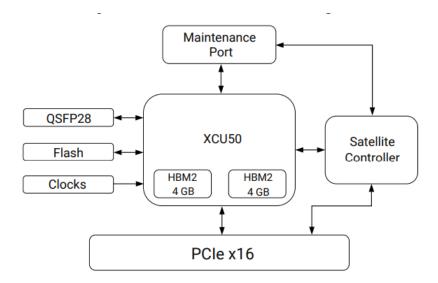

|   |     | 5.1.4 Alveo U50 Data Center Accelerator Card            | 50 |

|   | 5.2 | Discussion                                              | 52 |

| 6 | Res | ults                                                    | 55 |

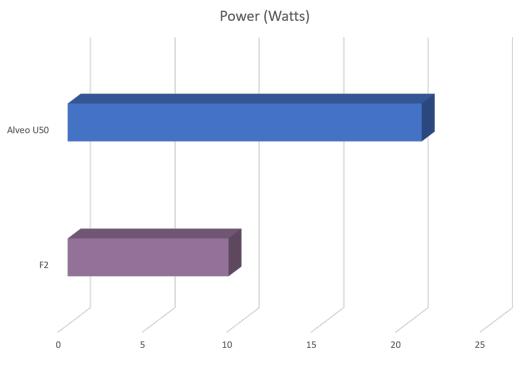

|   | 6.1 | Resource Utilization                                    | 55 |

|   | 6.2 | Power Consumption and Energy Consumption                | 56 |

|   |     | Power Consumption                                       | 56 |

|   |     | Energy Consumption                                      | 56 |

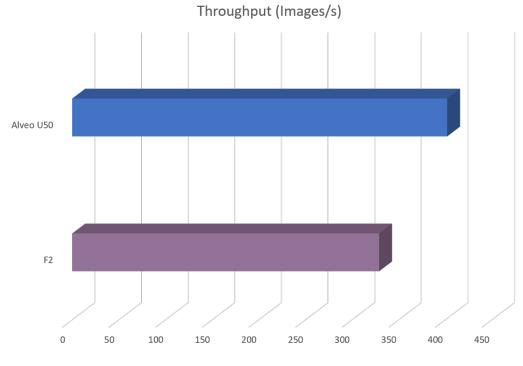

|   | 6.3 | Throughput and Latency Speedup                          | 57 |

|   |     | Latency                                                 | 57 |

|   |     | $Throughput \ . \ . \ . \ . \ . \ . \ . \ . \ . \ $     | 57 |

|   | 6.4 | Overall Performance Comparison                          | 57 |

| 7 | Con | clusions and Future Work                                | 61 |

х

### References

xi

# **List of Figures**

| A CNN architecture. Source: [6]                                  | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Architecture Design. Source: [15]                                | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Vivado Design Suite design flow. Source: [21]                    | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Vitis design flow. Source: $[23]$                                | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

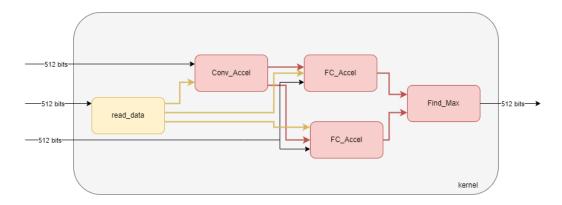

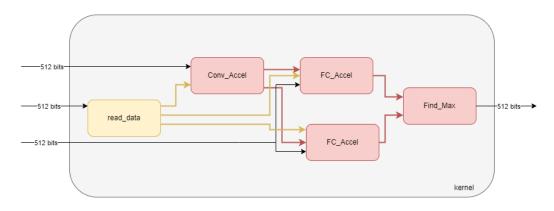

| Architecture Design                                              | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Data movement through CL buffers                                 | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

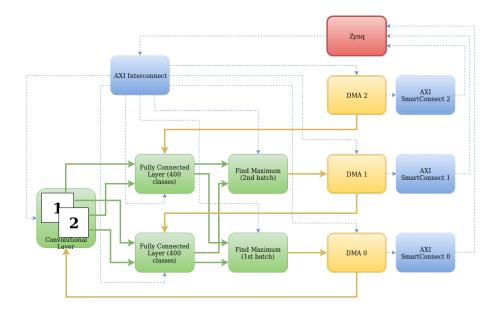

| Block Diagram of kernel - input 32bits                           | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Block Diagram of kernel without dataflow                         | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Block Diagram of kernel with dataflow                            | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |