## TECHNICAL UNIVERSITY OF CRETE

Architectural Trade-offs of Partial Reconfiguration in FPGA Systems

A DISSERTATION

SUBMMITTED TO THE GRADUATE PROGRAM IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

> FOR THE DEGREE DOCTOR OF PHILOSOPHY IN

ELECTRONIC AND COMPUTER ENGINEERING

BY

Kyprianos D. Papadimitriou

CHANIA, CRETE

October 2011

© Copyright by Kyprianos D. Papadimitriou. All Rights Reserved

#### Abstract

Reconfigurable computing (RC) is increasingly gaining the attention of many researchers and users by the academia and industry alike. The most popular representatives of reconfigurable computing are Field Programmable Gate Arrays (FPGAs). FPGAs are integrated circuits consisting of a large array of uncommitted programmable logic and interconnect, plus large blocks such as memories and Digital Dignal Processing (DSP) units that can be configured to implement digital circuits. Their capability to be programmed and reprogrammed in the field, i.e. forming on demand the digital circuit that will execute the application at hand, offers an unprecedented advantage over other technologies such as the Application Specific Integrated Circuits (ASICs) that cannot be reprogrammed, and the traditional software microprocessors in which flexibility comes at the expense of limited performance due to the fixed instruction set and the lack of parallelism. Moreover, GPUs that have started to be used for accelerating computationally intensive applications, although stand as strong opponents to the FPGAs, they have fixed hardware resources that cannot be customized to the application at hand.

An important portion of the FPGA market concerns static RAM (SRAM) based FPGAs, meaning that the SRAM bits are connected to the configuration points in the chip, and programming the SRAM bits configures the chip. A promising feature of specific families of SRAM-based FPGAs is the ability to reuse the same hardware for different tasks at different phases of an application execution. Moreover, the tasks can be swapped on the fly while part of the hardware continues to operate. This feature is known as run-time or dynamic reconfiguration.

Building upon the idea of dynamically reconfiguring a circuit in SRAM-based FPGAs, this dissertation explores the architectural tradeoffs of implementing applications in partially reconfigurable (PR) FPGA-based systems and proposes new avenues for its use. The dissertation begins with an in-depth study of the literature on reconfigurable devices and concentrates on those that can be configured in part. Next, it proposes a novel way to schedule tasks in PR FPGAs which is evaluated within the context of a simulation framework. Then, a real-world experimental framework allowing to study the functional details of reconfiguration is presented. Using this framework a theoretical model is shaped which can be used for the early assessment of the overhead that the reconfiguration process incurs to the application execution. Finally, the dissertation proposes a novel way to exploit the PR technology in a specific application domain. In particular, a new method based on the PR capability of specific FPGAs is described, which allows for the self-repairing of FPGA core while operating in a harsh environment. All aspects of the present research have been verified with experiments from different setups using partially reconfigurable FPGA platforms.

#### Acknowledgements

I would like to thank my Professor Apostolos Dollas for his advice, encouragement and support on this dissertation effort. It was his vision that introduced me in the fascinating area of reconfigurable computing which has started earning its own place as an individual research field. I was fortunate enough to have him as a supervisor to stimulate and struggle me in order to devote a large amount of time seeking the research topic and shaping the subject of this Ph.D on my own. We spent a lot of time discussing and arguing on this subject and it was his directions that eventually led me to complete this dissertation. Also, he was the one who insisted and exhorted me to make the last steps toward completing my work and eventually close this Chapter of my life. I thank him for this deeply.

I would like to thank my Professor Konstantinos Kalaitzakis for his support and advices during my Ph.D candidacy, and my Professor Dionisios Pnevmatikatos for the discussions we had prior delving into this work and for his important hints throughout my research. I deeply thank Professor Scott Hauck for accepting me in his group at the University of Washington and for the long and fruitful discussions we had. Although my visit at the University of Washington was short his advices had a great impact on me. I hope that we will meet and cooperate again in the future.

I want to thank Professors Manolis Katevenis, Georgios Stamoulis, Georgios Stavrakakis, and Ioannis Papaefstathiou for participating in my committee and revising the manuscript.

I deeply thank Robert Pozner for all his advices and the way he has influenced me until now. I thank Anne McKay, Stella Psaroudaki and Magda Markantonaki for all their help. I want to thank the people I have worked with at the Microprocessor and Hardware Laboratory (MHL). It is a pleasure to be in the same environment with Markos - who assisted me in everything I 've needed -, Euripides and Grigoris and interact with all the members of MHL.

I want to thank Stefanos Karasavvidis for his help, and Christoforos Kachris for his detailed comments prior submitting a paper related with my Ph.D work. I would like to thank Amir for the great cooperation we had. Our joint work is not included in the present dissertation but its has been published in the proceedings of a conference. Also, I would like to thank all the members of the group I worked with during my visit at the University of Washington: Aaron, Robin, Shakil, Jimmy, Michael, Brian, Benjamin, Steve and Ken were all great.

It would have been a miss not to mention Antonis Anyfantis and Argyris Ilias who during their undergraduate studies helped me reinforce the contributions of this research. Antonis made the automatic framework described in Chapter 4 that enabled the measurements during reconfiguration. The results formed the basis for extracting the model of Chapter 5. Argyris during his final-year project implemented a fully functional prototype of the design described in Chapter 6. I instructed and cooperated tightly with both Antonis and Argyris and although they didn't involve with the design, their contribution in building the fully functional systems is acknowledged. Also it should be noted that the results gathered with the experimental setups of the final-year projects of Michalis Vavouras and Giorgos Nikoloudakis were used to verify part of the work described in Chapters 3 and 5 respectively.

I would like to thank all the friends and the people that stood by my side and especially I thank Efi and Fotis.

Also, I would like to acknowledge the support of Xilinx Incorporation on the development platforms and tools. I acknowledge the Greek Ministry of National Education and Religious Affairs for the Ph.D fellowship under the program Heraklitus of EPEAEK II. However, I want to report the delay of the funding, which arrived 20 months after the acceptance of the research proposal. I wish it would have arrived earlier. Also, I want to point out that the subject of the proposal wasn't strictly related with the subject of my Ph.D, but it gave me the motivation to delve into the details of reconfigurable computing.

I thank my parents Dimitris and Ioanna for standing by my side throughout all these years. Without their patience and support I wouldn't be able to complete this task. I thank them with all my heart and I dedicate the dissertation to my father who left us so soon.

To my father

# Contents

|               | Abst            | tract .  |                                                   | iii      |

|---------------|-----------------|----------|---------------------------------------------------|----------|

|               | Ackı            | nowledg  | gements                                           | v        |

| $\mathbf{Li}$ | st of           | Table    | s                                                 | 1        |

| $\mathbf{Li}$ | st of           | Figur    | es                                                | 4        |

| 1             | $\mathbf{Intr}$ | oducti   | ion                                               | <b>2</b> |

|               | 1.1             | Motiva   | ation                                             | 3        |

|               | 1.2             | Contri   | ibution                                           | 4        |

|               | 1.3             | Struct   | sure                                              | 5        |

| <b>2</b>      | Stat            | te of tl | he Art                                            | 7        |

|               | 2.1             | Introd   | luction                                           | 7        |

|               | 2.2             | Histor   | rical Evolution                                   | 12       |

|               |                 | 2.2.1    | Single Context                                    | 13       |

|               |                 | 2.2.2    | Multi Context                                     | 15       |

|               |                 | 2.2.3    | Partially Reconfigurable                          | 16       |

|               |                 | 2.2.4    | Discussion Summary                                | 17       |

|               | 2.3             | Resear   | rch Topics on Dynamic Reconfiguration             | 19       |

|               | 2.4             | Theor    | etical Study of Dynamic Reconfiguration           | 22       |

|               |                 | 2.4.1    | RTR approaches                                    | 22       |

|               |                 | 2.4.2    | Studying RTR Performance with Mathematical Models | 24       |

|               |                 | 2.4.3    | Other Approaches                                  | 28       |

|   |      | 2.4.4  | Discussion Summary                         | 29 |

|---|------|--------|--------------------------------------------|----|

|   | 2.5  | Archit | ectures                                    | 30 |

|   |      | 2.5.1  | Reconfigurable coprocessor                 | 32 |

|   |      | 2.5.2  | Reconfigurable Functional Unit             | 35 |

|   |      | 2.5.3  | FPU embedded in reconfigurable fabric      | 40 |

|   |      | 2.5.4  | Other Architectures                        | 42 |

|   |      | 2.5.5  | Discussion Summary                         | 46 |

| 3 | Tasl | k Sche | duling and Allocation                      | 53 |

|   | 3.1  | Proble | m Description                              | 53 |

|   |      | 3.1.1  | Related Work                               | 54 |

|   | 3.2  | Contri | bution                                     | 55 |

|   | 3.3  | Model  | ing with Task Graphs                       | 56 |

|   |      | 3.3.1  | An Illustrative Example                    | 57 |

|   |      | 3.3.2  | Task Graphs For Free                       | 58 |

|   | 3.4  | Enhan  | cing a Prefetching Algorithm               | 58 |

|   | 3.5  | System | n Model                                    | 61 |

|   |      | 3.5.1  | Configuration in Modern FPGAs              | 61 |

|   |      | 3.5.2  | Simulation Framework                       | 62 |

|   | 3.6  | A Res  | ource-driven Approach                      | 63 |

|   | 3.7  | Using  | the Simulation Framework                   | 66 |

|   |      | 3.7.1  | An Experimental Setup                      | 67 |

|   |      | 3.7.2  | Results and Evaluation                     | 69 |

|   | 3.8  | Discus | sion Summary                               | 73 |

| 4 | Exp  | erime  | ntal Framework                             | 77 |

|   | 4.1  | Backg  | round                                      | 79 |

|   |      | 4.1.1  | The Virtex-II Pro FPGA and Reconfiguration | 79 |

|   |      | 4.1.2  | Evaluation of Reconfiguration              | 80 |

|   | 4.2  | Experi | imental Setup                              | 81 |

|   |      | 4.2.1  | XUPV2P Platform                            | 82 |

|   |     | 4.2.2   | FPGA System                                   | 82  |

|---|-----|---------|-----------------------------------------------|-----|

|   |     | 4.2.3   | Creating the Partial Bitstreams               | 84  |

|   |     | 4.2.4   | Demonstration of Dynamic Reconfiguration      | 85  |

|   |     | 4.2.5   | System Parameters                             | 85  |

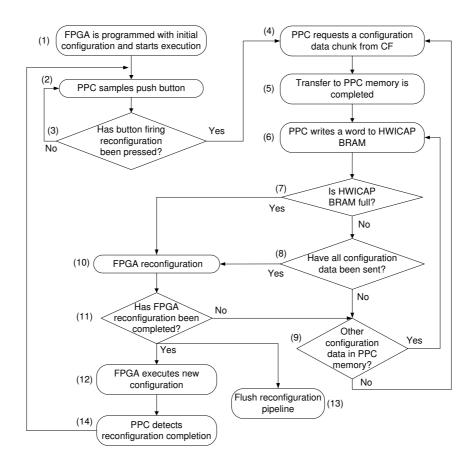

|   |     | 4.2.6   | System Operation Flow                         | 86  |

|   | 4.3 | Recon   | figuration Time Breakdown and Measurement     | 86  |

|   | 4.4 | Exper   | imentation Phase                              | 89  |

|   |     | 4.4.1   | Parameters and Stages                         | 90  |

|   |     | 4.4.2   | The Manual Method                             | 90  |

|   |     | 4.4.3   | The Framework                                 | 92  |

|   | 4.5 | Result  | ts                                            | 95  |

|   | 4.6 | Conclu  | usion                                         | 96  |

| 5 | Per | formaı  | nce of Reconfiguration                        | 98  |

|   | 5.1 | Overv   | iew of Reconfiguration Performance Issues     | 99  |

|   | 5.2 | State   | of the Art                                    | 101 |

|   |     | 5.2.1   | Background on Partial Reconfiguration         | 101 |

|   |     | 5.2.2   | Reconfiguration Time and Throughput           | 103 |

|   | 5.3 | Invest  | igation of Reconfiguration Performance        | 107 |

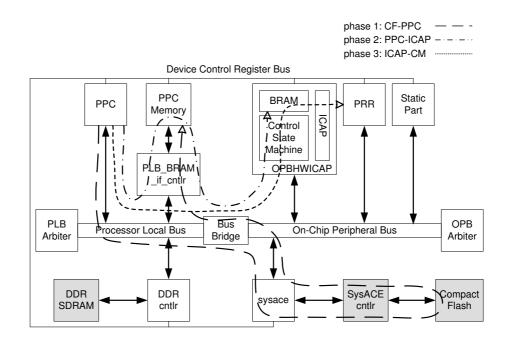

|   | 5.4 | System  | n Architecture                                | 112 |

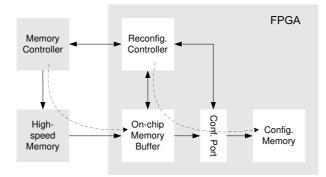

|   |     | 5.4.1   | General Architectural Model                   | 112 |

|   |     | 5.4.2   | The Reference System                          | 113 |

|   |     | 5.4.3   | Options Affecting Reconfiguration Performance | 117 |

|   | 5.5 | Develo  | opment of a Cost Model                        | 118 |

|   |     | 5.5.1   | The Cost Model                                | 118 |

|   |     | 5.5.2   | Model Extension                               | 122 |

|   |     | 5.5.3   | Discussion                                    | 124 |

|   | 5.6 | Verific | cation and Usage                              | 125 |

|   |     | 5.6.1   | Verification                                  | 125 |

|   |     | 5.6.2   | Reaping the Benefits of the Cost Model        | 126 |

|    |        | 5.6.3 Strengths, Weaknesses and Potential Extensions | 130 |

|----|--------|------------------------------------------------------|-----|

|    | 5.7    | Discussion Summary                                   | 132 |

| 6  | HM     | IR: A Novel Case Study                               | 133 |

|    | 6.1    | Introduction                                         | 134 |

|    | 6.2    | Related Work and Motivation                          | 136 |

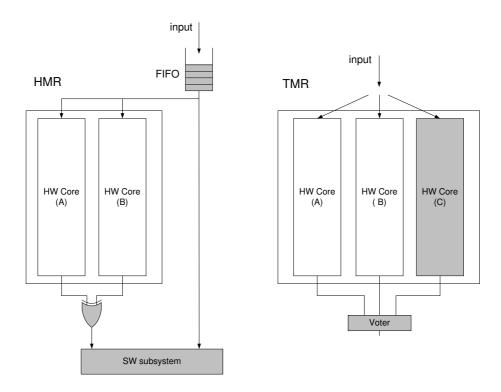

|    | 6.3    | A Generic HMR Architecture                           | 138 |

|    |        | 6.3.1 Architecture                                   | 139 |

|    |        | 6.3.2 1-PRR design vs. 2-PRRs design                 | 140 |

|    |        | 6.3.3 Benefits and Weaknesses                        | 141 |

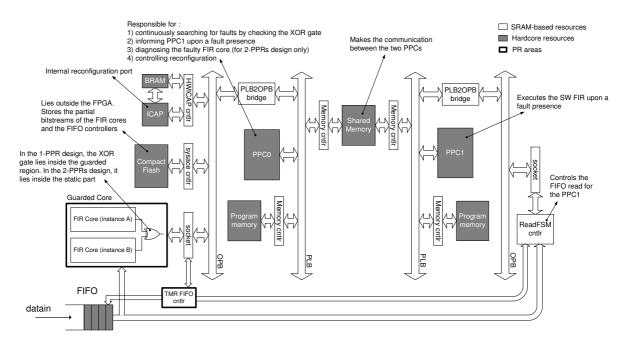

|    | 6.4    | Implementation of HMR in a Virtex-II Pro             | 142 |

|    |        | 6.4.1 Resource Utilization                           | 144 |

|    |        | 6.4.2 Benefits, Drawbacks and Extensions             | 145 |

|    | 6.5    | Experimental Results                                 | 147 |

|    | 6.6    | HMR vs. TMR                                          | 148 |

|    | 6.7    | Conclusions                                          | 151 |

| 7  | Cor    | nclusions and Future Work                            | 152 |

|    | 7.1    | Contributions                                        | 152 |

|    | 7.2    | Directions for Future Research                       | 154 |

| Bi | ibliog | graphy                                               | 157 |

# List of Tables

| 2.1 | Reconfigurable devices classified in single-context (SC), multi-context (MC)  |     |

|-----|-------------------------------------------------------------------------------|-----|

|     | and partially reconfigurable (PR) structures.                                 | 14  |

| 2.2 | Design issues, logic and software requirements for the three RTR approaches   |     |

|     | of the example system                                                         | 24  |

| 2.3 | Classification of reconfigurable processors.                                  | 47  |

| 3.1 | Characteristics of the XC2V500 FPGA.                                          | 68  |

| 3.2 | Input to the TGFF.                                                            | 69  |

| 3.3 | Performance in original vs. augmented model. Worst cases regarding CLAM       |     |

|     | time are shown. Times are measured in $\mu s$                                 | 71  |

| 4.1 | Time duration per user, system, or combined user/system action, for one       |     |

|     | experiment with the manual method                                             | 91  |

| 4.2 | Time duration per user, system, or combined user/system action for one run    |     |

|     | using the framework. 88 different experiments, with each one corresponding    |     |

|     | to a different parameter combination, are executed with a single run          | 95  |

| 4.3 | Size of the experimental partial bitstreams and reconfiguration times for the |     |

|     | parameters of Figure 4.7.                                                     | 97  |

| 5.1 | Reconfiguration-related characteristics and measured reconfiguration time     |     |

|     | and throughput. The Bitstream Size (BS) is in KBytes, the Reconfigura-        |     |

|     | tion Time (RT) in milliseconds, and the Actual Reconfiguration Throughput     |     |

|     | (ARTP) in MBytes/sec.                                                         | 105 |

| 5.2  | Comparison between the bandwidth of the configuration port and the actual         |     |

|------|-----------------------------------------------------------------------------------|-----|

|      | reconfiguration throughput for different published system setups                  | 108 |

| 5.3  | Size of BRAM resources for moderate-sized FPGAs of Virtex-II,-4,and -5            |     |

|      | families. The Table illustrates the maximum size of the bitstreams that can       |     |

|      | be prefetched in the extreme case none of the actual circuits utilizes BRAMs.     | 112 |

| 5.4  | System settings.                                                                  | 115 |

| 5.5  | Execution time-per-processor-call for different sizes of the processor array.     |     |

|      | The amount of data transferred per call is dictated by the smallest amongst       |     |

|      | the processor array and the ICAP cache. In the ICAP-CM phase, the pro-            |     |

|      | cessor call needs 2048 Bytes to perform a transaction                             | 117 |

| 5.6  | Average time-per-processor-call. For the analysis to be realistic it is adhered   |     |

|      | to the way the phases are carried out by the corresponding processor calls;       |     |

|      | the minimum amount of data for the SM-PPC and PPC-ICAP phases to be               |     |

|      | carried out is 512 Bytes, while ICAP-CM phase needs exactly 2048 Bytes            | 117 |

| 5.7  | Percentage of the time spent in each phase of reconfiguration and the cor-        |     |

|      | responding measured throughput and theoretical bandwidth. The values              |     |

|      | concern the reference system.                                                     | 121 |

| 5.8  | Comparison between the calculated and measured reconfiguration times for          |     |

|      | a partially reconfigurable cryptography system                                    | 126 |

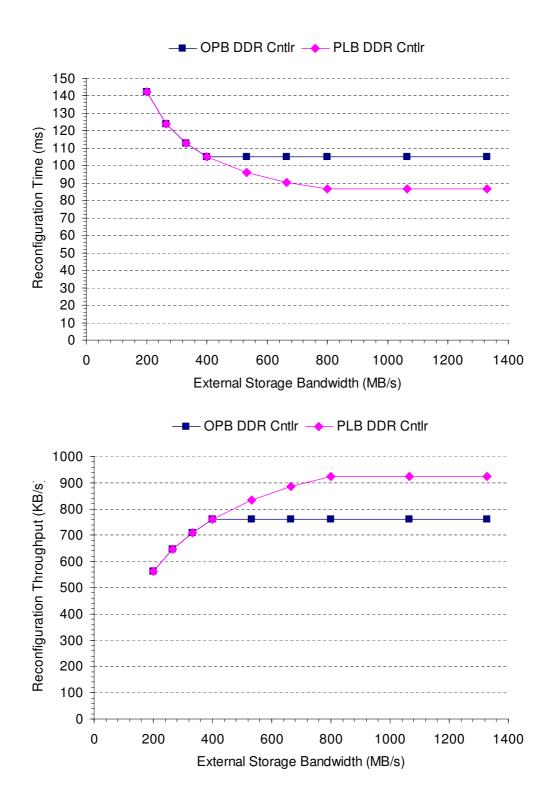

| 5.9  | Reconfiguration time (RT) and throughput (ARTP) for setups with various           |     |

|      | DDR memories. The values are calculated with the cost model for a partial         |     |

|      | bitstream of 80 KBytes. They concern a system, where the DDR controller           |     |

|      | is implemented as an IP core attached on the OPB (400 $\mathrm{MB/s})$ or the PLB |     |

|      | (800 MB/s) bus                                                                    | 129 |

| 5.10 | Comparison between the calculated and published reconfiguration times for         |     |

|      | different setups of partially reconfigurable systems using the processor to       |     |

|      | control reconfiguration (Calculated RT was extracted using the cost model,        |     |

|      | while Published RT is reported in the corresponding reference paper)              | 129 |

| 6.1  | Resource requirements for HMR and TMR                                             | 146 |

| 6.2 | Resource utilization for the static and the partially reconfigurable parts of |     |

|-----|-------------------------------------------------------------------------------|-----|

|     | the 2-PRRs design of HMR implemented in a Virtex-II Pro                       | 147 |

| 6.3 | BRAM utilization for implementing the program memories and the shared         |     |

|     | memory of the PPC's subsystem. 136 BRAMs are available in the Virtex-II       |     |

|     | Pro FPGA, each of which equals $2.25$ KBytes resulting in an overall of $306$ |     |

|     | KBytes available in the device.                                               | 147 |

| 6.4 | Operations affecting the restoration time in the HMR when implemented         |     |

|     | with the two different designs. The time duration of an operation is shown    |     |

|     | and summed only if it is part of the restoration procedure                    | 148 |

| 6.5 | Components in HMR and TMR schemes that scale according to the applica-        |     |

|     | tion size                                                                     | 150 |

# List of Figures

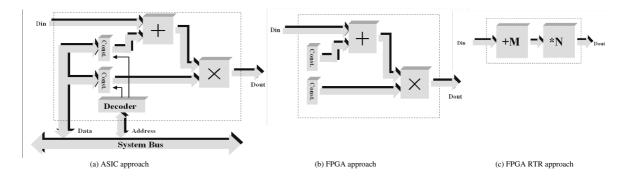

| 2.1 | Three different RTR approaches to design an equivalent system [Guccione           |    |

|-----|-----------------------------------------------------------------------------------|----|

|     | and Levi 1999]                                                                    | 22 |

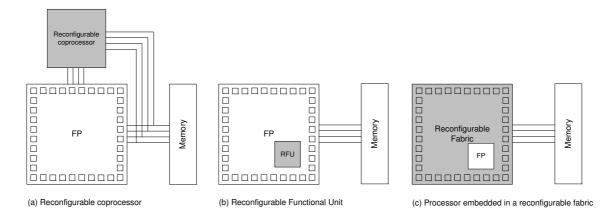

| 2.2 | Levels of coupling between microprocessor and reconfigurable hardware             | 29 |

| 2.3 | Block diagram of reconfigurable coprocessor architectures                         | 32 |

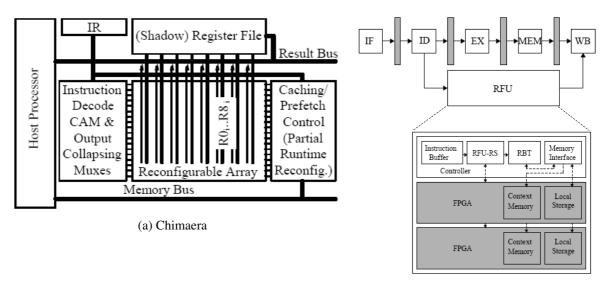

| 2.4 | Block diagram of reconfigurable functional unit architectures                     | 36 |

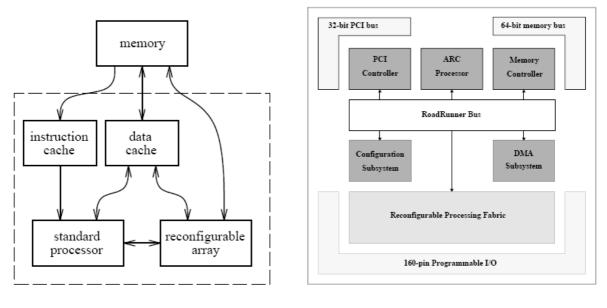

| 2.5 | Block diagram of architectures with FPU embedded in reconfigurable fabric.        | 40 |

| 2.6 | Block diagram of innovative architectures                                         | 43 |

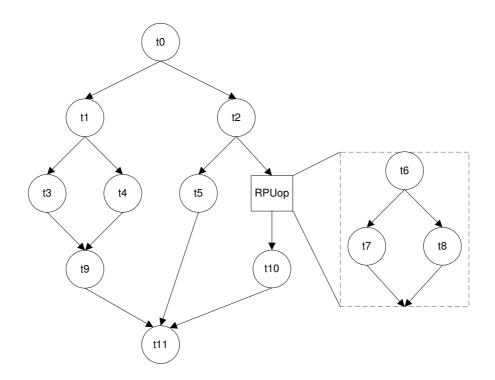

| 3.1 | Task graph of an example application. The nodes outside the box are tasks         |    |

|     | executed by the FPU. The square task corresponds to an RPU<br>op call com-        |    |

|     | prising of a set of tasks.                                                        | 57 |

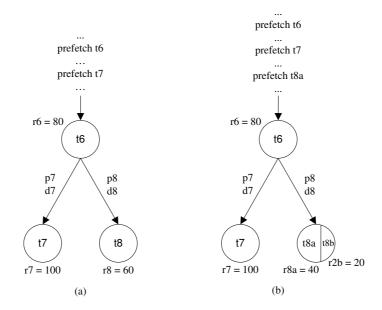

| 3.2 | Original static prefetching model and augmented model that proposes trans-        |    |

|     | formation of the graph and insertion of additional prefetch instructions          | 59 |

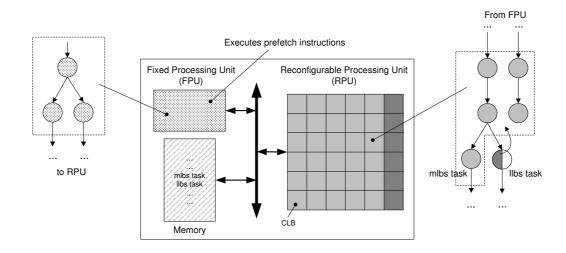

| 3.3 | Some tasks are executed by the FPU and other tasks are loaded to the RPU          |    |

|     | for acceleration. FPU triggers reconfiguration of the RPU without entering        |    |

|     | a stall phase. Prefetch instructions are initiated by the FPU. The partial        |    |

|     | bits<br>treams that implement the RPU tasks are stored in a memory.<br>$\ldots$ . | 61 |

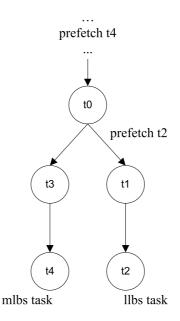

| 3.4 | Insertion of prefetch instruction of mlbs and llbs tasks according to the orig-   |    |

|     | inal model.                                                                       | 64 |

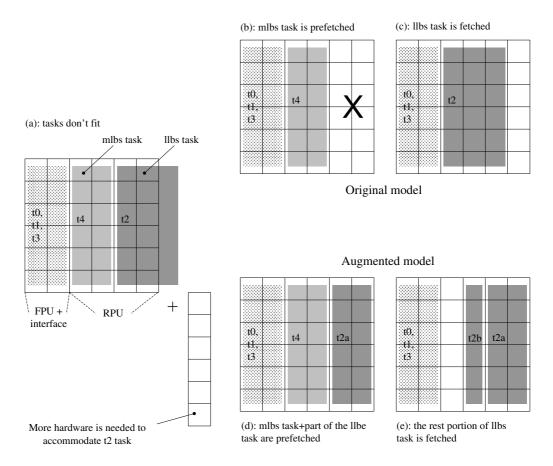

| 3.5 | Task placement in original vs. augmented model. In (a) tasks do not fit           |    |

|     | into the RPU. (b) and (c) correspond to the original model. (d) and (e)           |    |

|     | correspond to the augmented model                                                 | 65 |

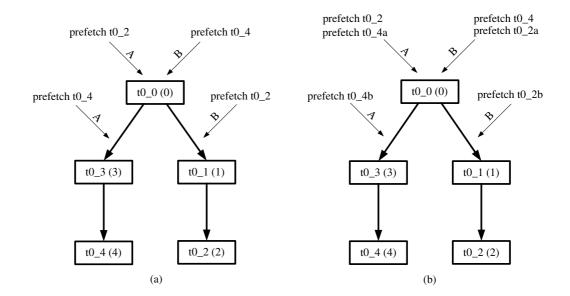

| 3.6 | TGFF output and insertion of prefetch instructions. (a) and (b) have the         |     |

|-----|----------------------------------------------------------------------------------|-----|

|     | prefetches according to the original and the augmented algorithm respec-         |     |

|     | tively. Two different scenarios regarding the insertion of prefetch instructions |     |

|     | are indicated with the labels A and B at the thin arrows, that are dictated      |     |

|     | by the mlbs/llbs assignment.                                                     | 67  |

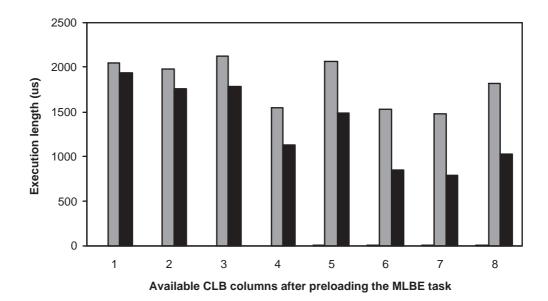

| 3.7 | Execution lengths for the original and the augmented model for different         |     |

|     | values of leftover CLB columns after prefetching the mlbs RPU task. The          |     |

|     | llbs RPU task is chosen for execution. Average values are shown that were        |     |

|     | obtained from 500 experiments with the simulation framework                      | 70  |

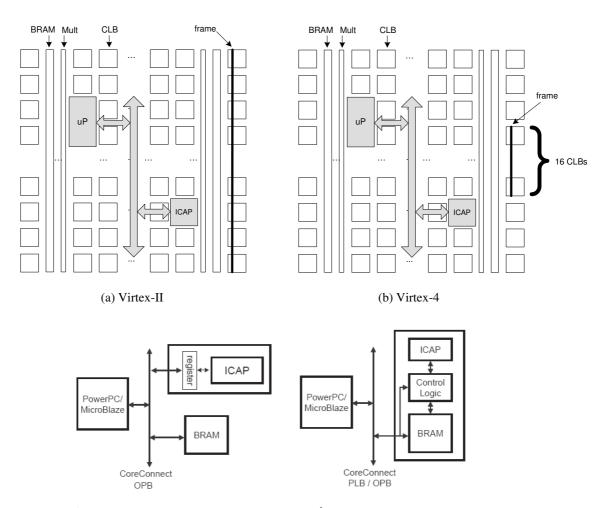

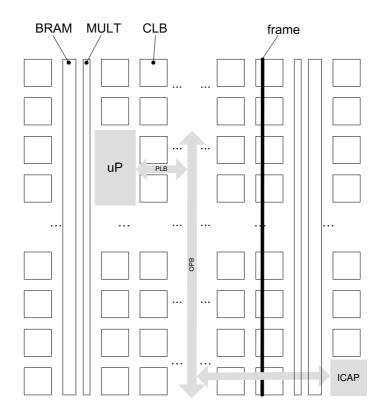

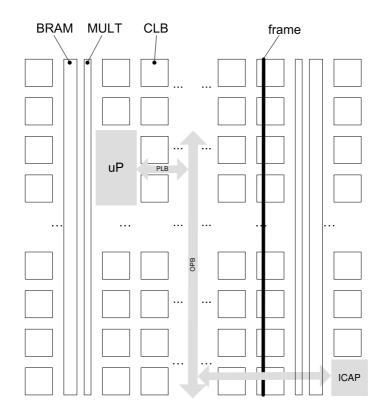

| 4.1 | The Virtex II-Pro FPGA resources and configuration frames                        | 78  |

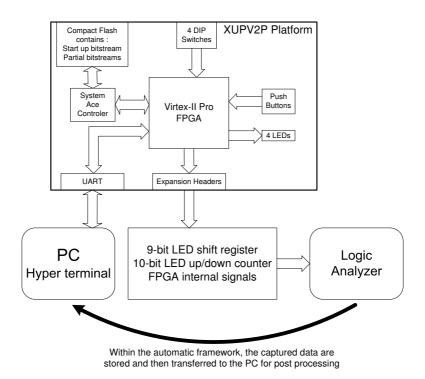

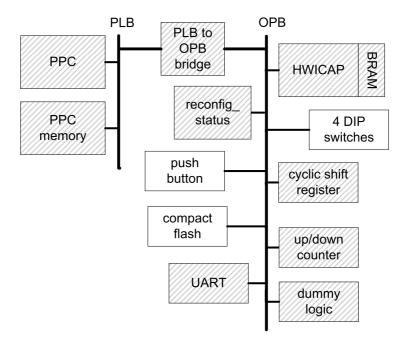

| 4.2 | Block diagram of the experimental setup.                                         | 82  |

| 4.3 | The shadowed boxes represent the internal components of the FPGA. The            |     |

|     | white boxes are parts of the platform connected externally with the FPGA.        | 83  |

| 4.4 | System operation flow.                                                           | 87  |

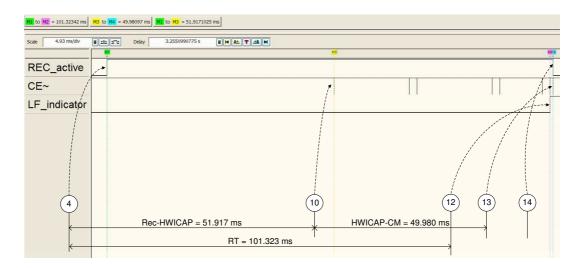

| 4.5 | Timing mode trace of the logic analyzer for one reconfiguration of bitstream     |     |

|     | 11 of Table 4.3. The parameters used are $bc=4,096$ Bytes and $pa=4,096$ Bytes.  | 88  |

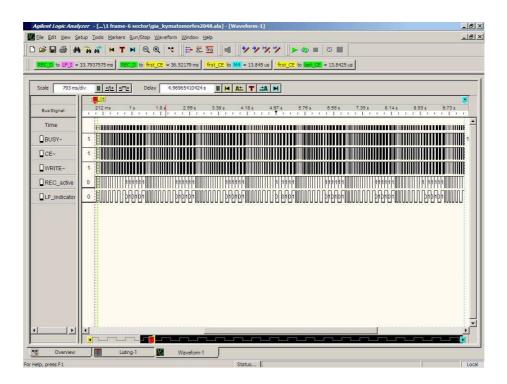

| 4.6 | Logic analyzer trace for successive reconfigurations of bitstreams 1-11 of Ta-   |     |

|     | ble 4.3 and pa sizes ranging from 512 to 4,096 Bytes                             | 93  |

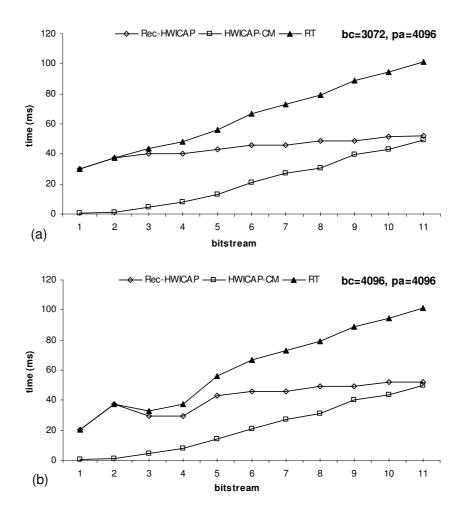

| 4.7 | Reconfiguration time and piecewise delays for different bitstreams and bc,       |     |

|     | and fixed pa.                                                                    | 96  |

| 5.1 | The Virtex II-Pro FPGA resources and configuration frames                        | 102 |

| 5.2 | General architectural model and flow of partial reconfiguration 1                | 13  |

| 5.3 | Flow of partial reconfiguration in the reference system with a Virtex-II Pro. 1  | 15  |

| 5.4 | Reconfiguration time for a partial bitstream of 80 KBytes and the corre-         |     |

|     | sponding throughput for different DDR memory bandwidths. The data are            |     |

|     | taken from Table 5.9                                                             | 128 |

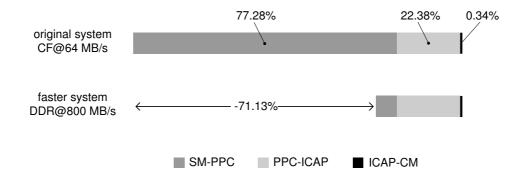

| 5.5 | The reconfiguration operation has three independent phases. In the original    |     |  |

|-----|--------------------------------------------------------------------------------|-----|--|

|     | system, the SM-PPC phase (dark-gray part) takes $77.28\%$ of the total recon-  |     |  |

|     | figuration operation (see Table 5.7). Making this part $12.5$ times faster and |     |  |

|     | leaving intact the rest of the operation (light-gray and black parts) in the   |     |  |

|     | faster system reduces the total reconfiguration time by 71.13%                 | 130 |  |

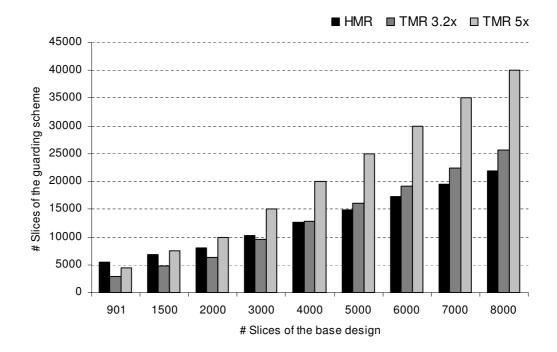

| 6.1 | HMR vs. TMR resource overhead.                                                 | 140 |  |

| 6.2 | Block diagram of the HMR implemented in a Virtex-II Pro FPGA                   | 143 |  |

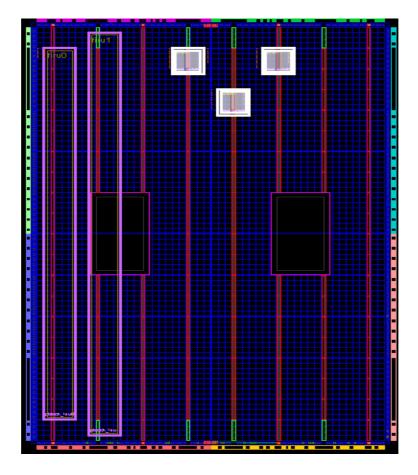

| 6.3 | Floorplanning of the partially reconfigurable regions in the HMR when im-      |     |  |

|     | plemented with the 2-PRRs design. The two FIR cores stand on the left and      |     |  |

|     | the TMR FIFO controller on the top of the device.                              | 145 |  |

| 6.4 | Slice utilization of HMR vs. TMR for various base designs in the Virtex-II     |     |  |

|     | Pro                                                                            | 149 |  |

## Chapter 1

## Introduction

Field Programmable Gate Arrays (FPGAs) are suitable for implementing applications that benefit from custom parallelization and pipelining. They combine a large pool of heterogeneous physical resources that when effectively treated can form circuits operating with high performance. Different application domains have benefited from their implementation in FPGAs ranging from bioinformatics on high-end systems [Afratis et al., 2008] to motion detection on low-cost systems [Papademetriou et al., 2006]. Nowadays, the leading companies manufacture FPGA chips in a technology process as low as 28nm. This broadens the capabilities offered by FPGAs as latest technology is capable to incorporate a vast amount of programmable resources made by billions of transistors within a single small die. The resources that co-exist into an FPGA chip range from single gates and flip-flops to hardcore Digital Signal Processing (DSP) units and embedded hardcore processors.

The proper activation of selected resources and the programming of interconnection thereof so as to map effectively an application into an FPGA emerge as important research subjects. Even more, performing these operations at run-time, i.e. dynamically altering part of the FPGA while the rest remains intact continuing its operation [Compton and Hauck, 2002], becomes more challenging although it is still in its infancy. Besides large FPGAs, this technology could benefit applications implemented in small FPGAs in which the gain would have different margins as compared to the former ones. For example, multiple design modules can time-share the physical resources, and the hardware can adapt to the application at hand or even to a segment of an application. In this way, smaller devices can be employed enabling reduction in cost, size and power, and more efficient use of the board space. In general, the use of PR technology for an application can be justified if benefits are gained with regard to factors such as resource savings, power reduction and higher performance over the static implementation.

#### 1.1 Motivation

Many efforts within the academia and a few among the industrial community exist, trying to establish dynamic reconfiguration as a feasible way to design commercial applications. It is considered to be the "holy grail" of reconfigurable computing and its effective exploitation could result in circuits that run applications more effectively over their static counterparts. In the network domain, a reconfigurable processor that was altered dynamically in order to meet the requirements of the network workload was proposed [Kachris and Vassiliadis, 2006]. Modules like encryption, compression and intrusion detection found in contemporary edge routers, are dynamically loaded according to the traffic distribution to serve the different network flows. In the field of Software Defined Radio (SDR), a prototyping kit was released to the market, which uses partial reconfiguration (PR) to support different communication waveforms and protocols within a single chip [Xilinx Inc., 2006b]; this allows for flexible and efficient communication between equipment that differs in vendor, Radio Frequency (RF) or interface protocol. Dynamic reconfiguration has also been used to support high energy physics research at CERN's Large Hadron Collider [Programmable Logic Design Line, 2008]. The latest achievement by the leading vendor in PR technology targets the networking domain. An integrated Optical Transport Network system has been demonstrated [Xilinx Inc., 2010b], in which considerable resource and power savings were achieved due to the use of PR technology.

The above are some of the systems that can establish dynamic reconfiguration as a feasible way to design commercial applications. At the same time issues such as when to use PR, why to use it, in what kind of applications and in which way remain open, though a considerable effort is made by the academia and industry towards addressing them. Present work aims at bridging the gap between theoretical research and real experimentation. The latter constitutes an effortful procedure due to the intrinsic difficulties of PR technology. The dissertation delves into the details of reconfiguration with real experiments and by using the feedback of the results it studies ways to use it effectively.

#### 1.2 Contribution

The dissertation is concerned with a task allocation and scheduling mechanism in PR FPGA-based systems, a formula to calculate the reconfiguration time, and a novel way to incorporate PR technology in an application domain. Among the experience gathered and the conclusions drawn, an experimental framework was developed on a PR FPGA-based platform. The contributions of the dissertation consist in:

- an in-depth literature review covering a wide area of issues related with PR technology,

- a resource-aware task scheduling algorithm to exploit effectively the area of a dynamically reconfigurable FPGA,

- a cost model extracted from real experiments and theoretical analysis to quantify the reconfiguration overhead for various setups which can be used in an early-assessment stage of the development procedure,

- evaluation of the impact of reconfiguration overhead in recovering a PR system that is subject to error upsets, and a scheme exhibiting resource savings over the dominant solution in the domain of error diagnosis and recovery.

It should be noted that due to the rapid changes in the specific subject, the direction of the dissertation had to be devised some times. At the same time although PR technology is around for almost 20 years, no killer application exists yet. Present dissertation delves into different research subjects, i.e. task scheduling and allocation, reconfiguration overhead and a novel scheme for fault-prone systems, and ends up with conclusions that can be considered when building systems using PR technology. All experiments were carried out on mature FPGAs, i.e. Xilinx Virtex-II Pro and Virtex-5 FPGAs. Virtex-6 and Virtex-7 FPGAs were released from Xilinx when the dissertation was close to its completion.

#### 1.3 Structure

The dissertation is structured as follows:

- Chapter 2 is devoted to the background of reconfigurable computing targeting mainly the dynamic nature of programmable chips. A wide spectrum of subjects related with the PR technology is analyzed to reveal the research status and open problems. It appears that although the PR topic has been studied intensively, several subjects need to be revisited.

- **Chapter 3** presents a new task scheduling mechanism that increases the utilization of the physical resources. Furthermore, a reusable framework that models dynamically reconfigurable systems and accepts attributes entered by the user has been developed for evaluating the task scheduling mechanism. The framework is generic so as to be used for researching and evaluating similar mechanisms.

- Chapter 4 presents an experimental framework deployed on an FPGA-based platform which allows for extensive experimentation and evaluation of PR technology. The values gathered with this platform are used in Chapter 5.

- Chapter 5 examines the different setups and factors affecting the reconfiguration time. Also, a cost model that applies in a range of platforms has been developed which was verified using a real-world system and evaluated upon works published by other researchers. This Chapter constitutes an integral work as it surveys the domain related with the reconfiguration overhead at system-level. Also, it analyzes a variety of setups and the factors contributing to the reconfiguration process.

- Chapter 6 studies the use of PR technology on a real-world application that has proven (based on the literature) to benefit from partial reconfiguration. It falls into the domain of error diagnosis and recovery for non critical systems. A novel scheme combining software and hardware is described, which supplies the core of an FPGA chip with self-repairing capability. Protection concerns the configuration memory of FPGA as well as instantaneous errors affecting the implemented circuit.

Chapter 7 summarizes the contributions of the dissertation and discusses the future work.

All Chapters begin with an introductory section along with a reference to an up-to-date relevant work. Although each one of the Chapters constitutes a coherent work, they all complement each other. In particular, the experimental framework of Chapter 4 was used to extract the cost model in Chapter 5. In turn, the information and the cost model of Chapter 5 can be used as feedback for inserting realistic attributes to the simulation framework of Chapter 3. Also, the cost model can be used for assessing the system presented in Chapter 6 for different setups.

## Chapter 2

## State of the Art

Reconfigurable computing has become a subject of a great deal of research during the last decade. The present Chapter begins with a historical evolution of reconfigurable devices. Then, it concentrates on systems supporting dynamic reconfiguration. First, it discusses the different theoretical perspectives that have been proposed to study its performance. Then, several dynamic architectures and the software tools to support them are described. Furthermore, a variety of applications implemented with dynamic reconfiguration is presented. Finally, the overhead incurred by dynamic reconfiguration and the research efforts to reduce its effects on performance are described. Throughout the present work the benefits and the weaknesses of dynamic reconfiguration as well as the effort to deal with it are discussed. This allows to examine the potential improvements of its use in modern systems and applications.

#### 2.1 Introduction

As of 2004, the computer industry has hit a roadblock in getting further performance gains from instruction level parallelism [Olukotun and Hammond, 2005]. Following Moore's law regarding performance, computer architects and designers have started to open new directions in developing computing systems. Hence, the industry is heading towards exploiting higher levels of available parallelism through techniques like multiprocessing and multithreading. On the other hand, reconfigurable computing since its early appearance has been intended to fill the gap between hardware, e.g. application specific integrated circuits (ASIC), and software, e.g. microprocessors  $(\mu P)$ , achieving potentially higher performance than software while maintaining a higher level of flexibility than hardware [Compton and Hauck, 2002]. The stronger representatives of Reconfigurable computing are the SRAMbased Field Programmable Gate Arrays (FPGAs). Systems incorporating a fixed processing unit (FPU) such as software microprocessors and a reconfigurable processing unit (RPU) such as field programmable gate arrays (FPGAs) onto a single chip have become state-of-theart devices known as reconfigurable processors. Also, super-computing systems combining fixed and reconfigurable resources were released aiming at speeding up custom applications such as systems released by the Convey Computer [Convey, 2011], the Maxeler Technologies [Maxeler, 2011] and Pico Computing [Pico Computing, 2011], which followed the steps of Cray XD1 Supercomputer [Cray, 2008], one of the earliest large-scale products combining microprocessors and FPGAs. Computationally-intensive tasks can be entirely executed in the reconfigurable fabric that can efficiently exploit the application's inherent parallelism. Furthermore, reconfigurable fabrics that adapt to the needs of the application task at hand at run-time have been proposed. Factors such as speed, area, power and energy consumption can be optimized due to the ability of the hardware to adapt to the characteristics of an application. This could boost the necessity of integrating reconfigurable processing units into contemporary systems whether they target the field of general purpose or embedded computing. Currently, almost all applications running in FPGAs as end-products do not make full use of their reprogrammable nature. When FPGAs are used either to rapidly prototype circuits or in designs where a small production run is expected they are usually programmed only once at power-up and after this the circuit remains unchanged.

Before proceeding with the main subject of this Chapter, some terms need to be clarified. Reconfiguration is defined as the capability of the hardware to be modified in the field such as the hardware resources to be used and their interconnection after it is initially configured. It is distinguished in two main categories, static and dynamic reconfiguration. Static reconfiguration is performed at shut-down mode, i.e. the hardware is modified when the device is inactive, while dynamic reconfiguration is performed during execution, i.e. the device is active. Two subcategories exist, full and partial reconfiguration. Full reconfiguration, in which the entire configuration is modified, is performed only under static mode as the reprogramming of the entire device is required. Partial reconfiguration, in which part of the hardware is modified while the rest remains unchanged, can be performed either under static or dynamic mode. Static partial reconfiguration is done when the device is inactive and the unchanged part retains its configuration information. Dynamic partial reconfiguration allows for swapping tasks in and out from specific areas of the hardware while the remaining logic continues undisturbed its execution. The concept of partially reconfiguring the hardware during execution is also known as active partial reconfiguration (APR) [Xilinx Inc., 2004a], run-time reconfiguration (RTR), on-the-fly reconfiguration or simply dynamic reconfiguration. In the present dissertation these terms are used interchangeably. One of the earliest works clarifying terminology on reconfiguration was published in [Lysaght and Dunlop, 1993].

Full reconfiguration incurs a significant amount of data to be swapped in and out of the hardware, which combined with the stall of execution restricts its applicability to applications in which reconfiguration delay degrades the overall performance. On the other hand, dynamic partial reconfiguration provides a more flexible way to deal with versatility and area utilization of reconfigurable resources as part of the hardware logic can be reconfigured while the rest hardware is in operation. This allows to extend the use of reconfigurable systems beyond emulation and rapid system prototyping. Many applications require a large amount of area in the fabric for their processes to be carried out. However, die cost is proportional to the fifth or higher power of the die area [Hennessy and Patterson, 2003] (pp. 21-22). Thus designers can reduce the cost by building smaller chips. Toward the same direction, developers can minimize the resources usage and consequently the chip size when different stages of the application are executed by the same hardware in different time slots. Having flexible means of fabric that can be modified at run-time to execute different tasks of the same application or different tasks serving different applications is appealing. Furthermore, circuits can be specialized according to parameters being changed at run-time, potentially resulting in a superior system over the static alternative [McKay et al., 1998, McKay and Singh, 1998, Gonzalez et al., 2003]. Going one step further, leaving hardware areas unoccupied and configure them according to the state of the application allows for energy savings as it is unnecessary to keep idle tasks in the hardware; unless these tasks are executing, leaving them out of the hardware can result in less energy consumption. The benefits offered by dynamic reconfiguration are recapitulated as follows:

- Hardware sharing by time multiplexing hardware tasks

- On-the-fly adaptation of the hardware according to the changing needs of the application

- Reduced device count

- Reduced power consumption (for infrequent reconfiguration)

- Reduced cost

At its earliest stage dynamic reconfiguration was introduced as virtual hardware which is similar to the concept of virtual memory [Brebner, 1996]. A few years ago, self-reconfiguring systems became feasible by offering the ability to modify the functionality of their hardware at run-time according to the application needs [Blodget et al., 2003]. In such a system an integrated processor undertakes the tasks of controlling and reconfiguring the reconfigurable hardware, while the latter executes the computationally-intensive tasks.

Numerous comprehensive surveys on reconfigurable computing have been published [Villasenor and Hutchings, 1998, Hauck, 1998b, Miyazaki, 1998, Tessier and Burleson, 2001, Hartenstein, 2001, Bondalapati and Prasanna, 2002, Compton and Hauck, 2002, Todman et al., 2005]. Some surveys attempt to classify reconfigurable systems according to specific aspects [Radunovic and Milutinovic, 1998, Enzler, 1999, Barat and Lauwereins, 2000, Schaumont et al., 2001, Barat et al., 2002, Sima et al., 2002, Donthi and Haggard, 2003, Amano, 2006]. In [Gokhale and Graham, 2005], after an introduction to the reconfigurable computing, several reconfigurable architectures, systems with reconfigurable devices, programming languages and implementations of different application domains are presented. An interesting catalog is available in [DeHon et al., 2004], which studies over one hundred works related to reconfigurable computing in order to classify them according to design patterns. Design patterns are defined as solutions to common and recurring design challenges in reconfigurable systems and applications. In [Bobda, 2007], various reconfigurable architectures and issues like design flow, high-level synthesis, temporal placement, on-line communication, partial reconfiguration and different domains of applications implemented in reconfigurable devices are discussed. Recently, a comprehensive collection was published covering a broad range of topics on reconfigurable computing [Hauck and DeHon, 2008]. This collection covers subjects like reconfigurable architectures, programming languages, operating systems, compilation, placement, mapping, routing, hardware/software partitioning and a variety of applications. Finally, the authors in [Garcia et al., 2006] target the embedded systems domain. They discuss topics such as benefits gained in applications implemented with reconfigurable hardware, basic architectural aspects, critical design issues for embedded systems, and design tools to develop such systems.

Although the above works do not target dynamic reconfiguration only, a few refer or devote a section to it. In [Compton and Hauck, 2002], a dedicated section addresses issues on run-time reconfiguration regarding architecture structures, run-time partial evaluation, compilation and configuration scheduling, supporting software, techniques to reduce reconfiguration overhead as well as existing problems of this technology. A more recent survey [Todman et al., 2005] discusses dynamic reconfiguration and its research directions in an abstract level. A few papers survey some commercial dynamically reconfigurable FPGA devices [Donthi and Haggard, 2003], and commercial coarse-grained dynamically reconfigurable processors [Amano, 2006]. The former evaluates FPGA architectures based on their granularity and their reconfiguration time, whereas the latter examines issues such as structure of the basic processing elements, dynamic reconfigurability, processor-coupling, interconnection and programming software. In [Bobda, 2007] a Chapter is devoted on partial reconfiguration targeting Xilinx devices. In [Hauck and DeHon, 2008] a dedicated section on reconfiguration management and a case study of partial reconfiguration are included. In [Garcia et al., 2006], issues such as real-time operating systems and scheduling for runtime reconfigurable systems, relocation and defragmentation of configurations, and research for hiding configuration overhead are discussed.

Present Chapter intends to complement the above works by presenting details on various aspects of dynamic reconfiguration and providing background information from the earliest up to the latest achievements. This is done by:

- presenting a historical evolution of reconfigurable devices with a critical analysis on academic and industrial research results on dynamic reconfiguration to date.

- presenting various theoretical perspectives that examine the performance of dynamic reconfiguration.

- providing up-to-date information on recent advances in architectures and software tools.

- discussing the application domains that can benefit from their implementation in dynamically reconfigurable hardware.

- presenting the research on techniques for scheduling and partitioning the dynamically reconfigurable tasks as well as on allocation of reconfigurable resources.

This Chapter merges the conducted research, the open directions and the way in which dynamic reconfiguration can be incorporated in computing systems. Although it does not cover every research project, it serves as an in-depth introduction to the rapidly evolving field of dynamically reconfigurable computing. It is organized as follows. Section 2.2 has the historical evolution of reconfigurable computing along with a classification of reconfigurable systems with respect to their structure. In Section 2.3 the main research topics on dynamic reconfiguration are discussed. Section 2.4 presents theoretical approaches studying its performance. Sections 2.5 and ?? examine the various architectures and the software developed to support them respectively. In Section ?? several applications deployed on dynamically reconfigurable systems are presented. Section ?? discusses reconfiguration overhead and research efforts to reduce its effects on performance. Finally, Section ?? discusses the present status and future directions on dynamic reconfiguration research.

#### 2.2 Historical Evolution

Numerous structures have been proposed since the appearance of reconfigurable computing. At the beginning the single-context FPGA was developed. As the research evolved multicontext and partially reconfigurable structures were invented. Present Section overviews this evolution of reconfigurable computing systems and distinguishes devices from the academic and commercial areas with respect to their structure and the way they are reconfigured. This high-level classification is provided in order to avoid reporting further details at this point such as types and structures of reconfigurable resources, granularity, and supporting software; these are discussed in later Sections.

The following classification concerns SRAM-based reprogrammable devices only that can be potentially programmed unlimited times and in a short time compared with other alternatives. Antifuse and flash devices [Actel, 2007, Quicklogic, 2007] are not included as the former type is one-time programmable only, and the latter type needs long time to be programmed. Table 2.1 consolidates representative SRAM-based reprogrammable devices. Devices combining characteristics of more than one structure type may appear in more than one fields of Table 2.1. The devices of each structure type are put in chronological order according to their first announcement. Especially for the commercial devices, the year in which they entered the market is denoted on the right side of the reference. This can be found in web resources, e.g. a link on Altera mature devices with the year of their first release is available in [Altera, 2007]. In many cases, this information does not match with the dates of the corresponding references - data sheets in most of the cases - because their first releases have been withdrawn for some reason, e.g. maturity of a device or release of newer versions of data sheets that hampered the task of finding and including them in the literature part of the present dissertation. Alternatively, later versions of data sheets which include old devices that are either available in the library of MHL laboratory or still accessible through the web are cited. The remaining Section overviews single-context, multi-context and partially reconfigurable structures. A comprehensive analysis on these structures can be also found in [Compton and Hauck, 2002].

#### 2.2.1 Single Context

Single-context devices were proposed at the evolutionary beginning of reconfigurable computing. In these devices, any change in the configuration requires a complete device reprogramming. Hence, in order to reconfigure a single-context device the whole execution stalls and the new bitstream is loaded off-line. Then, execution starts according to the new

| 1  | ally reconfigurable (PR) structures.<br>Academic efforts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Commercial devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SC | PRISC [Razdan and Smith, 1994]<br>Datapath-FPGA [Cherepacha and Lewis, 1994]<br>HybridFPGA [Kaviani and Brown, 1996]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | XC2000/3000/4000/5000 [Xilinx, 1994] '85/'87/'91/?<br>Flex 8000/10K [Altera, 1995] '93/'95<br>Flex 6000 [Altera, 1998] '98<br>Spartan [Xilinx, 2002b] '98<br>Apex 20K [Altera, 1998] '98<br>Apex 20K [Altera, 1998] '98<br>Acex 1K [Altera, 2003] '00<br>Spartan-II [Xilinx, 2004] '00<br>Mercury [Altera, 2003] '00<br>Excalibur ARM [Altera, 2001] '00<br>E5 CSoC [Triscend, 2003] '00<br>Excalibur MIPS [Altera, 2001] '01<br>A7 CSoC [Triscend, 2000] '01<br>Apex II [Altera, 2002] '01<br>Stratix [Altera, 2005] '02<br>Cyclone [Altera, 2006] '04<br>Cyclone-II [Altera, 2006] '04                                                                                                                                                                                                                                                                                                                       |

| MC | WASMII [Ling and Amano, 1993]<br>DPGA [DeHon, 1994]<br>OneChip95 [Wittig, 1995]<br>TMFPGA [Trimberger et al., 1997]<br>CSRC [Scalera and Vazquez, 1998]<br>OneChip98 [Jacob, 1998]<br>MorphoSys [Singh, 1998]<br>DRLE [Fuji et al., 1999]<br>OneChip00 [Esparza, 2000]<br>SRGA [Sidhu et al., 2000]<br>ZIPPY [Enzler and Platzner, 2001]<br>XiRisc [Lodi et al., 2003]<br>PRMC [Smith and Xia, 2004]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | MAPL [Hawley, 1991] '91<br>SIDSA FIPSOC [Faura et al., 1997] '97<br>CS2112 RCP [Chameleon, 2000] '00<br>picoArray [PicoChip, 2008] '00<br>NEC DRP [Motomura, 2002] '02<br>DAPDNA-2 [IP Flex, 2008] '03                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| PR | DPGA [DeHon, 1994]<br>KressArray [Hartenstein et al., 1994]<br>COLT [Bittner et al., 1996]<br>MATRIX [Mirsky and Dehon, 1996]<br>RaPiD [Ebeling et al., 1996]<br>Garp [Hauser and Wawrzynek, 1997]<br>Chimaera [Hauck et al., 1997]<br>PipeRench [Schmit, 1997]<br>RAW [Waingold et al., 1997]<br>RAW [Waingold et al., 1997]<br>REMARC [Miyamori and Olukotun, 1998]<br>CoMPARE [Sawitzki et al., 1998]<br>PROTEUS [Dales, 1999]<br>CHESS [Marshall et al., 1999]<br>modified XC6200 [Compton, 1999]<br>unnamed [Pozzi, 2000]<br>DReAM [Alsolaim et al., 2000]<br>Molen [Vassiliadis et al., 2001]<br>HySAM [Bondalapati, 2001]<br>ZIPPY [Enzler and Platzner, 2001]<br>AMDREL [Soudris et al., 2002]<br>ADRES [Mei et al., 2003]<br>WARP [Stitt et al., 2003]<br>POEtic [Thoma et al., 2003]<br>DyNoC [Bobda et al., 2004]<br>ARCADE eFPGA [Nowak, 2004]<br>PRMC [Smith and Xia, 2004] | CAL [Algotronix, 1988] '88<br>ERA60100 [Plessey, 1990] '90<br>CLAy [National, 1993] '93<br>AT6000 [Atmel, 1993] '93<br>CLi6000 [Jenkins, 1994]<br>XC6200 [Xilinx, 1995] '95<br>NAPA1000 [National, 1996] '96<br>OR FPGA [Vasilko and Ait-boudaoud, 1996]<br>SIDSA FIPSOC [Faura et al., 1997] '97<br>PCA [Nagami et al., 1998]<br>DL6000 [DynaChip, 1998]<br>Orca Series 2/3/4 [Lucent, 1998] <'98<br>Quicksilver ACM [Quicksilver, 2007] '98<br>AT40K [Atmel, 2006] '98<br>Virtex [Xilinx, 1999] '98<br>D-Fabrix [Elixent, 2000] '00<br>ecS2112 RCP [Chameleon, 2000] '00<br>AT94K FPSLIC [Atmel, 2005] '00<br>XPP [Baumgarte et al., 2001] '01<br>Virtex-II [Xilinx, 2007e] '02<br>Cypress PSoC [Cypress, 2008] '02<br>DAPDNA-2 [IP Flex, 2008] '03<br>MeP+D-Fabrix [Toshiba, 2003] '03<br>Spartan-3 [?] '03<br>Virtex-4 [Xilinx, 2007e] '04<br>S5-engine [Arnold, 2005] '06<br>XPP-III [PACT XPP, 2008] '07 |

Table 2.1: Reconfigurable devices classified in single-context (SC), multi-context (MC) and partially reconfigurable (PR) structures.

configuration data. Xilinx XC2000 series [Xilinx, 1994] and Altera Flex 8000 series [Altera, 1995] were of this type. An innovative architecture was proposed in [Kaviani and Brown, 1996] combining a simple FPGA structure with CPLD in a single die. A few years later, several vendors coupled single-context structures with a hardware processor in the same die like Altera [Altera, 2001], and Tensilica [Triscend, 2000, Triscend, 2003]. The latter's technology was acquired by Xilinx in 2004. Towards this direction, softcore processors have been developed for reconfigurable logic like Nios [Altera, 2004] and Microblaze [Xilinx, 2007a] for Altera and Xilinx devices respectively. From the academia part, a few efforts proposing innovative single-context structures [Cherepacha and Lewis, 1994], and coupled devices [Razdan and Smith, 1994] were made in the early stages of reconfigurable computing.

#### 2.2.2 Multi Context

Multi-context devices include multiple memory bits for each programming bit location. They can be thought of as multiple planes of configuration information. One plane can be active at a given time, while new configuration data are loaded to another plane. This structure can be also viewed as a multiplexed set of single-context devices, which requires that a context be fully reprogrammed - in most cases - to perform any modification. Switching between planes (or contexts) can be performed in a single cycle. National Semiconductor MAPL was the first device to be considered as a multi-context device [Hawley, 1991]. From the academia part the first published multi-context device was WASMII [Ling and Amano, 1993]. Some of the earliest works were presented in [DeHon, 1994, Wittig, 1995, Trimberger et al., 1997]. Since then, various researchers have been involved with multi-context structures [Scalera and Vazquez, 1998, Jacob, 1998, Singh, 1998, Fuji et al., 1999, Esparza, 2000, Sidhu et al., 2000, Enzler and Platzner, 2001. A few such devices were commercialized such as the Field Programmable System-on-Chip (FIPSOC) by SIDSA [Faura et al., 1997], the Reconfigurable Communication Processor (RCP) by Chameleon Systems [Chameleon, 2000], the IPFLEX DAPDNA-2 [IP Flex, 2008] and the Dynamic Reconfigurable Processor (DRP) by NEC [Motomura, 2002]. The latter was the successor of the academic Dynamically Reconfigurable Logic Engine (DRLE) [Fuji et al., 1999] and NEC terminated its production in 2007. The FPGA presented in [Scalera and Vazquez, 1998], known as Context Switching Reconfigurable Computer (CSRC), was implemented by British Aerospace Systems [BAE, 2007] and was used for experimental purposes. Most of the above devices were augmented with a processor which controls reconfiguration and context-switching.

#### 2.2.3 Partially Reconfigurable

Partial reconfiguration allows to selectively modify part of the hardware while the remaining hardware retains its configuration. In static devices, execution stalls waiting for the selected part to be reconfigured. This operation resembles single-context devices operation except that a partially reconfigurable device allows partial modifications of the fabric. Such devices are Garp [Hauser and Wawrzynek, 1997], CHESS [Marshall et al., 1999] and its commercial successor D-Fabrix [Elixent, 2000] - later bought by Matsushita Electronics Corp. -, and Molen [Vassiliadis et al., 2001]. The more sophisticated dynamically reconfigurable structure allows for the rest of the device to continue uninterrupted its execution. The first commercial device supporting dynamic reconfiguration was Algotronix CAL [Algotronix, 1988], which was introduced in 1988. A few years later National Semiconductor CLAy [National, 1993] and ATMEL AT6000 [Atmel, 1993] announced the support of this feature. Since then, various vendors like Xilinx [Xilinx, 1995, Xilinx, 1999, Xilinx, 2007d, Xilinx, 2007e, Xilinx, 2007c, Xilinx, 2008b, Xilinx Inc., 2008, Lucent [Lucent, 1998] and PACT XPP [Baumgarte et al., 2001, PACT XPP, 2008] have released such products. For sake of history, Xilinx XC6200 [Xilinx, 1995] was designed based on Algotronix CAL after Xilinx acquired Algotronix technology. The high-end Virtex series have also retained some of its features. Lattice supplied the ORCA series 2/3/4 devices [Lucent, 1998] that support dynamic reconfiguration. The company has entered the market of FPGAs after the purchase of the Agere Systems - formerly Lucent Technologies and before that AT&T Microelectronics. Although Lattice ORCA series support partial reconfiguration while in operation, there is no published record of applications implemented with this feature and as a consequence they have been reported as single-context devices in the literature [Compton and Hauck, 2002]. From the academia part, due to the rich area of research that dynamic reconfiguration technology offers, many groups have been involved with developing such structures [Hartenstein et al., 1994, Bittner et al., 1996, Ebeling et al., 1996, Hauck

et al., 1997, Schmit, 1997, Miyamori and Olukotun, 1998, Alsolaim et al., 2000, Enzler and Platzner, 2001, Mei et al., 2003, Stitt et al., 2003, Bobda et al., 2004]. Designing proprietary architectures rather than using commercial ones allowed researchers to have full control of their characteristics and apply modifications according to the changing needs. There exist several efforts on innovative partially reconfigurable structures and ways to reprogram them [Plessey, 1990, Vasilko and Ait-boudaoud, 1996, Nagami et al., 1998, DynaChip, 1998]. PRMC [Smith and Xia, 2004] suggests a multi-context, partially reconfigurable homogeneous fine-grain array. Moreover, following the concept of the first two structures both academic and commercial partially reconfigurable structures, i.e. single-context and multicontext, tend to incorporate a processor which acts as a reconfiguration controller amongst other tasks. Finally, multi-context structures have been leveraged to allow partial loading of inactive contexts [DeHon, 1994, Mirsky and Dehon, 1996, Faura et al., 1997, Chameleon, 2000, IP Flex, 2008, Lodi et al., 2003, Smith and Xia, 2004]. To the best of the author's knowledge there does not exist an academic or a commercial multi-context device supporting partial reconfiguration of the active context.

#### 2.2.4 Discussion Summary

In this Section a classification of reconfigurable devices according to their structure from the reconfiguration point of view, the year they were announced, and whether they come from the academia or the commercial area has been given. The above list includes fine-, coarse-, medium-, and mixed-grained, coupled and uncoupled with a microprocessor, homogeneous and heterogeneous reconfigurable devices. Some of them fall into the category of FPGAs whereas others are SoCs. In addition, there exist devices and derivatives of the reported commercial devices enhanced with a variety of hardware cores, e.g. PCI and phase-locked loops(PLLs). Similar lists can also be found in active web sites [Berkeley, 2007, Ottawa, 2007, Erasmushogeschool, 2007]. In spite of the large amount of existing reconfigurable architectures the market is still dominated by FPGA devices and in particular those from Xilinx and Altera. The latter vendor has recently started putting effort in developing dynamically reconfigurable FPGAs, e.g. transceivers in Stratix-II GX device can be reprogrammed on the fly to support multiple protocols, data rates and physical medium attachment settings. Moreover, the coarse-grained reconfigurable devices market has not taken off yet despite the amount of prototypes developed in this direction.

The reconfiguration capabilities of these devices have also been described. Single-context structure requires full reconfiguration whereas in the other two structures only a part can be reconfigured. Although in most of the multi-context devices a full-context is reconfigured while another is active, there are few multi-context devices of which only a part of an inactive context can be reconfigured while another context executes. Partially reconfigurable structures incur small reconfiguration overhead in applications that do not require the device to be completely reconfigured; however, depending on the application needs this might not be negligible with respect to the total execution time. Alternatively, a system consisting of multiple single-context reconfigurable devices each of which is separately reconfigured can be employed, but off-chip communication and extra space on the board increase the cost of speed, area and power consumption. Similarly, a multi-context device carries significant reconfigurable area incurring high interconnection delay, low computational density and suffers from various delays and high-costs due to large storage silicon area, i.e. multicontext configuration memory; thus it is more applicable in coarse-grain devices. In a single partially reconfigurable device the trade-offs between the above factors are more efficiently balanced.

Table 2.1 illustrates that substantial efforts have been made in developing multi-context and partially reconfigurable architectures (statically partially reconfigurable architectures aren't distinguished from the dynamically ones). Although the list is far from being complete it demonstrates that there is an increasing interest from the academia and industry for such devices. Although some commercial efforts have been abandoned the lessons learned - which are basically given by the market applications - are changing the directions; but research for dynamic reconfigurable devices and particularly on systems combining a fixed processor with a reconfigurable hardware onto the same die. In this scenario the processor usually undertakes the reconfiguration task; however, there exist devices in which a dedicated reconfiguration controller undertakes this task [Baumgarte et al., 2003].

#### 2.3 Research Topics on Dynamic Reconfiguration

Although dynamic reconfiguration is a fascinating feature many scientists have been cautious regarding its feasibility and value. Its use has been restricted within the borders of research, and none to very few commercial applications have been implemented in a dynamic manner. The lack of an operational framework, and its tedious design flow have kept this technology from being widely accepted by the community. As of 2006 a new method has been announced to support dynamic reconfiguration [Lysaght et al., 2006]. It offers a graphical environment and its main scope it to abstract the details of the rigorous design flow of dynamic reconfiguration from the developer.

Commercial applications implemented in a dynamic manner have also been released. A prototyping-to-production kit that accelerates implementation of software defined radio (SDR) modems has been announced by Xilinx and ISR technologies [Xilinx and ISR, 2006]. SDR is a radio communication system supporting different transmission protocols and it allows for the modulation and demodulation of signals to be implemented in software. This provides flexibility to the customer, and Xilinx has taken advantage of the flexibility supported by its devices. Thus it transferred the implementation in hardware to reach high performance and change the algorithms at run-time. It is the industry's first SDR kit to support partial reconfiguration, which exploits this feature to reduce power and cost in developing SDR systems. In the context of networking, Xilinx released an industrial crossbar switch in which the routing resources are modified during operation [Xilinx, 2002a]. These products demonstrate that dynamic reconfiguration technology is now feasible, and it is time to start exhibiting the advantages of reconfigurable computing in more areas. On the other hand, there are several issues that remain to be solved to enable the access of this technology to the mainstream. This Section introduces the main research aspects on dynamic reconfiguration that are discussed later.

• Several works study dynamic reconfiguration from a *theoretical perspective*. This way issues like efficient handling of dynamically reconfigurable tasks and the impact of dynamic reconfiguration on speed and area are theoretically elaborated. As the technology evolves it would be useful to explore the applicability of these studies on recent

systems.

- The demanding adaptation of the hardware to the application at hand has led the exploration of numerous *architectures*. Coarse-grained, fine-grained and architectures integrating a fixed processor onto a single chip that support dynamic reconfiguration have been proposed. Moreover, issues such as which component undertakes the reconfiguration process, i.e. a processor or a dedicated configuration manager, the size of the smallest unit to be reconfigured, and the way the unit to be reconfigured is located should be addressed when designing an architecture.

- A variety of *software tools* have been developed to support dynamically reconfigurable architectures. The design flow of dynamic reconfiguration is rigorous compared with the traditional design flow. Thus abstracting the low-level details from the designer is a major issue and efficient mapping of applications to the hardware without knowing its details is a challenging problem. Nowadays the trend is moving towards designing applications in high-level programming languages with interfaces that can be efficiently handled by the average software programmer. The simplest way is generating data-flow graph from a C-like language and map them into the array.

- Significant efforts by the academia and the industry are made to establish dynamic reconfiguration as a feasible way in designing *applications*. Its performance has been investigated with respect to factors such as speed, area and power. Restrictions on these factors have to be considered when employing dynamic reconfiguration to execute an application. The question is under which conditions dynamic reconfiguration prevails over alternative approaches. The type of applications that can benefit from dynamic reconfiguration vs. alternative solutions like ASIC and general-purpose processors are still under research.

- Benefits of dynamic reconfiguration do not come without cost. The inherent high latency and low throughput of the reconfiguration process compared with other processes incurs degradation in overall system performance known as *reconfiguration overhead*. In the 1st NASA/DOD Workshop on Evolvable Hardware, it was reported that

while reconfigurability was a major theme in DARPA's Adaptive Computer Systems program, the big stumbling block at the time was the large reconfiguration time of modern platforms [Munoz, 1999]. In order to harness this overhead which can take microseconds or longer, fast configuration was a critical issue. Since then, the problem has been dealt with techniques such as configuration caching, configuration compression and configuration prefetching [Li, 2002]. Moreover the problem has been addressed in the context of placing the dynamically reconfigurable tasks on the hardware in an efficient manner. Research on task scheduling, resource allocation, HW/SW partitioning mechanisms and efficient placement has been conducted to deal with this problem [Brebner and Diessel, 2001,Noguera and Badia, 2002,Steiger et al., 2004,Banerjee et al., 2005b,Singhal and Bozorgzadeh, 2006].