## An Embedded USB Controller Linux Device Driver: Common Practices and Experience

Dimitris Lampridis

May 13, 2005

## Contents

| 1 | Intro | oduction                                 | 1        |

|---|-------|------------------------------------------|----------|

|   | 1.1   | Introduction to Embedded Devices         | 1        |

|   |       | 1.1.1 Embedded System Platforms          | 2        |

|   |       | 1.1.2 Embedded Operating Systems         | <b>2</b> |

|   |       | 1.1.3 The Need for Device Drivers        | 3        |

|   |       | 1.1.4 Linux for Embedded Devices         | 4        |

|   | 1.2   | Device Drivers: Basic Principles         | 5        |

|   |       | 1.2.1 The Role of a Device Driver        | 5        |

|   |       | 1.2.2 Kernel & User Space                | 5        |

|   |       | 1.2.3 Security Issues                    | 6        |

|   | 1.3   |                                          | 7        |

|   |       | 1.3.1 Thesis Goals                       | 7        |

|   |       | 1.3.2 Thesis Results                     | 8        |

|   |       | 1.3.3 Thesis Outline                     | 9        |

| 2 | The   | Universal Serial Bus                     | 10       |

|   | 2.1   | Background                               | 10       |

|   |       | 2.1.1 Goals for the Universal Serial Bus | 11       |

|   |       | 2.1.2 USB Features                       | 11       |

|   | 2.2   | Architectural Overview                   | 13       |

|   |       | 2.2.1 USB Topology                       | 13       |

|   |       | 2.2.2 USB Hosts                          | 13       |

|   |       | 2.2.3 Dynamic Device Attachment          | 14       |

|   | 2.3   | USB Data Flow Modes                      | 15       |

|   |       | 2.3.1 Transfer Modes                     | 16       |

|   | 2.4   | USB Device Framework                     | 18       |

|   |       | 2.4.1 USB Hubs                           | 18       |

|   |       | 2.4.2 USB Functions                      | 19       |

|   |       | 2.4.3 USB Device Endpoints               | 20       |

|   |       | 2.4.4 USB Pipes                          | 21       |

|   | 2.5   |                                          | 22       |

|   |       | 2.5.1 Composition of USB Descriptors     | 23       |

|   | 2.6   | USB Host: Hardware & Software            | 23       |

|   |     | 2.6.1 Host Co       | ontroller Requirements                 |   | <br>23 |

|---|-----|---------------------|----------------------------------------|---|--------|

|   |     | 2.6.2 Overvie       | ew of the USB Host                     |   | <br>24 |

|   |     | 2.6.3 USB Bus       | s Interface                            |   | <br>25 |

|   |     | 2.6.4 USB Sys       | . <mark>tem</mark>                     |   | <br>27 |

|   |     |                     | ontroller Driver                       |   | 27     |

|   |     | 2.6.6 USB Driv      | ver                                    |   | <br>28 |

|   | 2.7 | The Root Hub        |                                        |   | <br>28 |

|   |     | 2.7.1 Hub Re        | equests & Descriptors                  |   | <br>29 |

|   |     |                     | chitecture & Supported Speeds          |   | 30     |

|   |     |                     | onnectivity                            |   | 30     |

|   |     |                     | nt Organization                        |   | 31     |

|   |     |                     | ange Information Processing            |   | 31     |

|   |     |                     | nd Port Status Change Bitmap           |   | 31     |

|   |     |                     | urrent Reporting and Recovery          |   | 32     |

|   |     |                     | ration Handling                        |   | 32     |

|   |     |                     | <b>0</b>                               |   |        |

| 3 | The | Linux USB Subs      | ystem                                  |   | 33     |

|   | 3.1 | <b>USB-Standard</b> | Types                                  |   | <br>34 |

|   |     | 3.1.1 Contro        | I Request Support                      |   | <br>34 |

|   |     | 3.1.2 Standa        | rd Descriptors                         |   | <br>34 |

|   | 3.2 | Upper (Host-S       | ide) API Model                         |   | <br>37 |

|   |     | 3.2.1 Host-Sid      | de Data Types                          |   | <br>38 |

|   | 3.3 | USB Core APIs       |                                        |   | <br>39 |

|   |     | 3.3.1 The Stru      | ucture of USB Request Blocks (URBs)    |   | <br>39 |

|   |     | 3.3.2 URB Mc        | anipulation Functions                  |   | <br>43 |

|   | 3.4 | Host Controlle      | er ÁPIs                                |   | <br>44 |

|   |     | 3.4.1 Host Co       | ontroller Data Types                   |   | <br>44 |

|   |     | 3.4.2 Host Co       | ontroller Functions                    |   | <br>49 |

|   |     |                     |                                        |   |        |

| 4 |     |                     | pedded USB Host Controller             |   | 51     |

|   | 4.1 |                     | er Internal Registers                  |   | 52     |

|   |     |                     | ub Registers                           |   | 53     |

|   | 4.2 | Microprocess        | or Bus Interface                       | • | <br>54 |

|   |     |                     | mmed I/O (PIO) Addressing Mode         |   | 54     |

|   |     | 4.2.2 DMA N         |                                        |   | 56     |

|   |     |                     | I Registers Access by PIO Mode         |   | 57     |

|   |     |                     | Iffer RAM Access by PIO Mode           |   | 58     |

|   |     | 4.2.5 FIFO Bu       | Iffer RAM Access by DMA Mode           |   | <br>58 |

|   |     |                     | ots                                    |   | 58     |

|   | 4.3 |                     | er (HC) Functionality                  |   | 60     |

|   |     |                     | SB States                              |   | 60     |

|   |     | 4.3.2 USB Tra       | ffic Generation                        |   | <br>60 |

|   |     | 4.3.3 The Stru      | ucture of Philips Transfer Descriptors |   | <br>62 |

|   |     | 4.3.4 Interna       | I FIFO Buffer RAM Data Organization .  |   | <br>66 |

|   |     |                     |                                        |   |        |

|   |       | 4.3.5 HC Operational Model                         |

|---|-------|----------------------------------------------------|

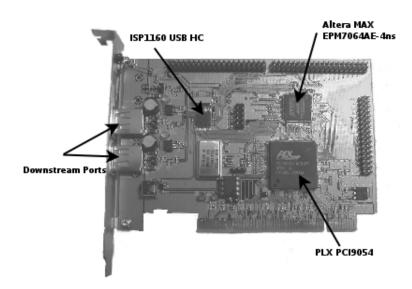

|   | 4.4   | The ISP1160 PCI Development Board                  |

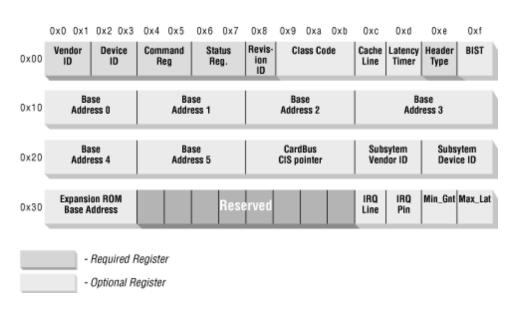

|   |       | 4.4.1 PCI Bus Overview                             |

|   |       | 4.4.2 The PLX9054 PCI I/O Accelerator              |

| 5 | ISP 1 | 160 PCI Driver Implementation 73                   |

|   | 5.1   | Important Data Structures                          |

|   | 5.2   | PCI Module Initialization                          |

|   |       | 5.2.1 PCI Device Probing                           |

|   |       | 5.2.2 PCI I/O Resource Allocation                  |

|   |       | 5.2.3 ISP1160 Initialization                       |

|   |       | 5.2.4 PCI Module Cleanup                           |

|   | 5.3   | Data Transfer Management                           |

|   |       | 5.3.1 The Interrupt Handler                        |

|   |       | 5.3.2 Root Hub Status Change and the "KHUBD" 88    |

|   |       | 5.3.3 Data Transfer Interrupts: ATLint & SOFint 89 |

|   |       | 5.3.4 Arrival of new URBs                          |

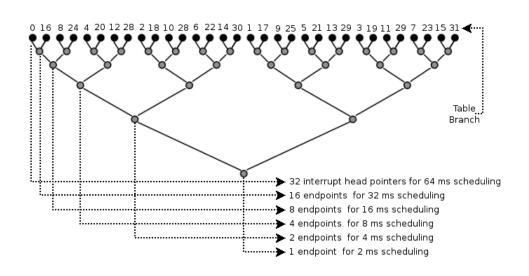

|   |       | 5.3.5 Interrupt Polling Rate                       |

|   |       | 5.3.6 Data Transfer to HC's Memory                 |

|   |       | 5.3.7 Data Transfer from HC's Memory               |

|   | 5.4   | Results                                            |

|   |       | 5.4.1 Insertion & Removal of the Driver            |

|   |       | 5.4.2 Hardware Functionality                       |

|   |       | 5.4.3 Driver Policy                                |

|   |       | 5.4.4 OS Integration                               |

|   |       | 5.4.5 Security                                     |

|   |       | 5.4.6 Driver Porting                               |

|   | 5.5   | Testing & Performance                              |

|   |       | 5.5.1 Testing                                      |

|   |       | 5.5.2 Performance Evaluation                       |

| 6 |       | clusions 106                                       |

|   | 6.1   | Further Work                                       |

| Α | USB   | Requests 110                                       |

|   | A.1   | USB Device Requests                                |

|   | A.2   | Standard Device Requests                           |

|   |       | A.2.1 Request Descriptions                         |

|   | A.3   | Hub Requests                                       |

|   |       | A.3.1 Standard Requests                            |

|   |       | A.3.2 Class-Specific Requests                      |

| В | USB Descriptors 121                        |

|---|--------------------------------------------|

|   | B.1 Device Descriptor                      |

|   | B.2 Configuration Descriptor               |

|   | B.3 Interface Descriptor                   |

|   | B.4 Endpoint Descriptor                    |

|   | B.5 String Descriptor                      |

|   | B.6 Class- & Vendor-specific Descriptors   |

|   | B.6.1 Hub Descriptor                       |

| С | ISP1160 Internal Registers 131             |

|   | C.1 HC Control and Status Registers        |

|   | C.1.1 HcRevision                           |

|   | C.1.2 HcControl                            |

|   | C.1.3 HcCommandStatus                      |

|   | C.1.4 HcInterruptStatus                    |

|   | C.1.5 HcInterruptEnable                    |

|   | C.1.6 HcInterruptDisable                   |

|   | C.2 HC Frame Counter Registers             |

|   | C.2.1 HcFmInterval                         |

|   | C.2.2 HcFmRemaining                        |

|   | C.2.3 HcFmNumber                           |

|   | C.2.4 HcLSThreshold                        |

|   | C.3 HC Root Hub Registers                  |

|   | C.3.1 HcRhDescriptorA                      |

|   | C.3.2 HcRhDescriptorB                      |

|   | C.3.3 HcRhStatus                           |

|   | C.3.4 HcRhPortStatus(1:2)                  |

|   | C.4 HC DMA and Interrupt Control Registers |

|   | C.4.1 HcHardwareConfiguration              |

|   | C.4.2 HcDMAConfiguration                   |

|   | C.4.3 HcTransferCounter                    |

|   | C.4.4 Hc $\mu$ PInterrupt                  |

|   | C.4.5 Hc $\mu$ PInterruptEnable            |

|   | C.5 HC Miscellaneous Registers             |

|   | C.5.1 HcChipID                             |

|   | C.5.2 HcScratch                            |

|   | C.5.3 HcSoftwareReset                      |

|   | C.6 HC Buffer RAM Control Registers        |

|   | C.6.1 HcITLBufferLength                    |

|   | C.6.2 HcATLBufferLength                    |

|   | C.6.3 HcBufferStatus                       |

|   | C.6.4 HcReadBackITL0Length                 |

|   | C.6.5 HcReadBackITL1Length                 |

|   | C.6.6 HcITLBufferPort                      |

| C.6.7 HcATLBufferPort | 100 |

|-----------------------|-----|

|-----------------------|-----|

# **List of Figures**

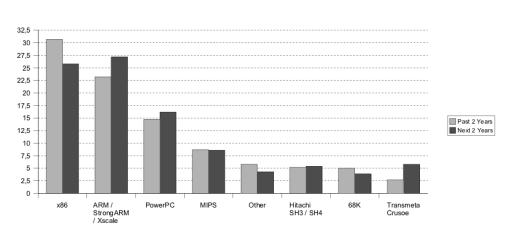

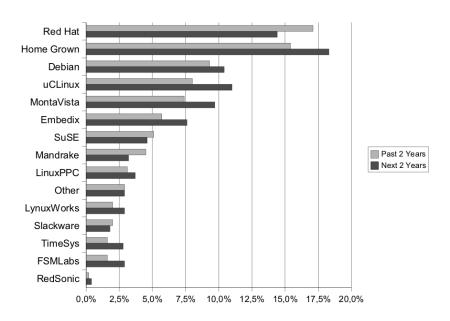

| 1.1<br>1.2                                           | Embedded System Architectures SurveyEmbedded Linux Distributions                                                                                                                                                          | $\frac{2}{4}$                                                  |

|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

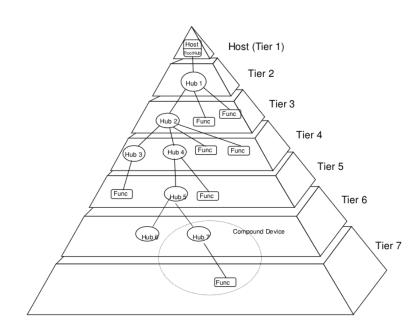

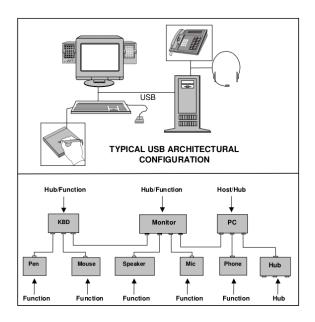

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8 | Topology of the USB BusA Typical USB HubHubs in a Desktop Computer EnvironmentAddressing of Device EndpointsHierarchy of the USB DescriptorsUSB Interlayer Communication ModelUSB Host CommunicationsUSB Driver Structure | 14<br>18<br>19<br>20<br>22<br>25<br>26<br>29                   |

| 3.1<br>3.2                                           | Linux USB Core API Layers                                                                                                                                                                                                 | 33<br>38                                                       |

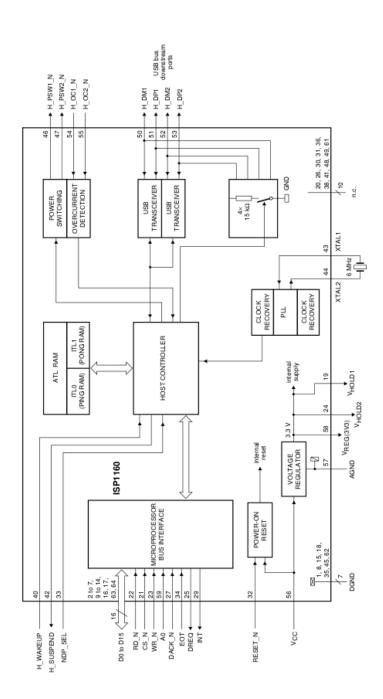

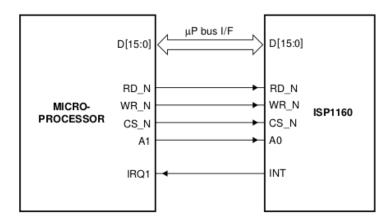

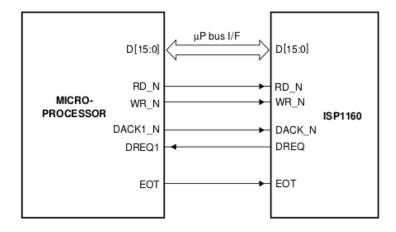

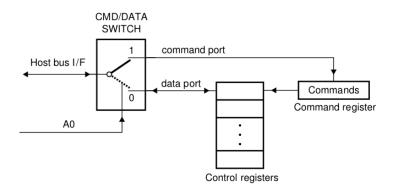

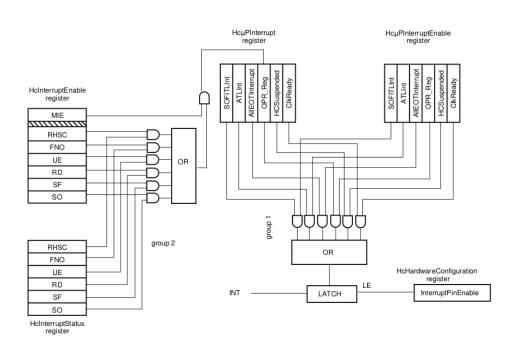

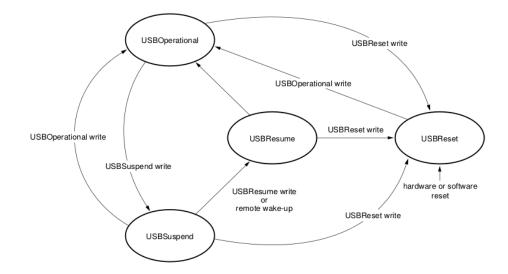

| 4.11                                                 | Block Diagram                                                                                                                                                                                                             | 55<br>56<br>57<br>59<br>60<br>61<br>63<br>67<br>68<br>69<br>71 |

| 5.1<br>5.2                                           | Interrupt Polling Intervals                                                                                                                                                                                               | 91<br>96                                                       |

|                                                      |                                                                                                                                                                                                                           |                                                                |

## **List of Tables**

| 2.1                                                   | USB supported speeds                                                                                                                                                                         | 10                                                   |

|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| 4.1<br>4.2<br>4.3<br>4.4                              | PTD Bit Allocation                                                                                                                                                                           |                                                      |

| A.1<br>A.2<br>A.3<br>A.4<br>A.5<br>A.6<br>A.7         | Format of Setup Data<br>Standard Device Requests<br>Standard Request Codes<br>Descriptor Types<br>Hub Responces to Standard Device Requests<br>Hub Class Requests<br>Hub Class Request Codes | 113<br>114<br>114<br>118<br>118                      |

| B.1<br>B.2<br>B.3<br>B.4<br>B.5<br>B.6<br>B.7         | Device Descriptor Format                                                                                                                                                                     | 124<br>125<br>127<br>128<br>128                      |

| C.3<br>C.4<br>C.5<br>C.6<br>C.7<br>C.8<br>C.9<br>C.10 | HcInterruptStatus RegisterHcInterruptEnable RegisterHcFmInterval RegisterHcFmRemaining Register                                                                                              | 131<br>133<br>135<br>136<br>136<br>137<br>137<br>137 |

|                                                       | 2HcRhStatus Register                                                                                                                                                                         |                                                      |

| C.13HcRhPortStatus(1:2) Register        |

|-----------------------------------------|

| C.14HcHardwareConfiguration Register    |

| C.15HcDMAConfiguration Register         |

| C.16HcTransferCounter Register          |

| $C.17 Hc_{\mu}$ PInterrupt Register     |

| C.18 Hc $\mu$ PInterruptEnable Register |

| C.19HcChipID Register                   |

| C.20HcScratch Register                  |

| C.21 HcSoftwareReset Register           |

| C.22 HcITLBufferLength Register         |

| C.23 HcATLBufferLength Register         |

| C.24HcBufferStatus Register             |

| C.25HcReadBackITLOLength Register       |

| C.26HcReadBackITL1Length Register       |

| C.27 HcITLBufferPort Register           |

| C.28 HcATLBufferPort Register           |

## Acknowledgements

I'd like to thank my supervisor, associate professor Dionisios N. Pnevmatikatos for his guidance and patience in helping me understand my project, and also for encouraging me to keep on going, at a time when all my efforts seemed futile. I'd like to thank all the open-source community, and especially everyone from the "Linux USB Development" mailing list, for their invaluable support and countless discussions; I have gained much from their insight. I'd also like to thank my remaining committee members, professor Apostolos Dollas and assistant professor Vassilis Samoladas for taking the time to read and evaluate this document.

I would like to thank the Microprocessor and Hardware Laboratory (MHL), of the Electronic and Computer Engineering Department, for the full financial assistance provided in acquiring the required hardware. I am grateful to the director of the laboratory Mr. Markos Kimionis, for providing a perfectly equipped laboratory and helping me with the logic analyzer. I'd also like to mention how much I appreciate the altruistic work of countless members of the opensource community, which provided me with invaluable tools for my work (just to name a few: the Debian GNU/Linux distribution, the GNU tools like GCC and Emacs, the GNOME desktop environment, and of course Latex, Ghostscript and Gimp, used in the creation of this paper).

I'd like to let my mother and father know how much I appreciate them for their many years of emotional and financial support.

And finally, I'd like to thank my girlfriend Katerina for all her love, support and encouragement. Without her, this project would have been much more difficult, if not impossible.

#### Abstract

Embedded systems design is a rapidly growing field of Computer Engineering. An embedded device may be built from "common of the self components", or use a custom range of hardware, different from the one found in most desktop computers, or a combination of the above. This fact has led to a growing demand for device drivers that will be able to complement the embedded opearating systems in their task to support the hardware. Very often, existing drivers are ported to the embedded architecture; other drivers are written from scratch.

This thesis is an attempt to understand the workings of a device driver in the Linux operating system, a popular choice among the embedded operating systems, and to apply this knowledge to write a driver for the PCI development board of the Philips ISP1160 Embedded USB Host Controller. The device driver is written for the new 2.6 series of the Linux kernel and can handle the Control, Bulk and Interrupt USB transfer modes, supporting a variety of USB devices, including printers, memory sticks, input devices, digital cameras and modems. The driver demonstrates competitive speed compared to the popular UHCI USB host controllers found in most modern desktop computers, using a smaller memory footprint and a simpler driver model.

## **Chapter 1**

## Introduction

## 1.1 Introduction to Embedded Devices

An embedded device is a special-purpose computer system, which is completely encapsulated by the device it controls. An embedded device has specific requirements and performs pre-defined tasks, unlike a general-purpose personal computer. Examples of embedded devices include:

- Automatic Teller Machines (ATMs)

- Cellular telephones and telephone switches

- Computer network equipment, including routers, timeservers and firewalls

- Computer printers

- Handheld calculators

- Household appliances, including microwave ovens, washing machines, television sets, DVD players/recorders

- Inertial Guidance Systems, flight control hardware/software and other integrated systems in aircraft and missiles

- Medical equipment

- Measurement equipment such as digital storage oscilloscopes, logic analyzers, and spectrum analyzers

- Personal digital assistants (PDAs)

- Videogame consoles

#### 1.1. INTRODUCTION TO EMBEDDED DEVICES

Figure 1.1: Embedded System Architectures Survey

Programs on an embedded system often must run with real-time constraints with limited hardware resources; often there is no disk drive, operating system, keyboard or screen. A flash drive may replace rotating media, and a small keypad and LCD screen may be used instead of a normal keyboard and screen respectively.

#### 1.1.1 Embedded System Platforms

There are many different CPU architectures used in embedded designs. This is in contrast to the desktop computer market, which is limited to just a few competing architectures, mainly the *Intel/AMD x86*, and the *Apple/Motorola/IBM PowerPC*.

Figure 1.1 shows the embedded market trends in CPU architectures<sup>1</sup>.

#### 1.1.2 Embedded Operating Systems

Embedded devices may or may not have an operating system (most modern devices do have one). *Firmware* is the name for software that is embedded in hardware devices, e.g. in one or more ROM/Flash memory IC chips.

Embedded systems are routinely expected to maintain reliability while running continuously for long periods of time, sometimes measured in years. Firmware is usually developed and tested to much stricter requirements than is general purpose software. In addition, due to the fact that the embedded system may be outside the reach of humans, embedded firmware must usually be able to selfrestart even if some sort of catastrophic data corruption has taken

<sup>&</sup>lt;sup>1</sup>Source: 2003 Embedded Market Survey, by LinuxDevices.com [1]

place. This last feature often requires external hardware assistance such as a watchdog timer that can automatically restart the system in the event of a software failure.

Many time-critical applications of embedded systems require a *Real Time Operating System* to control the device.

## **Real-Time Operating Systems**

A Real Time Operating System (RTOS) is an operating system that has been developed for real-time applications. A commonly accepted definition of "real-time" performance is that real-world events must be responded to within a defined, predictable, and relatively short time interval.

Popular RTOSes include:

- BeOS

- OS-9

- OSE

- FreeRTOS

- Nucleus

- Windows CE

- RT Linux

- VxWorks

- LynxOS

### 1.1.3 The Need for Device Drivers

An operating system is of no value without a complete and frequently updated list of device drivers to support the hardware. This is also true for embedded devices.

As mentioned above, an embedded system is designed for a specific task and has special requirements (as compared to a classic desktop computer). During the past few years, the hardware industry has made steps to provide the embedded system designers with tools that fit well with these special needs (e.g., a network interface for the embedded market might not be as fast as a classic one, but it will be able to perform well while consuming less energy).

This special hardware, needs of course device drivers. And although the computer industry is moving towards a unified approach

Figure 1.2: Embedded Linux Distributions

in hardware design by adopting specifications (thus greatly reducing the number of different drivers required), the embedded market has its own rules and specifications. As a result, the need for custom device drivers to support the hardware is always a top priority in embedded systems design.

## 1.1.4 Linux for Embedded Devices

The power, reliability, flexibility, and scalability of Linux, combined with its support for a multitude of microprocessor architectures, hardware devices, graphics support, and communications protocols have established it as an increasingly popular software platform for a vast array of projects and products.

Given that Linux is openly and freely available in source form, many variations and configurations of the operating system and its supporting software components have evolved to meet the diverse needs of the markets and applications to which Linux is being adapted. There are small-footprint versions and real-time enhanced versions. And despite the origins of Linux as a PC architecture operating system, there are now ports to numerous non-x86 CPUs, with and without memory management units, including PowerPC, ARM, MIPS, 68K, and even microcontrollers.

Figure 1.2 shows the Linux distributions that are favored by the

embedded market<sup>2</sup>. We can see that there is a shift towards custombuilt Linux (listed under "home grown"). Since Linux is open-source software, more and more embedded system manufacturers prefer to download the source of the Linux kernel and modify it to fit their needs.

## **1.2 Device Drivers: Basic Principles**

No matter the hardware addressed, every device driver should adhere to certain basic principles.

## 1.2.1 The Role of a Device Driver

Most programming problems can be split into two parts: "what capabilities are to be provided" (the mechanism) and "how those capabilities can be used" (the policy). If the two issues are addressed by different parts of the program, or even by different programs altogether, the software package is easier to develop and to adapt to particular needs.

The role of a device driver is to provide *mechanism*, not *policy*. The driver should deal with making the hardware available, leaving all the issues about *how* to use the hardware to the applications.

Policy-free drivers should have a number of typical characteristics:

- Support both synchronous and asynchronous operation

- Ability to be opened multiple times

- Exploit the full capabilities of the hardware

- Lack of software layers to provide policy-related operations

However, user programs are an integral part of a software package and all drivers should be distributed with configuration files that apply a default behavior to the underlying mechanism.

### 1.2.2 Kernel & User Space

A device driver runs in the so-called *kernel space*, whereas applications run in *user space*.

<sup>&</sup>lt;sup>2</sup>Source: 2003 Embedded Market Survey, by LinuxDevices.com [1]

The role of the operating system is to provide programs with a consistent view of the computer's hardware. In addition, the operating system must account for independent operation of programs and protection against unauthorized access to resources. This is possible if the CPU enforces protection of system software from the applications.

All current processors have at least two protection levels (the x86 family have more). The kernel (and its device drivers) executes in the highest level where everything is allowed, whereas applications execute in the lowest level where the processor regulates direct access to hardware and unauthorized access to memory.

#### **1.2.3 Security Issues**

Security is an increasingly important concern in modern times. It is a problem that can be split in two parts. One security problem is the damage a user can cause through the misuse of existing programs, or by *incidentally* exploiting bugs; a different issue is what kind of misfunctionality a programmer can *deliberately* implement. It is a dangerous to run a program received from somebody else from the administrator account, as it is to give him or her a superuser shell. And since every device driver runs in kernel space, a kernel module is just as powerful as a superuser shell.

When possible, a driver should not encode security policy in its source code. Security is a policy issue that is often best handled at higher levels within the kernel, under the control of the system administrator.

The driver should not include of course security bugs. Many security problems are created by *buffer overrun* errors, when data ends up written beyond the end of an allocated buffer, thus overwriting unrelated data. A few other security ideas include:

- Any input received from user processes should be treated with great suspicion

- Any memory obtained from the kernel should be zeroed or otherwise initialized before being made available to a user process or device.

- If there are specific operations that could affect the system (e.g., formatting a disk), those operations should be restricted to privileged users.

## **1.3 Thesis Summary**

This thesis is an attempt to understand the workings of a device driver in the Linux operating system, a popular choice among the embedded operating systems, and to apply this knowledge to write a driver for the PCI development board of the *Philips ISP1160 Embedded USB Host Controller*. The PCI board was connected to a typical PC x86 32 bit system (AMD Duron), running Debian GNU/Linux, Testing (Sarge).

Although when the project first started, the best choice in Linux kernels was the 2.4 series, a few months later the 2.6 series appeared, which among many other changes, incorporates a very different (and much better) scheme in supporting *hotplug* devices (such as a USB device). Thus, even though the documentation for the 2.6 series was very sparse, it was chosen as the kernel to develop the driver for.

The PCI development board of the ISP1160 ships with a driver for the DOS operating system but lacks a Linux device driver (altough there exists a Linux driver for the ISA version of the board). The drivers shipped with the board (both PCI and ISA) are far from complete, as they only intend to demonstrate some of the capabilities of the host controller. Using the supplied software, the user can monitor the USB downstream ports for changes (e.g. connection of a USB device), get information about the connected devices by reading their descriptors, check the contents of the buffer RAM of the host controller, and try a USB mouse.

## **1.3.1** Thesis Goals

This driver is an attempt to illustrate the way that a device driver can be written (focusing in the API of Linux kernel 2.6). A set of goals was introduced from the beginning of the development. According to these goals, the driver should:

- 1. be written using the new API of Linux kernel 2.6

- 2. integrate with the operating system, making the USB host controller available and functional, just like any other device driver present on the system (especially any USB host controller driver)

- 3. separate all PCI-specific code from the rest of the source, to ease porting of the driver to non-PCI implementations

- 4. be fully modular

- 5. be as policy-free as possible

- 6. support at least the *Control* and *Bulk* USB transfer modes, and if possible the *Interrupt* and *Isochronous* transfer modes. (see Section 2.3.1, on page 16)

- 7. be as secure as possible

- 8. support the PIO mode of operation, and if possible the DMA mode as well.

- 9. Emphasize in aspects of speed, to demonstrate the importance of a driver in overall system performance

Note however that this driver is not supposed to be a "commercialgrade" software product. As such, some features of a complete device driver might be missing.

### **1.3.2 Thesis Results**

The resulting work of the thesis is a functional driver module for the PCI development board of the IS1160 host controller, which fully integrates with the operating system. Users are able to insert and remove the module from the running kernel, and the host controller is able to coexist with other possibly present USB host controllers, providing the same functionality through standard user-space programs.

The work follows the "separation of policy from mechanism" model presented in Section 1.2.1. The driver makes the hardware available by taking advantage of the API provided by the kernel. This way the kernel registers the host controller with the operating system in a transparent way, leaving all issues of using the hardware to applications. This ensures an adequate level of security, since the driver does not attempt to encode its own security policy, leaving all such matters to the operating system. The Linux OS already includes a strict set of security measures related with the insertion and removal of modules. All input from user space applications is passed to the USBD kernel driver of the Linux USB subsystem, which forwards the request to the correct host controller driver. This way, the driver is able to trust all incoming data, since any user input is first filtered with the security mechanisms of the USB subsystem.

The supported hardware functionality includes Control, Bulk and Interrupt transfer modes, leaving only the Isochronous mode out of the list. This allows the majority of available USB devices to be connected to the host controller. Access to the internal registers and buffer RAM of the host controller is accomplished through PIO operations. DMA access to the buffer RAM was not implemented.

The source code separates the initialization sequence from the actual programming of the ISP1160, allowing the driver to be easily modified to support other implementations of the ISP1160 as well. Such implementations need only to alter the way that the hardware resources are made available, by modifying the files that contain the PCI initialization code.

This driver has been tested and works with a custom-built 2.6.10 version of the Linux kernel. A detailed explanation of the results can be found in Section 5.4, on page 93.

## 1.3.3 Thesis Outline

This document is divided in two parts. The first part (Chapters 2-4) is dedicated to the theoritical knowledge required to understand to second part (Chapter 5), where we analyze the task of writing the actual driver for the ISP1160. The first part begins with an overview of the USB Bus specifications (Chapter 2), followed by a presentation of the Linux USB subsystem (Chapter 3) and the way that it implements the USB standards. Then, we present an architectural and functional overview of the ISP1160 (Chapter 4), focusing on the parts that are important to the device driver. At the end of Chapter 4, we examine the PCI development board that was used. The second part is the presentation of the device driver. Throughout this chapter we examine parts of the source code and explain the key elements of the driver. This is no substitute for the actual source code, and for a full explanation of the way that this driver works, refer to the manual of the source code, available in HTML and PDF format. At the end of the second part, we evaluate the perforance of ther driver and, based on the goals that were set for the thesis, comment on the results. The last part (Chapter 6) contains the conclusions and possible further work on the subject.

## Chapter 2

## **The Universal Serial Bus**

This chapter presents a brief description of the background, architecture and operation of the Universal Serial Bus (USB). This is not a full description of the bus specifications. For more information see (5)

## 2.1 Background

Universal Serial Bus was created when a group of 7 companies: *Compaq, Digital Equipment, IBM, Intel, Microsoft* and *Northern Telecom* decided to form a specifications to merge legacy connectivity such as RS232, Printer port, PS2 port into a single common connector to the Personal Computer.

USB version 1.1 was released on 15 January 1996 and supported two speeds, a full speed mode of 12 Mbits/s and a low speed mode of 1.5 Mbits/s. The 1.5 Mbits/s mode is slower and less susceptible to EMI, thus reducing the cost of ferrite beads and quality components. For example, crystals can be replaced by cheaper resonators. USB 2.0, released on 27 April 2000, supports speeds up to 480 Mbits/s. Table 2.1 summarizes the available speeds.

Table 2.1: USB supported speeds

| High Speed | 480.0 Mbits/s |

|------------|---------------|

| Full Speed | 12.0 Mbits/s  |

| Low Speed  | 1.5 Mbits/s   |

## 2.1.1 Goals for the Universal Serial Bus

The USB is specified to be an industry-standard extension to the PC architecture with a focus on PC peripherals that enable consumer and business applications. The following criteria were applied in defining the architecture for the USB:

- 1. Ease-of-use for PC peripheral expansion

- 2. Low-cost solution that supports transfer rates up to 480 Mb/s

- 3. Full support for real-time data for voice, audio, and video

- 4. Protocol flexibility for mixed-mode isochronous data transfers and asynchronous messaging

- 5. Integration in commodity device technology

- 6. Comprehension of various PC configurations and form factors

- 7. Provision of a standard interface capable of quick diffusion into product

- 8. Enabling new classes of devices that augment the PC's capability

- 9. Full backward compatibility of USB 2.0 for devices built to previous versions of the specification

## 2.1.2 USB Features

The USB Specification provides a selection of attributes that can achieve multiple price/performance integration points and can enable functions that allow differentiation at the system and component level.

Features are categorized by the following benefits:

- 1. Easy to use for end user

- Single model for cabling and connectors

- Electrical details isolated from end user (e.g., bus terminations)

- Self-identifying peripherals, automatic mapping of function to driver and configuration

- Dynamically attachable and reconfigurable peripherals

- 2. Wide range of workloads and applications

- Suitable for a broad spectrum of bandwidths

- Supports isochronous as well as asynchronous transfer types over the same set of wires

- Supports concurrent operation of many devices (multiple connections)

- Supports up to 127 physical devices

- Supports transfer of multiple data and message streams between the host and devices

- Allows compound devices (i.e., peripherals composed of many functions)

- Lower protocol overhead, resulting in high bus utilization

- 3. Isochronous bandwidth

- Guaranteed bandwidth and low latencies appropriate for telephony, audio, video, etc.

- 4. Flexibility

- Supports a wide range of packet sizes, which allows a range of device buffering options

- Allows a wide range of device data rates by accommodating packet buffer size and latencies

- Flow control for buffer handling is built into the protocol

- 5. Robustness

- Error handling/fault recovery mechanism is built into the protocol

- Dynamic insertion and removal of devices is identified in user-perceived real-time

- . Supports identification of faulty devices

- 6. Synergy with PC industry

- Protocol is simple to implement and integrate

- Consistent with the PC plug-and-play architecture

- Leverages existing operating system interfaces

- 7. Low-cost implementation

- Low-cost subchannel at 1.5 Mb/s

- Optimized for integration in peripheral and host hardware

- Suitable for development of low-cost peripherals

- Low-cost cables and connectors

- Uses commodity technologies

- 8. Upgrade path

- Architecture upgradeable to support multiple USB Host Controllers in a system

## 2.2 Architectural Overview

USB is a cable bus that supports data exchange between a host computer and a wide range of simultaneously accessible peripherals. The attached peripherals share USB bandwidth through a hostscheduled, token-based protocol. The bus allows peripherals to be attached, configured, used, and detached while the host and other peripherals are in operation.

## 2.2.1 USB Topology

The USB connects USB devices with the USB host. The USB physical interconnect is a tiered star topology. A hub is at the center of each star. Each wire segment is a point-to-point connection between the host and a hub or function, or a hub connected to another hub or function (for more inormation on hubs or functions, refer to 2.4.1 and 2.4.2). Figure 2.1 illustrates the topology of the USB.

Due to timing constraints allowed for hub and cable propagation times, the maximum number of tiers allowed is seven (including the root tier). In seven tiers, a maximum of five non-root hubs can be supported in a communication path between the host and any device. A compound device (see Figure 2.1) occupies two tiers; therefore, it cannot be enabled if attached at tier level seven. Only functions can be enabled in tier seven.

## 2.2.2 USB Hosts

The Universal Serial Bus is host controlled. There can only be one host per bus. The specification in itself, does not support any form of multimaster arrangement. However the On-The-Go specification, which is an addition to USB 2.0, has introduced a Host Negotiation Protocol which allows two devices to negotiate for the role of host. This is aimed at and limited to single point-to-point connections such as a mobile phone and personal organizer and not multiple hub, multiple

Figure 2.1: Topology of the USB Bus

device desktop configurations. The USB host is responsible for undertaking all transactions and scheduling bandwidth. Data can be sent by various transaction methods using a token-based protocol.

#### **USB Host Specifications**

The USB host controllers have their own specifications. With USB 1.1, there were two Host Controller Interface Specifications, *UHCI* (Universal Host Controller Interface) developed by *Intel* which puts more of the burden on software and allowing for cheaper hardware and the *OHCI* (Open Host Controller Interface) developed by *Compaq*, *Microsoft* and *National Semiconductor* which places more of the burden on hardware and makes for simpler software. With the introduction of USB 2.0 a new Host Controller Interface Specification was needed to describe the register level details specific to USB 2.0. The *EHCI* (Enhanced Host Controller Interface) was born. Significant contributors include *Intel, Compaq, NEC, Lucent* and *Microsoft*.

#### 2.2.3 Dynamic Device Attachment

The USB supports USB devices attaching to and detaching from the USB at any time. Consequently, system software must accommodate dynamic changes in the physical bus topology.

### **Attachment of USB Devices**

All USB devices attach to the USB through ports on specialized USB devices known as hubs (refer to 2.4.1, on page 18). Hubs have status bits that are used to report the attachment or removal of a USB device on one of its ports. The host queries the hub to retrieve these bits. In the case of an attachment, the host enables the port and addresses the USB device through the device's control pipe at the default address (pipes are explained in 2.4.4, on page 21). The host assigns a unique USB address to the device and then determines if the newly attached USB device is a hub or a function. The host establishes its end of the control pipe for the USB device using the assigned USB address and endpoint number zero. If the attached USB device is a hub and USB devices are attached to its ports, then the above procedure is followed for each of the attached USB devices. If the attached USB device is a function, then attachment notifications will be handled by host software that is appropriate for the function.

#### **Removal of USB Devices**

When a USB device has been removed from one of a hub's ports, the hub disables the port and provides an indication of device removal to the host. The removal indication is then handled by appropriate USB System Software. If the removed USB device is a hub, the USB System Software must handle the removal of both the hub and of all of the USB devices that were previously attached to the system through the hub.

#### **Bus Enumeration**

Bus enumeration is the activity that identifies and assigns unique addresses to devices attached to a bus. Because the USB allows USB devices to attach to or detach from the USB at any time, bus enumeration is an on-going activity for the USB System Software. Additionally, bus enumeration for the USB also includes the detection and processing of removals (More information on the enumeration process can be found in section 2.7.8, on page 32).

## 2.3 USB Data Flow Modes

The USB supports functional data and control exchange between the USB host and a USB device as a set of either unidirectional or bidirectional pipes (refer to 2.4.4, on page 21). USB data transfers take place between host software and a particular endpoint on a USB device. Such associations between the host software and a USB device endpoint are called pipes. In general, data movement though one pipe is independent from the data flow in any other pipe. A given USB device may have many pipes.

### 2.3.1 Transfer Modes

The USB architecture comprehends four basic types of data transfers:

- *Control Transfers:* Used to configure a device at attach time and can be used for other device-specific purposes, including control of other pipes on the device.

- *Bulk Data Transfers:* Generated or consumed in relatively large and bursty quantities and have wide dynamic latitude in transmission constraints.

- Interrupt Data Transfers: Used for timely but reliable delivery of data, for example, characters or coordinates with human-perceptible echo or feedback response characteristics.

- *Isochronous Data Transfers* Occupy a prenegotiated amount of USB bandwidth with a prenegotiated delivery latency.

A pipe supports only one of the types of transfers described above for any given device configuration.

## **Control Transfers**

Control data is used by the USB System Software to configure devices when they are first attached. Other driver software can choose to use control transfers in implementation-specific ways. Data delivery is lossless.

The USB device framework (refer to Section 2.4) defines standard, device class, or vendor-specific requests that can be used to manipulate a device's state. Descriptors are also defined that can be used to contain different information on the device. Control transfers provide the transport mechanism to access device descriptors and make requests of a device to manipulate its behavior.

### **Bulk Transfers**

Bulk data typically consists of larger amounts of data, such as that used for printers or scanners. Bulk data is sequential. Reliable exchange of data is ensured at the hardware level by using error detection in hardware and invoking a limited number of retries in hardware. Also, the bandwidth taken up by bulk data can vary, depending on other bus activities.

#### **Interrupt Transfers**

A limited-latency transfer to or from a device is referred to as interrupt data. Such data may be presented for transfer by a device at any time and is delivered by the USB at a rate no slower than is specified by the device.

Interrupt data typically consists of event notification, characters, or coordinates that are organized as one or more bytes. An example of interrupt data is the coordinates from a pointing device. Although an explicit timing rate is not required, interactive data may have response time bounds that the USB must support.

#### **Isochronous Transfers**

Isochronous data is continuous and real-time in creation, delivery, and consumption. Timing-related information is implied by the steady rate at which isochronous data is received and transferred. Isochronous data must be delivered at the rate received to maintain its timing. In addition to delivery rate, isochronous data may also be sensitive to delivery delays. For isochronous pipes, the bandwidth required is typically based upon the sampling characteristics of the associated function. The latency required is related to the buffering available at each endpoint.

A typical example of isochronous data is voice. If the delivery rate of these data streams is not maintained, dropouts in the data stream will occur due to buffer or frame underruns or overruns. Even if data is delivered at the appropriate rate by USB hardware, delivery delays introduced by software may degrade applications requiring real-time turnaround, such as telephony-based audio conferencing.

The timely delivery of isochronous data is ensured at the expense of potential transient losses in the data stream. In other words, any error in electrical transmission is not corrected by hardware mechanisms such as retries. USB isochronous data streams are allocated a dedicated portion of USB bandwidth to ensure that data can be delivered at the desired rate.

Figure 2.2: A Typical USB Hub

## 2.4 USB Device Framework

USB devices are divided into device classes such as hub, human interface, printer, imaging, or mass storage device. The hub device class indicates a specially designated USB device that provides additional USB attachment points. USB devices are required to carry information for self-identification and generic configuration. They are also required at all times to display behavior consistent with defined USB device states.

Two major divisions of device classes exist: hubs and functions. Only hubs have the ability to provide additional USB attachment points. Functions provide additional capabilities to the host.

### 2.4.1 USB Hubs

Hubs are a key element in the plug-and-play architecture of the USB. Figure 2.2 shows a typical hub. Hubs serve to simplify USB connectivity from the user's perspective and provide robustness at relatively low cost and complexity.

Hubs are wiring concentrators and enable the multiple attachment characteristics of the USB. Attachment points are referred to as ports. Each hub converts a single attachment point into multiple attachment points. The architecture supports concatenation of multiple hubs (see also 2.7, on page 28, for details on the root hub).

The upstream port of a hub connects the hub towards the host. Each of the downstream ports of a hub allows connection to another hub or function. Hubs can detect attach and detach at each downstream port and enable the distribution of power to downstream devices. Each downstream port can be individually enabled and attached to either high-, full- or low-speed devices.

Figure 2.3 illustrates how hubs provide connectivity in a typical desktop computer environment.

Figure 2.3: Hubs in a Desktop Computer Environment

## 2.4.2 USB Functions

A function is a USB device that is able to transmit or receive data or control information over the bus. A function is typically implemented as a separate peripheral device with a cable that plugs into a port on a hub. However, a physical package may implement multiple functions and an embedded hub with a single USB cable. This is known as a compound device. A compound device appears to the host as a hub with one or more nonremovable USB devices (see Figure 2.1, on page 14).

Each function contains configuration information that describes its capabilities and resource requirements. Before a function can be used, it must be configured by the host. This configuration includes allocating USB bandwidth and selecting function-specific configuration options. Examples of functions include the following:

- A human interface device such as a mouse, keyboard, tablet, or game controller

- An imaging device such as a scanner, printer, or camera

- A mass storage device such as a CDROM drive, floppy drive, or DVD drive

Most functions have a series of buffers, typically 8 bytes long. Each buffer belongs to an endpoint.

#### 2.4. USB DEVICE FRAMEWORK

## 2.4.3 USB Device Endpoints

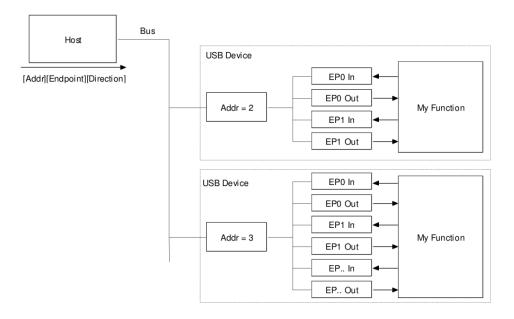

An endpoint is a uniquely identifiable portion of a USB device that is the terminus of a communication flow between the host and device. Each USB logical device is composed of a collection of independent endpoints. Each logical device has a unique address assigned by the system at device attachment time. Each endpoint on a device is given at design time a unique device-determined identifier called the endpoint number. Each endpoint has a device-determined direction of data flow. As illustrated in Figure 2.4, the combination of the device address, endpoint number, and direction allows each endpoint to be uniquely referenced. Each endpoint is a simplex connection that supports data flow in one direction: either input (from device to host) or output (from host to device).

An endpoint has characteristics that determine the type of transfer service required between the endpoint and the client software. An endpoint describes itself by:

- Bus access frequency/latency requirement

- Bandwidth requirement

- Endpoint number

- Error handling behavior requirements

- Maximum packet size that the endpoint is capable of sending or receiving

- The transfer type for the endpoint (refer to Section 2.3.1, on page 16 for details)

- The direction in which data is transferred between the endpoint and the host

All devices must support endpoint zero. This is the endpoint which receives all of the devices control and status requests during enumeration and throughout the duration while the device is operational on the bus. Endpoints other than those with endpoint number zero are in an unknown state before being configured and may not be accessed by the host before being configured.

## 2.4.4 USB Pipes

While the device sends and receives data on a series of endpoints, the client software transfers data through pipes. A pipe is a logical connection between the host and endpoint(s). Pipes also have a set of parameters associated with them such as how much bandwidth is allocated to it, what transfer type (Control, Bulk, Iso or Interrupt) it uses, a direction of data flow and maximum packet/buffer sizes. For example the default pipe is a bidirectional pipe made up of endpoint zero in and endpoint zero out with a control transfer type.

USB defines two types of pipes:

- Stream Pipes: have no defined USB format. Data flows sequentially and has a predefined direction, either in or out. Stream pipes support bulk, isochronous and interrupt transfer types. Stream pipes can either be controlled by the host or device.

- *Message Pipes*: have a defined USB format. They are host controlled. Data is transferred in the desired direction, dictated by the request. Message pipes allow data to flow in both directions but only support control transfers.

All USB devices respond to requests from the host on the device's Default Control Pipe. These requests are made using control transfers. The USB protocol specifies a standard set of requests that all devices must support. More information on USB standard requests can be found in Appendix A.1, on page 110.

## **2.5 USB Descriptors**

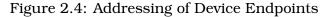

All USB devices have a hierarchy of descriptors which describe to the host information such as what the device is, who makes it, what version of USB it supports, how many ways it can be configured, the number of endpoints and their types etc.

The more common USB descriptors are:

- Device Descriptors

- Configuration Descriptors

- Interface Descriptors

- Endpoint Descriptors

- String Descriptors

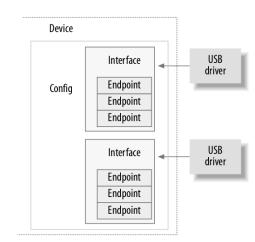

The hierarchy of the descriptors is illustrated in Figure 2.5.

USB devices can only have one **device descriptor**. The device descriptor includes information such as what USB revision the device complies to, the Product and Vendor IDs used to load the appropriate drivers and the number of possible configurations the device can have. The number of configurations (*bNumConfigurations* in Figure 2.5) indicates how many configuration descriptors branches are to follow.

The **configuration descriptor** specifies values such as the amount of power this particular configuration uses, if the device is self- or buspowered and the number of interfaces it has (*bNumInterfaces* in Figure 2.5). When a device is enumerated, the host reads the device descriptors and can make a decision of which configuration to enable. It can only enable one configuration at a time.

The configuration settings are not limited to power differences. Each configuration could be powered in the same way and draw the same current, yet have different interface or endpoint combinations. However it should be noted that changing the configuration requires all activity on each endpoint to stop. While USB offers this flexibility, very few devices have more than 1 configuration.

The **interface descriptor** can be seen as a header or grouping of the endpoints into a functional group performing a single feature of a multi-function device. Unlike the configuration descriptor, there is no limitation as to having only one interface enabled at a time.

Each **endpoint descriptor** is used to specify the type of transfer, direction, polling interval and maximum packet size for each endpoint. Endpoint zero, the default control endpoint is always assumed to be a control endpoint and as such never has a descriptor.

## 2.5.1 Composition of USB Descriptors

All descriptors are made up of a common format. The first byte specifies the length of the descriptor, while the second byte indicates the descriptor type. If the length of a descriptor is smaller than what the specification defines, then the host shall ignore it. However if the size is greater than expected the host will ignore the extra bytes and start looking for the next descriptor at the end of actual length returned.

For more information on the composition of USB Descriptors, refer to Appendix B, on page 121.

## 2.6 USB Host: Hardware & Software

The USB interconnect supports data traffic between a host and a USB device. The specifications of the bus, describe the host interfaces necessary to facilitate USB communication between a software client, resident on the host, and a function implemented on a device.

### 2.6.1 Host Controller Requirements

In all implementations, Host Controllers perform the same basic duties with regard to the USB and its attached devices. The Host Controller has requirements from both the host and the USB. The following is a brief overview of the functionality provided:

- State Handling As a component of the host, the Host Controller reports and manages its states.

- Serializer/Deserializer For data transmitted from the host, the Host Controller converts protocol and data information from its native format to a bit stream transmitted on the USB. For data being received into the host, the reverse operation is performed.

- (micro)Frame Generation The HC produces "Start of Frame" (SOF) tokens at a period of 1 ms when operating with full-speed devices, and at a period of 125  $\mu$ s when operating with high-speed devices.

- Data Processing The Host Controller processes requests for data transmission to and from the host.

- *Protocol Engine* The Host Controller supports the protocol specified by the USB.

- *Transmission Error Handling* All Host Controllers exhibit the same behavior when detecting and reacting to the defined error categories.

- *Remote Wakeup* All Host Controllers must have the ability to place the bus into the Suspended state and to respond to bus wakeup events.

- *Root Hub* The root hub provides standard hub function to link the Host Controller to one or more USB ports.

- Host System Interface Provides a high-speed data path between the Host Controller and host system.

## 2.6.2 Overview of the USB Host

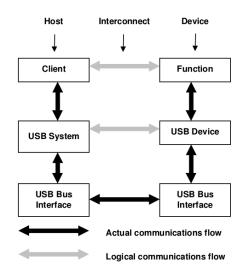

The host and the device are divided into the distinct layers depicted in Figure 2.6. Vertical arrows indicate the actual communication on the host. All communications between the host and device ultimately occur on the physical USB wire. However, there are logical host-device interfaces between each horizontal layer. These communications, between client software resident on the host and the function provided by the device, are typified by a contract based on the needs of the application currently using the device and the capabilities provided by the device. This client-function interaction creates the requirements for all of the underlying layers and their interfaces.

In summary, the host layers provide the following capabilities:

Figure 2.6: USB Interlayer Communication Model

- Detecting the attachment and removal of USB devices

- Managing USB standard control flow between the host and USB devices

- Managing data flow between the host and USB devices

- Collecting status and activity statistics

- Controlling the electrical interface between the Host Controller and USB devices, including the provision of a limited amount of power.

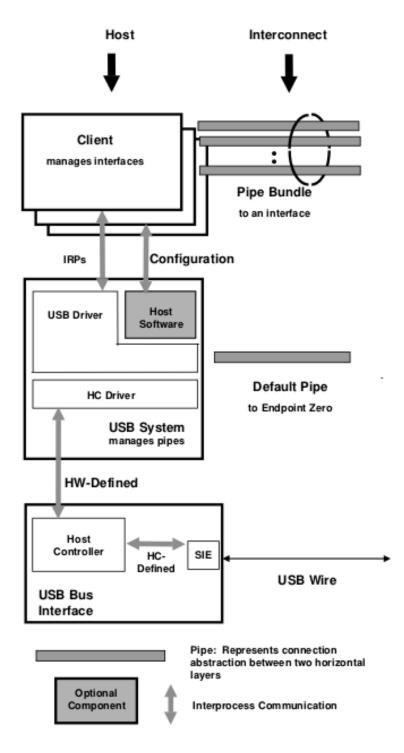

Figure 2.7 illustrates the host's view of its communication with the device. There is only one host for each USB. The major layers of a host consist of the following:

- USB bus interface

- USB System

- Client

### 2.6.3 USB Bus Interface

The USB bus interface handles interactions for the electrical and protocol layers. From the interconnect point of view, a similar USB bus interface is provided by both the USB device and the host, as exemplified by the Serial Interface Engine (SIE). On the host, however,

Figure 2.7: USB Host Communications

the USB bus interface has additional responsibilities due to the unique role of the host on the USB and is implemented as the Host Controller. The Host Controller has an integrated root hub providing attachment points to the USB wire.

## 2.6.4 USB System

The USB System uses the Host Controller to manage data transfers between the host and USB devices. The interface between the USB System and the Host Controller is dependent on the hardware definition of the Host Controller. The USB System, along with the Host Controller, performs the translation between the client's view of data transfers and the USB transactions appearing on the interconnect. This includes the addition of any USB feature support such as protocol wrappers. The USB System is also responsible for managing USB resources, such as bandwidth and bus power, so that client access to the USB is possible.

The USB System has three basic components:

- Host Controller Driver

- USB Driver

- Host Software

## 2.6.5 Host Controller Driver

The Host Controller Driver (HCD) is an abstraction of Host Controller hardware and the Host Controller's view of data transmission over the USB. The HCD meets the following requirements:

- Provides an abstraction of the Host Controller hardware.

- Provides an abstraction for data transfers by the Host Controller across the USB interconnect.

- Provides an abstraction for the allocation (and de-allocation) of Host Controller resources to support guaranteed service to USB devices.

- Presents the root hub and its behavior according to the hub class definition. This includes supporting the root hub such that the hub driver interacts with the root hub exactly as it would for any hub.

The HCD provides a software interface (HCDI) that implements the required abstractions. The function of the HCD is to provide an abstraction, which hides the details of the Host Controller hardware. Below the Host Controller hardware is the physical USB and all the attached USB devices.

The HCD is the lowest tier in the USB software stack. The HCD has only one client: the Universal Serial Bus Driver (USBD). The USBD maps requests from many clients to the appropriate HCD. A given HCD may manage many Host Controllers. The HCDI is not directly accessible from a client.

#### 2.6.6 USB Driver

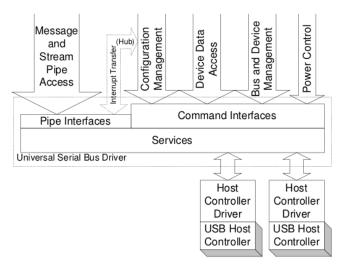

The USBD provides a collection of mechanisms that operating system components, typically device drivers, use to access USB devices. The only access to a USB device is that provided by the USBD. The USBD implementations are operating system-specific. The mechanisms provided by the USBD are implemented, using as appropriate and augmenting as necessary, the mechanisms provided by the operating system. For specifics of the USBD operation in the Linux operating system, see Chapter 3.

USBD directs accesses to one or more HCDs that in turn connect to one or more Host Controllers. If allowed, how USBD instancing is managed is dependent upon the operating system environment. However, from the client's point of view, the USBD with which the client communicates manages all of the attached USB devices. Figure 2.8 presents an overview of the USBD structure.

Clients of USBD direct commands to devices or move streams of data to or from pipes. The USBD presents two groups of software mechanisms to clients:

- *Command mechanisms* allow clients to configure and control USBD operation as well as to configure and generically control a USB device. In particular, command mechanisms provide all access to the device's default pipe.

- *Pipe mechanisms* allow a USBD client to manage device specific data and control transfers. Pipe mechanisms do not allow a client to directly address the device's default pipe.

## 2.7 The Root Hub

Hubs provide the electrical interface between USB devices and the host. Hubs are directly responsible for supporting many of the at-

Figure 10-5. Universal Serial Bus Driver Structure

tributes that make USB user friendly and hide its complexity from the user. Listed below are the major aspects of USB functionality that hubs must support:

- Connectivity behavior

- Power management

- Device connect/disconnect detection

- Bus fault detection and recovery

- High, full, and lowspeed device support

#### 2.7.1 Hub Requests & Descriptors

Hubs respond to standard device commands as defined in A.3.1, on page 118. In addition, the hub class defines a set of hub-specific requests, listed in Section A.3.2, on page 118.

Likewise, hub descriptors are derived from the general USB framework (refer to Appendix B, on page 121). Hub descriptors define a hub device and the ports on that hub. The hub class defines a hubspecific descriptor, listed in Section B.6, on page 128.

#### 2.7.2 Hub Architecture & Supported Speeds

A hub consists of a Hub Repeater section, a Hub Controller section, and a Transaction Translator section. The hub must operate at highspeed when its upstream facing port is connected at high-speed. The hub must operate at full-speed when its upstream facing port is connected at full-speed. The Hub Repeater is responsible for managing connectivity between upstream and downstream facing ports which are operating at the same speed. The Hub Repeater supports full-/low-speed connectivity and high-speed connectivity. The Hub Controller provides status and control and permits host access to the hub. The Transaction Translator takes high-speed split transactions and translates them to full-/low-speed transactions when the hub is operating at high-speed and has full-/low-speed devices attached. The operating speed of a device attached on a downstream facing port determines whether the Routing Logic connects a port to the Transaction Translator or hub repeater sections (see also Table 2.1, on page 10).

#### 2.7.3 Hub Connectivity

Hubs exhibit different connectivity behavior depending on whether they are propagating packet traffic, or resume signaling, or are in the Idle state.

The Hub Repeater contains one port that must always connect in the upstream direction (referred to as the upstream facing port) and one or more downstream facing ports. Upstream connectivity is defined as being towards the host, and downstream connectivity is defined as being towards a device (see also Figure 2.2, on page 18).

If a downstream facing port is enabled (i.e., in a state where it can propagate signaling through the hub), and the hub detects the start of a packet on that port, connectivity is established in an upstream direction to the upstream facing port of that hub, but not to any other downstream facing ports. This means that when a device or a hub transmits a packet upstream, only those hubs in line between the transmitting device and the host will see the packet.

In the downstream direction, hubs operate in a broadcast mode. When a hub detects the start of a packet on its upstream facing port, it establishes connectivity to all enabled downstream facing ports. If a port is not enabled, it does not propagate packet signaling downstream.

#### 2.7.4 Endpoint Organization

The Hub Class defines one additional endpoint beyond Default Control Pipe, which is required for all hubs: the *Status Change endpoint*. The host system receives port and hub status change notifications through the Status Change endpoint. The Status Change endpoint is an interrupt endpoint. If no hub or port status change bits are set, then the hub returns an NAK when the Status Change endpoint is polled. When a status change bit is set, the hub responds with data, as shown in 2.7.6, indicating the entity (hub or port) with a change bit set. The USB System Software can use this data to determine which status registers to access in order to determine the exact cause of the status change interrupt.

#### 2.7.5 Port Change Information Processing

Hubs report a port's status through port commands on a per-port basis. The USB System Software acknowledges a port change by clearing the change state corresponding to the status change reported by the hub. The acknowledgment clears the change state for that port so future data transfers to the Status Change endpoint do not report the previous event. This allows the process to repeat for further changes.

#### 2.7.6 Hub and Port Status Change Bitmap

The Hub and Port Status Change Bitmap indicates whether the hub or a port has experienced a status change. This bitmap also indicates which port(s) has had a change in status. The hub returns this value on the Status Change endpoint. Hubs report this value in byteincrements. That is, if a hub has six ports, it returns a byte quantity, and reports a zero in the invalid port number field locations.

The USB System Software is aware of the number of ports on a hub (this is reported in the hub descriptor) and decodes the Hub and Port Status Change Bitmap accordingly. The hub reports any changes in hub status in bit zero of the Hub and Port Status Change Bitmap.

The Hub and Port Status Change Bitmap size varies from a minimum size of one byte. Hubs report only as many bits as there are ports on the hub, subject to the byte-granularity requirement (i.e., round up to the nearest byte).

Any time the Status Change endpoint is polled by the host controller and any of the Status Changed bits are non-zero, the Hub and Port Status Change Bitmap is returned.

#### 2.7.7 Over-current Reporting and Recovery

USB devices must be designed to meet applicable safety standards. Usually, this will mean that a self-powered hub implements current limiting on its downstream facing ports. If an over-current condition occurs, it causes a status and state change in one or more ports. This change is reported to the USB System Software so that it can take corrective action.

A hub may be designed to report over-current as either a port or a hub event. The hub descriptor field wHubCharacteristics (refer to B.6.1, on page 129) is used to indicate the reporting capabilities of a particular hub. The over-current status bit in the hub or port status field indicates the state of the over-current detection when the status is returned. The over-current status change bit in the Hub or Port Change field indicates if the overcurrent status has changed.

When a hub experiences an over-current condition, it must place all affected ports in the Powered-off state. If a hub has per-port power switching and per-port current limiting, an over-current on one port may still cause the power on another port to fall below specified minimums. In this case, the affected port is placed in the Poweredoff state. If the hub has over-current detection on a hub basis, then an over-current condition on the hub will cause all ports to enter the Powered-off state.

#### 2.7.8 Enumeration Handling

The hub device class commands (refer to Appedix A.3.2, on page 118) are used to manipulate its downstream facing port state. When a device is attached, the device attach event is detected by the hub and reported on the status change interrupt. The host will accept the status change report and request a SetPortFeature(PORT\_RESET) on the port. As part of the bus reset sequence, a speed detect is performed by the hub's port hardware.

When the device is detached from the port, the port reports the status change through the status change endpoint and the port will be reconnected to the high-speed repeater. Then the process is ready to be repeated on the next device attach detect.

## **Chapter 3**

## The Linux USB Subsystem

The development of the Linux USB subsystem started in 1997 and in the meantime it was redesigned many times. This implied various changes of its internal structure and its API too. So it is hard for device driver developers to keep up to date with all ongoing discussions and current changes.

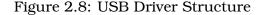

Inside the Linux kernel, there exists a subsystem called "The USB Core" with a specific API to support USB devices and host controllers. Its purpose is to abstract all hardware or device dependent parts by defining a set of data structures, macros and functions. In fact, the USB core is the implementation of the USBD component of a USB system, as described in the USB specifications (refer to 2.6.6, on page 28).

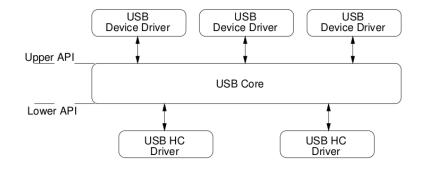

The USB core contains routines common to all USB device drivers and host controller drivers. These functions can be grouped into an upper (Host-Side) and a lower (Host Controller) API layer. As shown in Figure 3.1 there exists an API for USB device drivers and another one for host controllers.

This Chapter begins by introducing some of the standard data

Figure 3.1: Linux USB Core API Layers

types provided by the USB subsystem that conform to the USB specifications. Then the API model of the upper layer is examined, in terms of data structures and functions. The description of the lower layer forms the last part of this chapter. The lower layer is the most important aspect of the USB subsystem in the scope of this work.

## 3.1 USB-Standard Types

This section describes USB structures that are needed for USB device APIs. These are used by the USB device model, which is defined in chapter 9 of the USB 2.0 specification. Linux has several APIs in C that need these.

Note that the naming scheme followed inside these data structures does not conform to the standard Linux kernel scheme, but matches the one found in the USB specifications.

## 3.1.1 Control Request Support

#### struct usb\_ctrlrequest

This structure is used to send control requests on a USB device. It matches the different fields of the USB 2.0 Spec. Refer to Table A.1 for a description of the different fields, and what they are used for.

```

struct usb_ctrlrequest {

___u8 bRequestType;

__u8 bRequest;

__le16 wValue;

__le16 wIndex;

__le16 wLength;

} __attribute__ ((packed));

```

### 3.1.2 Standard Descriptors

These are the standard USB Descriptors, defined in 2.5, as returned by the "GET\_DESCRIPTOR" command.

Two fields inside these data structures, "bLength" and "bDescriptorType", are common to all descriptors. The other fields are specific to each descriptor.

All multi-byte values here are encoded in little endian byte order on the physical bus. But when exposed through Linux-USB APIs, they've been converted to cpu byte order.

#### struct usb\_device\_descriptor

This structure is used to hold a USB device descriptor.

| struct | struct usb_device_descriptor {<br>u8 bLength; |                     |  |

|--------|-----------------------------------------------|---------------------|--|

|        |                                               | bDescriptorType;    |  |

|        | u16                                           | bcdUSB;             |  |

|        | u8                                            | bDeviceClass;       |  |

|        | u8                                            | bDeviceSubClass;    |  |

|        | u8                                            | bDeviceProtocol;    |  |

|        | u8                                            | bMaxPacketSize0;    |  |

|        | u16                                           | idVendor;           |  |

|        | u16                                           | idProduct;          |  |

|        | u16                                           | bcdDevice;          |  |

|        | u8                                            | iManufacturer;      |  |

|        | u8                                            | iProduct;           |  |

|        | u8                                            | iSerialNumber;      |  |

|        | u8                                            | bNumConfigurations; |  |

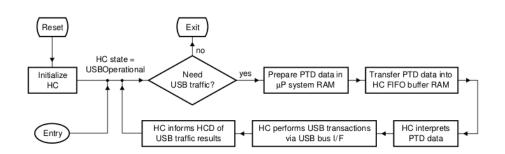

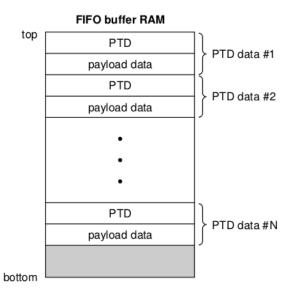

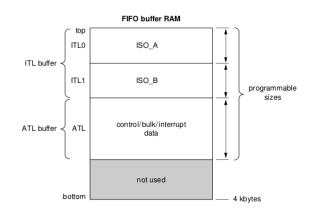

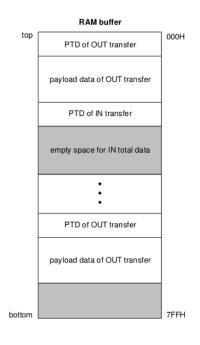

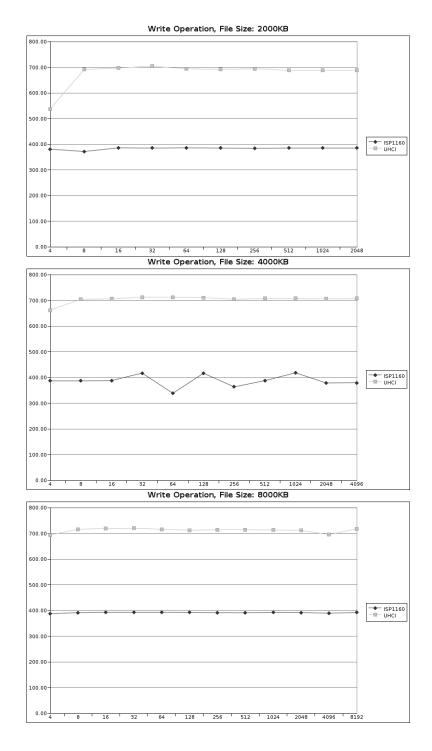

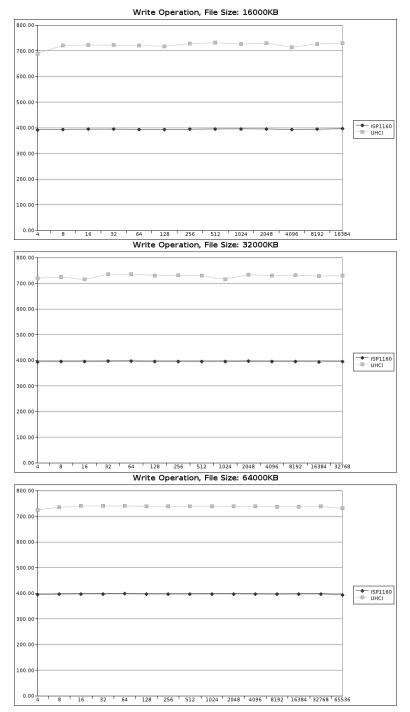

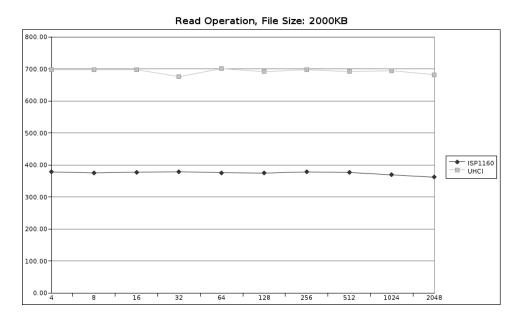

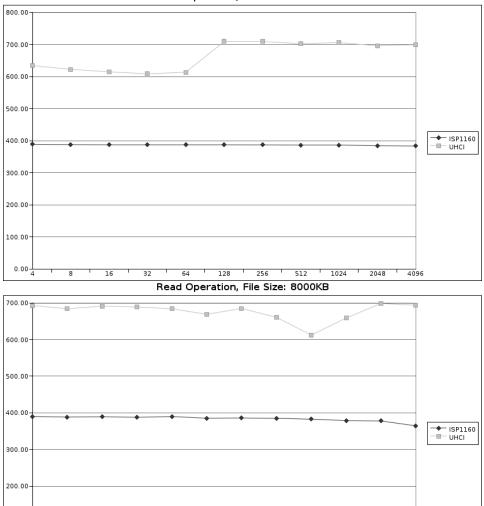

| }ati   | tribute_                                      | ((packed));         |  |