# **Development of a Network Processor in Reconfigurable Logic (FPGA)** Ανάπτυξη Δικτυακού Επεξεργαστή σε Αναδιατασσόμενη Λογική

Technical University of Crete Electronic and Computer Engineering Department

> Author: Constantinos Stefanatos

Supervisor: Ioannis Papaefstathiou, Assistant Professor

Committee: Apostolos Dollas, Professor Dionisios Pnevmatikatos, Associate Professor

September 2009

#### Abstract

Network Processors play a major role in computer network infrastructure and especially in the Internet, since they are embedded in many kinds of devices critical to the correct operation of these networks, such as routers, switches, firewalls etc. By being implemented in such devices, they are responsible for much of the workload these devices have to deal with.

The purpose of this diploma thesis was to develop and implement a Network Processor in Reconfigurable Logic, supporting a specific instruction set, capable of handling some of the tasks Network Processors deal with under normal circumstances. It is capable of operating in 10, 100 and 1000 Mbit/s Ethernet speeds. The design was implemented in an advanced FPGA board.

#### Ελληνικά

Οι Δικτυακοί Επεξεργαστές αποτελούν ένα σημαντικό κομμάτι της υλικής υποδομής διαφόρων δικτύων υπολογιστών, με κυριότερο αυτό του Διαδικτύου. Είναι ενσωματωμένοι σε συσκευές όπως routers, switches, firewalls και συνεπώς αναλαμβάνουν ένα μεγάλο μέρος από τη δουλειά που επιτελούν οι παραπάνω συσκευές.

Στην παρούσα διπλωματική εργασία, ο σκοπός μας ήταν να σχεδιάσουμε και να υλοποιήσουμε ένα Δικτυακό Επεξεργαστή σε Αναδιατασσόμενη Λογική, ο οποίος να υποστηρίζει ένα συγκεκριμένο σετ εντολών, ικανό να εκτελέσει μέρος από τις βασικές λειτουργίες των Δικτυακών Επεξεργαστών, υποστηρίζοντας ταχύτητες λειτουργίας 10, 100 και 1000 Mbit/s Ethernet. Η υλοποίηση της αρχιτεκτονικής έγινε σε μια προηγμένη FPGA.

# Contents

| 1 | Inti | oduct    | ion                |          |            |       |      |   |       |  |   |  | 1  |

|---|------|----------|--------------------|----------|------------|-------|------|---|-------|--|---|--|----|

|   | The  | sis Orga | anization          |          |            | <br>• | <br> | • | <br>• |  | • |  | 2  |

| 2 | The  | eoretic  | al Backg           | round    |            |       |      |   |       |  |   |  | 4  |

|   | 2.1  | OSI L    | ayers              |          |            |       | <br> |   |       |  |   |  | 4  |

|   | 2.2  | Ether    | net Proto          | col      |            |       | <br> |   |       |  |   |  | 5  |

|   |      | 2.2.1    | Frame ty           |          |            |       |      |   |       |  |   |  | 6  |

|   |      | 2.2.2    | Parts of           | -        |            |       |      |   |       |  |   |  | 6  |

|   | 2.3  | Physic   | cal Layer          | Interfac | ces        |       | <br> |   |       |  |   |  | 7  |

|   |      | 2.3.1    |                    |          |            |       |      |   |       |  |   |  | 8  |

|   |      | 2.3.2    | RMII .             |          |            |       | <br> |   |       |  |   |  | 8  |

|   |      | 2.3.3    | SMII               |          |            |       | <br> |   |       |  |   |  | 8  |

|   |      | 2.3.4    | GMII .             |          |            |       | <br> |   |       |  |   |  | 8  |

|   |      | 2.3.5    | RGMII              |          |            |       | <br> |   |       |  |   |  | 9  |

|   |      | 2.3.6    | SGMII .            |          |            |       |      |   |       |  |   |  | 9  |

| 3 | Rel  | ated V   | Vork               |          |            |       |      |   |       |  |   |  | 10 |

|   | 3.1  | Comm     | nercial Sol        | lutions  |            |       | <br> |   |       |  |   |  | 10 |

|   |      | 3.1.1    | IBM/Hi             | fn       |            |       | <br> |   |       |  |   |  | 11 |

|   |      | 3.1.2    | Intel <sup>'</sup> |          |            |       | <br> |   |       |  |   |  | 12 |

|   |      |          | 3.1.2.1            | IXP12    | 2xx .      |       | <br> |   |       |  |   |  | 12 |

|   |      |          | 3.1.2.2            | IXP24    | lxx .      |       | <br> |   |       |  |   |  | 13 |

|   |      |          | 3.1.2.3            | IXP28    | Bxx .      |       | <br> |   |       |  |   |  | 14 |

|   |      |          | 3.1.2.4            | IXP42    | 2x         |       | <br> |   |       |  |   |  | 15 |

|   |      |          | 3.1.2.5            | IXP43    | <b>3</b> x |       | <br> |   |       |  |   |  | 16 |

|   |      |          | 3.1.2.6            | IXP45    | бх.        |       | <br> |   |       |  |   |  | 16 |

|   |      |          | 3.1.2.7            | IXP46    | бх.        |       | <br> |   |       |  |   |  | 16 |

|   |      | 3.1.3    | Motorol            | a/Frees  | cale .     |       | <br> |   |       |  |   |  | 17 |

|   |      |          | 3.1.3.1            | С-Зе.    |            |       |      |   |       |  |   |  | 17 |

|     |            | 3.1.3.2 C-5                                                                                        |

|-----|------------|----------------------------------------------------------------------------------------------------|

|     |            | 3.1.3.3 C-5e                                                                                       |

| 3   | .2 Acad    | emic Research                                                                                      |

|     | 3.2.1      | The PRO3 Architecture - Overview 19                                                                |

|     | 3.2.2      | The PRO3 Architecture - In depth look                                                              |

|     |            | 3.2.2.1 Packet Preprocessor                                                                        |

|     |            | 3.2.2.2 Data Memory Management unit 21                                                             |

|     |            | 3.2.2.3 Scheduler modules                                                                          |

|     |            | 3.2.2.4 Reprogrammable Pipeline Module 22                                                          |

|     | 3.2.3      | The PRO3 Architecture - Development Tools 23                                                       |

| 4 A | rchitect   | ture 24                                                                                            |

| 4   | .1 Virte   | x-5 FPGA Embedded Tri-mode Ethernet MAC 24                                                         |

| 4   | .2 Our l   | $Design  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                          |

|     | 4.2.1      | Configuration of the Tri-mode Ethernet MAC 28                                                      |

|     | 4.2.2      | Architecture - Overview                                                                            |

|     | 4.2.3      | Architecture - In-depth                                                                            |

|     |            | 4.2.3.1 Rx2Mem                                                                                     |

|     |            | 4.2.3.2 Control                                                                                    |

|     |            | 4.2.3.3 R2M                                                                                        |

|     |            | 4.2.3.4 M2P                                                                                        |

|     |            | 4.2.3.5 P2M                                                                                        |

|     |            | 4.2.3.6 M2T                                                                                        |

|     |            | 4.2.3.7 Process                                                                                    |

|     |            | 4.2.3.8 Top Level                                                                                  |

|     | 4.2.4      | Device Utilization                                                                                 |

| 5 1 | Verificati | ion & Performance 56                                                                               |

| 5   | .1 Hard    | ware used $\ldots \ldots 56$ |

|     | 5.1.1      | Virtex-5 Board $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 56$          |

|     | 5.1.2      | Ethernet Category 5e crossover cable                                                               |

|     | 5.1.3      | PC Workstation                                                                                     |

|     | 5.1.4      | Connectivity                                                                                       |

| 5   | .2 Softw   | vare used during Development                                                                       |

|     | 5.2.1      | Xilinx ISE                                                                                         |

|     | 5.2.2      | Xilinx CoreGenerator                                                                               |

|     | 5.2.3      | Xilinx EDK                                                                                         |

| 5   | .3 Softw   | vare used during Verification                                                                      |

|     | 5.3.1      |                                                                                                    |

|     | 5.3.2      | Wireshark                                                                                          |

|    |       | 5.3.3                          | packEth                       | 59 |

|----|-------|--------------------------------|-------------------------------|----|

|    | 5.4   | Verific                        | cation Process                | 60 |

|    |       | 5.4.1                          | Commands loaded in Memory     | 60 |

|    | 5.5   | Perfor                         | mance                         | 62 |

|    |       | 5.5.1 Loopback mode benchmarks |                               |    |

|    |       | 5.5.2                          | Design Latency and Throughput | 62 |

|    |       |                                | 5.5.2.1 Latency               | 62 |

|    |       |                                | 5.5.2.2 Throughput            | 64 |

| 6  | Fut   | ure Wo                         | ork                           | 65 |

| Bi | bliog | graphy                         |                               | 67 |

# List of Figures

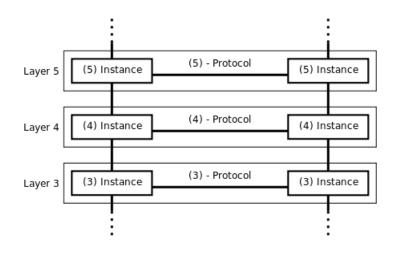

| 2.1  | Communication in the OSI Model                                | 5 |

|------|---------------------------------------------------------------|---|

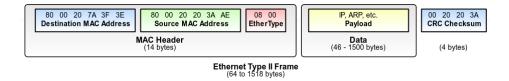

| 2.2  | Ethernet II Frame Format                                      | 7 |

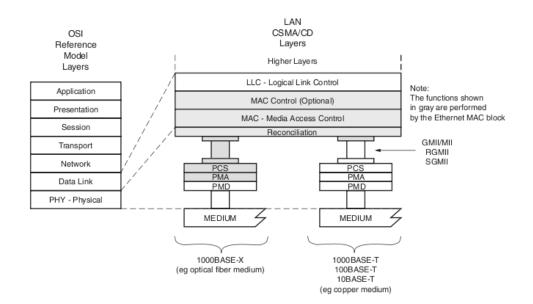

| 4.1  | Virtex-5 Tri-mode Ethernet MAC-supplied OSI Layers 2          | 5 |

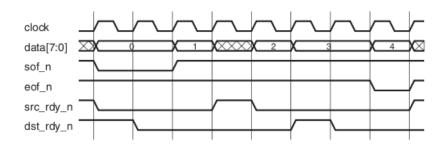

| 4.2  | Frame Transfer with Flow Control across LocalLink Interface 2 | 8 |

| 4.3  | Design Overview Block Diagram                                 | 9 |

| 4.4  | Rx2Mem Block Diagram                                          | 3 |

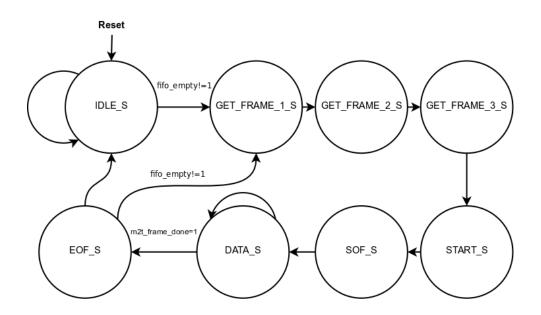

| 4.5  | Rx2Mem FSM 3                                                  | 3 |

| 4.6  | Control Block Diagram 3                                       | 6 |

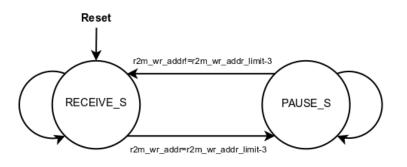

| 4.7  | R2M FSM                                                       | 8 |

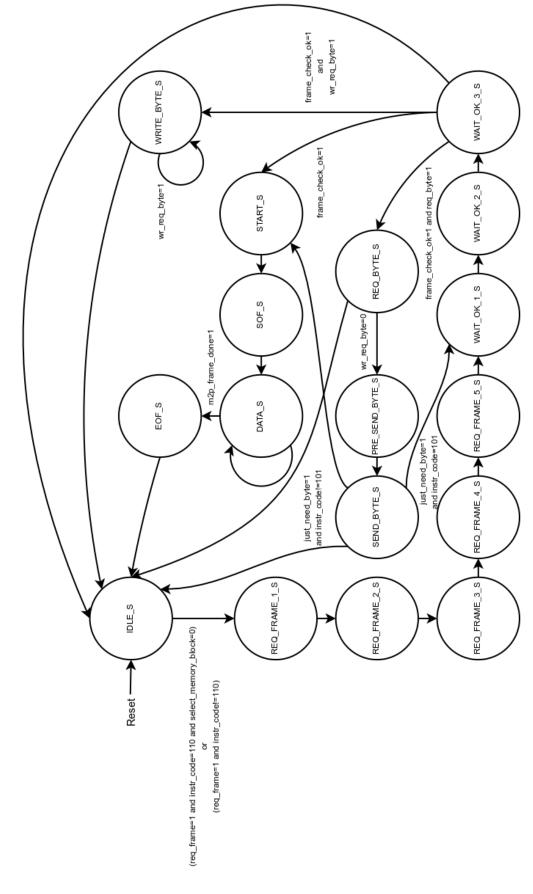

| 4.8  | M2P FSM                                                       | 1 |

| 4.9  | P2M FSM                                                       | 3 |

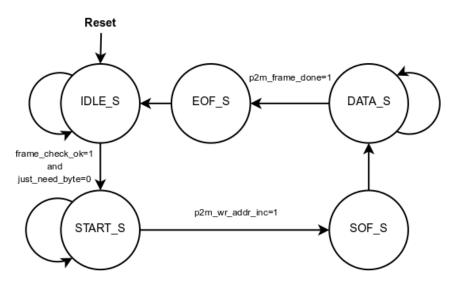

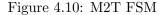

| 4.10 | M2T FSM                                                       | 4 |

| 4.11 | Process Block Diagram                                         | 2 |

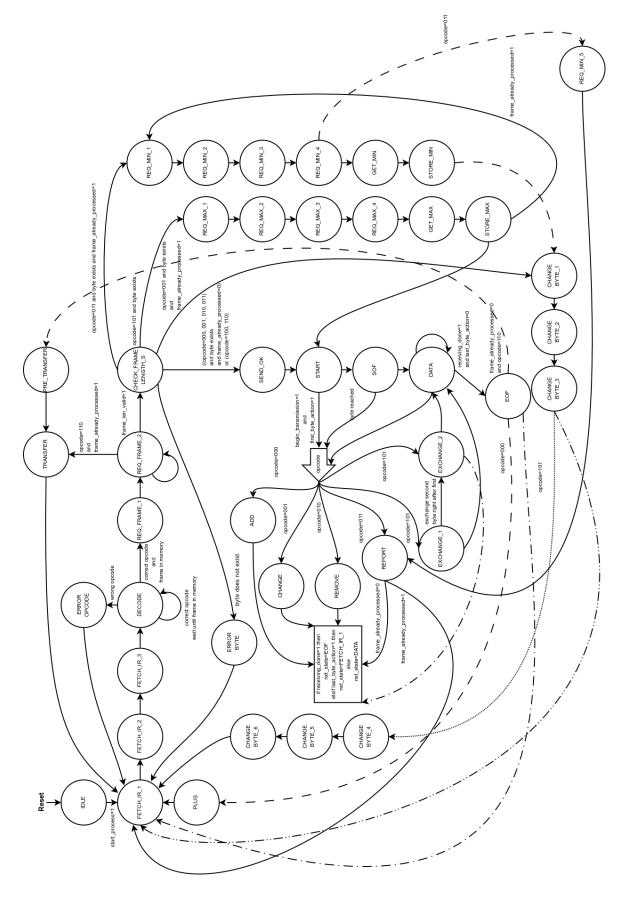

| 4.12 | Process FSM 5                                                 | 3 |

| 4.13 | Top Level Block Diagram 5                                     | 4 |

# List of Tables

| 2.1 | OSI Model                                                 | 4  |

|-----|-----------------------------------------------------------|----|

| 3.1 | Network Processor Manufacturers                           | 10 |

| 4.1 | Selection of configuration options for Virtex-5 FPGA Tri- |    |

|     | mode Ethernet MAC                                         | 26 |

| 4.2 | LocalLink Interface                                       | 27 |

| 4.3 | Command Syntax and Opcodes                                | 30 |

| 4.4 | Rx2Mem Interface                                          | 32 |

| 4.5 | Control Interface                                         | 35 |

| 4.6 | Command bit decomposition                                 | 46 |

| 4.7 | Process Unit Interface                                    | 51 |

| 4.8 | Top Level Interface                                       | 54 |

| 4.9 | Device Utilization Summary                                | 55 |

|     |                                                           |    |

| 5.1 | Loopback mode benchmarks (T is for total, U for upload)   | 63 |

| 5.2 | Instruction Set Latency                                   | 63 |

# Acronyms

| IC    | Integrated Circuit                          |

|-------|---------------------------------------------|

| NP    | Network Processor                           |

| BGA   | Ball Grid Array                             |

| PBGA  | Plastic Ball Grid Array                     |

| SDK   | Software Development Kit                    |

| ΑΡΙ   | Application Programming Interface           |

| MAC   | Media Access Control                        |

| МП    | Media Independent Interface                 |

| RMII  | Reduced Media Independent Interface         |

| SMII  | Serial Media Independent Interface          |

| GMII  | Gigabit Media Independent Interface         |

| RGMII | Reduced Gigabit Media Independent Interface |

| SGMII | Serial Gigabit Media Independent Interface  |

| тві   | Ten Bit Interface                           |

| QoS   | Quality of Service                          |

| тср   | Transmission Control Protocol               |

| PCI   | Peripheral Component Interconnect           |

| USB   | Universal Serial Bus                        |

| POS      | Packet Over Sonet                                     |

|----------|-------------------------------------------------------|

| GUI      | Graphical User Interface                              |

| BSM-CCGA | Bottom Surface Metallurgy - Ceramic Column Grid Array |

| SAN      | Storage Area Network                                  |

| DSL      | Digital Subscriber Line                               |

| DSLAM    | Digital Subscriber Line Access Multiplexer            |

| CMTS     | Cable Modem Termination System                        |

| LAN      | Local Area Network                                    |

| VLAN     | Virtual Local Area Network                            |

| WAN      | Wide Area Network                                     |

| MAN      | Metropolitan Area Network                             |

| IP       | Internet Protocol                                     |

| IPv6     | Internet Protocol version 6                           |

| VPN      | Virtual Private Network                               |

| RMON     | Remote Monitoring                                     |

| ROM      | Read Only Memory                                      |

| SRAM     | Static Random Access Memory                           |

| DRAM     | Dynamic Random Access Memory                          |

| SDRAM    | Synchronous Dynamic Random Access Memory              |

| RDRAM    | Rambus Dynamic Random Access Memory                   |

| CRC      | Cyclic Redundancy Checking                            |

| ECC      | Error Correction Code                                 |

| IDE      | Integrated Development Environment                    |

| RISC     | Reduced Instruction Set Computer                      |

| IXA   | Internet Exchange Architecture                    |  |  |

|-------|---------------------------------------------------|--|--|

| DDR   | Double Data Rate                                  |  |  |

| QDR   | Quad Data Rate                                    |  |  |

| FCBGA | Flip-Chip Ball Grid Array                         |  |  |

| FLBGA | Fine-Line Ball Grid Array                         |  |  |

| VoIP  | Voice over Internet Protocol                      |  |  |

| АТМ   | Asynchronous Transfer Mode                        |  |  |

| SAR   | Segmentation and Reassembly                       |  |  |

| GTP   | General Packet Radio Service Tunneling Protocol   |  |  |

| LVDS  | Low Voltage Differential Signaling                |  |  |

| SPI   | System Packet Interface                           |  |  |

| CSIX  | Common Switch Interface                           |  |  |

| IPsec | Internet Protocol Security                        |  |  |

| SSL   | Secure Socket Layer                               |  |  |

| TLS   | Transport Layer Security                          |  |  |

| NPE   | Network Processing Engine                         |  |  |

| DES   | Data Encryption Standard                          |  |  |

| 3DES  | Triple Data Encryption Standard                   |  |  |

| AES   | Advanced Encryption Standard                      |  |  |

| SHA-1 | Secure Hash Algorithm 1                           |  |  |

| MD5   | Message-Digest Algorithm 5                        |  |  |

| SME   | Small and Medium Enterprises                      |  |  |

| IAD   | Integrated Access Devices                         |  |  |

| IEEE  | Institute of Electrical and Electronics Engineers |  |  |

| TDM  | Time-Division Multiplexing                   |

|------|----------------------------------------------|

| AAL  | Asynchronous Transfer Mode Adaptation Layers |

| HDLC | High-Level Data Link Control                 |

| RFID | Radio-Frequency Identification               |

| ХР   | Executive Processor                          |

| СР   | Channel Processor                            |

| SDP  | Serial Data Processor                        |

| SP   | Services Processor                           |

| TLU  | Table Lookups Unit                           |

| QMU  | Queue Management Unit                        |

| BMU  | Buffer Management Unit                       |

| FP   | Fabric Processor                             |

| MSAP | Multiservice Access Platform                 |

| СРЕ  | Customer Premises Equipment                  |

| PRO3 | Programmable Protocol Processor              |

| NPU  | Network Processing Unit                      |

| PDU  | Protocol Data Unit                           |

| СРՍ  | Central Processing Unit                      |

| DMM  | Data Memory Management                       |

| тѕс  | Task Scheduler                               |

| TRS  | Traffic Scheduler                            |

| RPM  | Reprogrammable Pipeline Module               |

| PPE  | Protocol Processing Engine                   |

| FEX  | Field Exctraction Engine                     |

|      |                                              |

| FMO   | Field Modification Engine                      |

|-------|------------------------------------------------|

| CL    | Configuration Library                          |

| ТСАМ  | Ternary Content-Addressable Memory             |

| I/O   | Input/Output                                   |

| FIFO  | First-In, First-Out                            |

| OSI   | Open Systems Interconnection                   |

| ISO   | International Organization for Standardization |

| LLC   | Logical Link Control                           |

| SNAP  | Subnetwork Access Protocol                     |

| MTU   | Maximum Transmission Unit                      |

| V5    | Virtex-5                                       |

| TEMAC | Tri-mode Ethernet MAC                          |

| Rx    | Receive                                        |

| Тх    | Transmit                                       |

| IFG   | Interframe Gap                                 |

| FCS   | Frame Check Sequence                           |

| DCR   | Device Control Register                        |

| PCS   | Physical Coding Sublayer                       |

| РМА   | Physical Medium Attachment                     |

| LL    | LocalLink Interface                            |

| ASM   | Address Swap Module                            |

| FSM   | Finite State Machine                           |

| BRAM  | Block RAM                                      |

### Chapter 1

## Introduction

A Network Processor (NP) is an Integrated Circuit (IC), with a feature set designed to tackle the needs of the networking application domain. Typically NPs are software programmable and have generic functions, which are similar to general purpose Central Processing Units (CPUs), commonly used in many different products.

Due to the fact that in modern telecommunication systems information is transferred in a packet form instead of the analog signals used in older systems, a need has arisen to develop ICs optimized to handle such packet forms of data. These ICs are called NPs and they make use of specific features or architectures to enhance and optimize packet processing in computer networks. By evolving over time, NPs have grown to become more flexible but at the same time more complex ICs. In newer iterations, NPs are programmable, thus providing the advantage of handling many different functions using the same hardware, by only installing the appropriate software.

NPs are designed with architectures that are aimed to augment network processing needs and applications. A common set of these architectures is:

- Pipeline of processors, where each pipeline stage consists of an entire processor

- Parallel processing, making use of multiple processors

- Specialized microcoded engines

A NP supports — as we have already mentioned — a set of generic functions. Some of those are:

• Pattern matching

- Key lookup

- Computation

- Data field modification

- Queue management

- Control processing

- Recirculation of packets

NPs are employed in many different types of network equipment, including, but not limited to:

- Routers both hardware and software

- Switches

- Firewalls

- Intrusion detection and prevention systems

- Network monitoring systems

Taking advantage of the programmability of NPs, software programs executed on the processors can be used to provide different services. Some of the most common and generally needed services performed by NPs include:

- Packet/frame discrimination and forwarding typically needed by routers or switches

- Quality of Service (QoS) enforcement handling and processing of packets/frames according to certain preferences

- Access Control deciding whether a packet should be accepted on the network node

- Encryption processor provided hardware encryption of data

- Transmission Control Protocol (TCP) offload processing

The purpose of this thesis is to develop a custom NP architecture from scratch, supporting a simple instruction set and capable of handling some of the aforementioned services and functions. The target platform of this architecture is the Virtex-5 FPGA board, since it provides a very efficient and easy to implement in user designs Ethernet MAC wrapper.

$\mathbf{2}$

#### Thesis Organization

The thesis is organized into chapters, each with a distinctive theme that upon its completion, leads naturally into the following one. We are now going to present the chapters and describe in a few lines what one can expect to find in each of them.

In the second chapter, we present the theoretical background necessary for one to understand the basic concepts behind all the information presented in this thesis. We begin by describing the Open Systems Interconnection (OSI) Layers and how they affect network architectures in general and then proceed to give a short description of all the information about the Ethernet standard that is needed to get a clear idea on some of the architectural decisions. Finally, we present a short overview of all the available Physical layer interfaces in order to justify the choice we made in our design later on.

In the third chapter, we deal with related work concerning NPs in both the commercial and the academic domain. We present some companies and their respective work concerning NPs; more specifically, we focus on products by IBM/Hifn, Intel and Freescale/Motorola. Then we move on to discuss a certain NP architecture developed in academic research, that of the Programmable Protocol Processor (PRO3).

In the fourth chapter, we present the architecture designed for this thesis. We begin by examining the base of the design, which is an Ethernet wrapper embedded on the Virtex-5 board and then justify some of the choices made during its generation process. After that, we continue by describing the design that implements the NP, all its modules and their inner workings; provided in this chapter are detailed block diagrams, Finite State Machine (FSM) states and their transitions and each module's interface.

In chapter five, a short presentation of the software tools used during the design's development and verification is given. Following after that is a step by step description of the verification process. Finally, a presentation of some benchmarks along with the design's performance is given.

In the last chapter, we propose some improvements to the design in order for it to become more efficient and complete.

### Chapter 2

## **Theoretical Background**

#### 2.1 OSI Layers

The OSI Model is an abstract description for layered communications and computer network protocol design that was developed in the late 1970s by the International Organization for Standardization (ISO). Its purpose is to provide guidelines for compatibility in newly designed computer networks, which is of utter importance, since computer networks can be developed in different architectures, yet need to be compatible with each other in order to be useful. It divides network architecture into seven layers [2, 3], as shown in table 2.1.

| Level | Layer        |

|-------|--------------|

| 7     | Application  |

| 6     | Presentation |

| 5     | Session      |

| 4     | Transport    |

| 3     | Network      |

| 2     | Data Link    |

| 1     | Physical     |

Table 2.1: OSI Model

A layer is considered a collection of conceptually similar functions that provide services to the layer above and receive services by the layer below. On each layer, an instance provides services to the instances at the above layer and requests services from the layers below. When different network nodes communicate with each other, each layer in the transmitting node passes data to the layer below while at the same time adding layer-specific data. When the Physical layer is reached, it sends the assembled data to the Physical layer of the receiving node. From there, each layer passes data to the layer above - each time removing the aforementioned layer-specific data - until the target layer is reached.

Communication in the OSI Model (see figure 2.1) is done with instances being on the same layer communicating with each other as if they exchange information directly, since through abstraction, each layer handles its own, specific part of the data.

Figure 2.1: Communication in the OSI Model

The OSI Model does not specify implementation details nor any programming interfaces; it only defines the so-called OSI Service Specifications, thus allowing for different implementations, as long as they conform to these Specifications.

#### 2.2 Ethernet Protocol

The Ethernet [5] Protocol (standardized as IEEE 802.3 [4]) is a family of frame-based computer networking technologies. It defines wiring and signaling standards for the Physical layer (Layer 1) of the OSI Model through means of network access at the Media Access Control (MAC) — sublayer of

the Data Link layer (Layer 2) [7] — and a common addressing format. Originally developed at Xerox PARC in 1973-1975 by Robert Metcalfe, David Boggs, Chuck Thacker and Butler Lampson and in wide use from 1980 until today, it has gradually evolved into the de facto standard for wired Local Area Networks (LANs).

The main varieties of Ethernet are 10 Mbit/s (called simply Ethernet), 100 Mbit/s (Fast Ethernet), 1000 Mbit/s (Gigabit Ethernet), 10 Gbit/s (10-Gigabit Ethernet) and — still in development at the time of writing — 100 Gbit/s (100-Gigabit Ethernet). These varieties differ not only in the bandwidth they provide, but also in the physical medium they use, with the most common being twisted pair cables and more demanding applications using fibre optic cables.

#### 2.2.1 Frame types

When data packets are transferred through the physical medium, they are referred to as frames. Ethernet frames have variations of their own: there is the Ethernet Version 2 Frame (Ethernet II Frame) or DIX Frame (DIX stands for DEC, Intel, Xerox) which is the most common today since it is used by the Internet Protocol (IP); IEEE's 802.3 Frame, Novell's non-standard frame variation of IEEE 802.3 without an IEEE 802.2 Logical Link Control (LLC) header, IEEE 802.2 LLC Frame and the IEEE 802.2 LLC\Subnetwork Access Protocol (SNAP) Frame. Optionally, all the aforementioned frame types can contain a IEEE 802.1Q tag which is used for Virtual Local Area Network (VLAN) identification and prioritization (QoS).

At the Physical layer, when a frame is transmitted, it is preceded by a preamble of 7 bytes — each with the hexademical value of AA — and a Start-of-Frame-Delimiter, 1 byte with the value AB (hex). After the frame follows the Interframe Gap (IFG), which consists of 12 bytes of idle characters. All of the aforementioned bytes are removed by network adapters before being passed to the Data Link layer.

#### 2.2.2 Parts of a frame

Since it is the most common, we are going to present the Ethernet II Frame format [6]. By examining figure 2.2, we can see that the frame consists of 3 parts; a MAC Header, Data and the Frame Checksum.

The Maximum Transmission Unit (MTU) of standard Ethernet II Frames is 1500 bytes [9], which when added with the MAC Header and Frame Checksum parts, totals to a maximum frame size of 1518 bytes, while for VLAN

Figure 2.2: Ethernet II Frame Format

tagged frames, it is extended to 1522 bytes. On the other hand, the minimum frame size is 64 bytes.

The MAC Header contains the Destination MAC Address field, 6 bytes identifying in a unique way [8] the network adapter that is to receive the frame, the Source MAC Address field, 6 bytes to identify the network adapter transmitting the frame and the EtherType field, 2 bytes used to identify the type of data carried by the frame. It is worth mentioning that the EtherType field is what differentiates the Ethernet II Frame from the Institute of Electrical and Electronics Engineers (IEEE) 802.3 Frame, since the latter uses that field as a length identifier, giving the length of actual data in the frame. To circumvent such problems, a convention has been made, which states that values between 64 and 1522 indicate a Length field, while values greater than 1536 indicate an EtherType field.

The Data part of the frame contains the actual data, which can range from 46 to 1500 bytes. Since data could be less than 46 bytes, padding is used in order to make the frame reach the minimum required size of 64 bytes.

Finally, the Frame Checksum part, uses Cyclic Redundancy Checking (CRC) to calculate 4 bytes used to check the correctness of the frame. The Checksum is generated by the network adapter before the transmission of the frame begins and is calculated again upon receival of the frame; if the calculated code matches the one in the Checksum part, the frame was succesfully transmitted and so it is passed on the Data Link layer. Otherwise, the frame is dropped, thus considered to be erroneous and not passed on to the Data Link layer.

#### 2.3 Physical Layer Interfaces

There is a selection of interfaces available to achieve data transfer between the Physical and the Data Link layers, and these are:

- Media Independent Interface (MII)

- Reduced Media Independent Interface (RMII)

- Serial Media Independent Interface (SMII)

- Gigabit Media Independent Interface (GMII)

- Reduced Gigabit Media Independent Interface (RGMII)

- Serial Gigabit Media Independent Interface (SGMII)

#### 2.3.1 MII

MII [10, 36] is a standard interface used to connect Ethernet and Fast Ethernet MAC sublayers to the Physical layer. The media independent part means that the same interface can be used to connect to different types of Physical layer devices without the need to redesign or replace the MAC hardware. It is a parallel interface, transferring 4-bit words, operating at 2.5 MHz for Ethernet and 25 MHz for Fast Ethernet, that uses 16 pins to connect the Physical layer with the MAC sublayer.

#### 2.3.2 RMII

The RMII [11] also supports Ethernet and Fast Ethernet MAC sublayers to Physical layer interfacing, differentiating itself from MII by reducing the pin count from 16 to a variable number of 6 to 10 (hence the reduced part of the title), by operating at a constant clock rate of 50 MHz and by transferring 2-bit words.

#### 2.3.3 SMII

SMII is a serial implementation of MII.

#### 2.3.4 GMII

GMII [12, 36] was developed in order to support Gigabit Ethernet, uses 8-bit data words, can operate at a maximum clock rate of 125 MHz and increases the pin count to 24. It is backwards compatible with MII, since it can operate at its offered speeds of 2.5 MHz and 25 MHz, thus making it able to connect to Ethernet and Fast Ethernet MAC sublayers as well. This of course renders the MII an actual subset of the GMII, making the latter a better choice, since

by a small increase in pins, a ten-fold increase in the supported Ethernet operating speed is achieved.

#### 2.3.5 RGMII

RGMII [13, 36] is once again a reduced — concerning pin count, which is only half (12) compared to that of GMII — version of the GMII, which was introduced by Hewlett Packard. Performance is on par though and this is achieved by transferring data on both positive and negative clock edges (Double Data Rate (DDR)). This fact makes RGMII a much better alternative to GMII.

#### 2.3.6 SGMII

The SGMII [14, 36] Physical layer interface was defined by Cisco Systems [15], a market leader in the networking domain. It converts the parallel nature of the GMII into a serial format using 2 data and 2 clock signals for each data direction (receive and transmit), thus exchanging frame data between the Physical layer and the MAC sublayer with a total pin count of 8. The data signals operate at a rate of 1.25 Gbps, while the clock signals operate at a 625 MHz rate (DDR). Due to these speeds, differential pairs are used in order to provide signal integrity and at the same time minimize system noise. Because of the increased performance and the low pin count, SGMII is usually preferred by manufacturers [36].

### Chapter 3

## **Related Work**

NPs have been an important subject in both commercial and academic research. In the following section we are going to present some companies and their respective work concerning NPs and in the next section we are going to present the work done in an academic research about a NP architecture.

#### **3.1** Commercial Solutions

In the commercial domain, the companies developing NPs are many and some of them are listed in table 3.1.

| Altera                             | AMD                                                                                                                      |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| Applied Micro Circuits Corporation | Bay Microsystems                                                                                                         |

| Cavium Networks                    | Conexant                                                                                                                 |

| Freescale                          | Hifn                                                                                                                     |

| LSI Corporation                    | Mindspeed                                                                                                                |

| Netronome                          | Raza Microelectronics Inc                                                                                                |

| Wintegra                           | Xelerated                                                                                                                |

| Ubicom                             | Xilinx                                                                                                                   |

| Intel                              |                                                                                                                          |

|                                    | Applied Micro Circuits Corporation<br>Cavium Networks<br>Freescale<br>LSI Corporation<br>Netronome<br>Wintegra<br>Ubicom |

Table 3.1: Network Processor Manufacturers

By examining table 3.1, we can see that there is a large number of companies researching, developing and manufacturing NPs.

In the rest of this section, we are going to focus on three manufacturers, IBM/Hifn, Intel and Motorola/Freescale.

#### 3.1.1 IBM/Hifn

IBM is a company with major presence in the computer industry, that ventures both in software and in hardware. It has a NP line, dubbed PowerNP that has been acquired in 2004 by Hifn [16, 17], a company which specialises in integrated circuits and software for network infrastructure developers. IBM is still producing the NPs, though they are being distributed by Hifn as part of their product line. Nevertheless, the architecture remains an intellectual property of IBM.

The PowerNP line is currently represented by a single product according to the website of Hifn [18], the 5NP4G NP, which uses the NP4GS3 [19, 20]. The NP4GS3 is an advanced, robust, programmable, high-performance NP optimized for packet processing which integrates a switching engine, a search engine, frame processors and multiplexed MACs. It is designed to satisfy enterprise, core and edge networking and Internet requirements at wire speed. Being scalable, the NP4GS3 can meet increasing bandwidth and functional demands. Thus, it can offer a wide selection of services, including but not limited to QoS, scheduling and flow control.

It features an embedded IBM PowerPC microprocessor, 16 programmable picoprocessors and multiple hardware accelerators. With the above hardware characteristics it can process up to 32 frames in parallel. The hardware accelerators can perform tree searches, frame forwarding, frame filtering, frame alteration and other functions, while the embedded PowerPC allows manufacturers to support their own custom functions, such as enhanced frame processing and higher-layer protocols.

Continuing on the features list, the NP4GS3 offers advanced flow control in order to prevent TCP collapse, hardware support for port mirroring and multi-threads support to improve performance.

The available interfaces are an integrated Peripheral Component Interconnect (PCI) interface that allows peripheral devices to be attached to it as well as OC-3, OC-12 and OC-48 Packet Over Sonet (POS) interfaces.

Its integrated MACs can support up to 4 Gigabit Ethernet or 40 Fast Ethernet ports, that can be accessed through SMII, GMII and Ten Bit Interface (TBI).

The NP4GS3 does not lack in programmability, since it is supported by software tools available for Windows, Solaris and Linux environments. These software tools include an assembler, a full-function simulator, a Graphical User Interface (GUI) debugger, a test case generator, demonstration picocode and test case scripts. Its simulation environment supports a distributed software model, which enables flexible testing configurations from software unit test to system test, even before having the actual hardware at hand. These tools enable using the NP4GS3 for rapid development and deployment of new services which can be applied as software upgrades, without altering the underlying hardware.

The packaging of the NP4GS3 is a 1088-pin Bottom Surface Metallurgy - Ceramic Column Grid Array (BSM-CCGA).

Some of the NP4GS3's applications, include:

- Multi-layer Chassis Switch-Router

- Server Load Balancer

- Network Edge QoS Traffic Manager

- Storage Area Network (SAN) Switch

- Core/Edge Router

- Digital Subscriber Line Access Multiplexer (DSLAM)

- Web Caching Server

- Wide Area Network (WAN) IP Switch

- Firewall and Virtual Private Network (VPN) Appliances

- IP Service Blade

#### 3.1.2 Intel

Intel is a renowned processor manufacturer and has had a long line of NPs in its product briefcase. Their IXP NP range is discontinued, yet it is worth mentioning, as it has evolved greatly since its incubation.

#### 3.1.2.1 IXP12xx

The first NP family developed by Intel was the IXP12xx [21, 22]. It was meant to be used in web switches, broadband access platforms and network appliances and could offer Layer 2 and Layer 3 forwarding, protocol conversion, QoS, filtering, firewalling, handling of VPNs, load balancing, Remote Monitoring (RMON) and intrusion detection.

They featured an integrated Intel StrongARM processor core, compatible with the ARM architecture, 6 integrated programmable multi-threaded microengines, an open IX bus architecture, an integrated PCI interface and integrated high-performance memory controllers for Static Random Access Memory (SRAM) and Synchronous Dynamic Random Access Memory (SDRAM). Also in the list of features are CRC and Error Correction Code (ECC) memory.

Lastly, the processor family delivered extensive programmability in software through the provided Intel Internet Exchange Architecture (IXA) Software Development Kit (SDK) 2.0, which could be used to extend their range of applications. Also provided were the Intel IXDP1200 Advanced Developer Platform, a Windows NT Integrated Development Environment (IDE) for Embedded Linux and example designs for an ATM/OC-3 to Fast Ethernet IP router and a WAN/LAN access switch.

The NPs in the IXP12xx family were available with core speeds of 166, 200 and 232 MHz, with a low power consumption of a typical value of 5 W or less. The package form of this family was a 432-pin HL-Ball Grid Array (BGA).

#### 3.1.2.2 IXP24xx

The architecture of the IXP24xx [23] NP family consists of an integrated Intel XScale Core (32-bit Reduced Instruction Set Computer (RISC)), 8 integrated fully programmable multi-threaded microengines (second generation), integrated PCI interface, receive and transmit interfaces supporting Utopia, SPI-3 or CSIX, integrated high-performance memory controllers for DDR Dynamic Random Access Memory (DRAM) and Quad Data Rate (QDR) SRAM and hardware support for memory access queuing.

This NP family was accompanied by the Intel IXA SDK 3.0 complemented by a hardware development platform with supporting software and tools, which account for its flexibility and extension of its capabilities. Included are Intel's own Microengine C compiler and Microengine C Networking library. Also included was the very important capability to retarget code developed for the 12xx family in order to make it compatible with the 24xx family.

The IXP24xx family was available at core speeds of 400 and 600 MHz, with a typical power consumption of 10 W. The packaging is a 1356-pin Flip-Chip Ball Grid Array (FCBGA).

Since it supports OC-48 line rates, these NPs are used in a wide selection of applications such as WAN multi-service switches, DSLAMS, Cable Modem Termination System (CMTS) equipment, 2.5G and 3G wireless infrastructure base station controllers and gateways and Layer 4 to Layer 7 switches with content-based load balancing and firewalls. Their programmability also allows them to be used in Voice over Internet Protocol (VoIP) gateways, multi-service access platforms, high-end routers, remote access concetrators and VPN gateways. Their usage models include:

- Aggregation, Asynchronous Transfer Mode (ATM) Segmentation and Reassembly (SAR), traffic shaping, policing, forwarding and protocol conversion in DSLAM equipment

- Aggregation, forwarding and protocol conversion in CMTS equipment

- ATM SAR, encryption and forwarding in base station controllers/radio network controllers

- General Packet Radio Service Tunneling Protocol (GTP) and Internet Protocol version 6 (IPv6) forwarding in wireless infrastructure

- ATM SAR, traffic shaping, policing, protocol conversion and aggregation for multi-service switches

- Content-aware load balancing, forwarding and policing

#### 3.1.2.3 IXP28xx

The IXP28xx [24] NP family's architecture is comprised of an integrated Intel XScale Core, 16 integrated programmable multi-threaded microengines (second generation), a PCI interface, two unidirectional 16-bit Low Voltage Differential Signaling (LVDS) data interfaces programmable to be System Packet Interface (SPI)-4.2 or Common Switch Interface (CSIX), an 8-bit asynchronous control interface, 5 industry-standard high-performance memory controllers for Rambus Dynamic Random Access Memory (RDRAM) and QDR SRAM memory and hardware support for memory access queuing.

The family's life is extended through the provided IXA SDK 3.0 and the hardware development platform, since it allows for great programmability and thus extension of the NPs' functionality.

The XScale core is clocked at 700 MHz, while the microengines are clocked at 1.0 and 1.4 GHz, while the family's power performance is at a typical 14 W.

This family supports OC-192 line rates, which makes it ideal for highperformance applications such as Metropolitan Area Network (MAN) switches and routers, Internet edge and core switches and routers, multi-service switches, 10 Gbps enterprise switches and routers for advanced data centers, SAN and content-aware server off-load/web switches. Its programmability allows it to be used to provide Internet Protocol Security (IPsec) and VPN solutions. It is also great in wireless infrastructure equipment. Its functionality includes:

- Ethernet/POS/ATM Layer 4 forwarding in core, MAN and edge applications

- Protocol conversion, forwarding and aggregation for multi-service switches, cable headends and DSLAM aggregation

- ATM SAR and forwarding with advanced traffic shaping

- Content-aware load balancing, forwarding and policing

- Encryption for VPNs and IPsec applications

- GTP and IPv6 in wireless infrastructure applications

- TCP/IP termination for enterprise data center and SANs

- Secure Socket Layer (SSL)/Transport Layer Security (TLS) acceleration

#### 3.1.2.4 IXP42x

Architecturally, the IXP42x [25] NP family changes quite a bit when compared to the previously mentioned IXP families. This one, features an Intel XScale processor along with up to 3 Network Processing Engines (NPEs) which are basically processors of their own. Also integrated are a PCI interface, a Universal Serial Bus (USB) 1.1 interface, a Utopia interface, 2 integrated 10/100 Ethernet MACs (MII), a high-performance SDRAM memory controller and hardware support for Data Encryption Standard (DES), Triple Data Encryption Standard (3DES), Advanced Encryption Standard (AES), Secure Hash Algorithm 1 (SHA-1) and Message-Digest Algorithm 5 (MD5) encryption and hashing algorithms. The latter hardware support is provided through the aforementioned NPEs.

Once again, a SDK supporting Windows and Linux as well as a hardware development platform are provided, thus gracing this NP family with great extensibility and longevity.

This family has outstanding energy efficiency, since it has a typical system power consumption of 1-1.5 W while operating at a clock speed of up to 533 MHz. The package is a 492-pin Plastic Ball Grid Array (PBGA).

Its applications include, but are not limited to, high-performance Digital Subscriber Line (DSL) modems, high-performance cable modems, residential gateways, Small and Medium Enterprises (SME) routers, Integrated Access Devices (IAD), set-top boxes, DSLAMs, wireless access points in accordance with the IEEE 802.11a/b/g protocols, industrial controllers, network printers and the control plane. The capabilities of this family, in more detail, include:

- Layer 2, Layer 3 forwarding

- ATM, Time-Division Multiplexing (TDM), Ethernet MAC filtering

- Asynchronous Transfer Mode Adaptation Layers (AAL) SAR, TDM framing, High-Level Data Link Control (HDLC) processing

- Hardware supported DES, 3DES data encryption

- Hardware supported SHA-1, MD5 hashing algorithms

#### 3.1.2.5 IXP43x

The IXP43x [26] NP family differentiates itself from the IXP42x by providing up to 2 NPEs that support double the amount of integrated instruction and data memory when compared to the NPEs in the IXP42x line, while at the same time adding support for DDR1 and DDR2 memory with ECC and USB 2.0.

The packaging is now a 460-pin PBGA and the available operating clock speeds are 400, 533 and 667 MHz, with a typical power consumption of 3.44 W.

#### 3.1.2.6 IXP45x

The IXP45x [27] NP family offers support only for DDR1 memory and integrates up to  $3 \ 10/100$  Ethernet MACs (MII).

The packaging once again changes to a 544-pin PBGA and the available clock speeds are 266, 400 and 533 MHz.

#### 3.1.2.7 IXP46x

The IXP46x [28] NP family differentiates itself from the other IXP4xx families by integrating up to 3 10/100 Ethernet MACs (MII or SMII) and by offering integrated hardware support for IEEE 1588 protocol.

The core this time operates at a selection of 266, 400, 533 and 667 MHz while being packaged in 544-pin PBGA.

#### 3.1. COMMERCIAL SOLUTIONS

#### 3.1.3 Motorola/Freescale

Motorola is a company specialised in communications, manufacturing products ranging from mobile phones to Radio-Frequency Identification (RFID) solutions. Among their products of course, lies a NP family, the C-Port family, consisting of processors C-3e, C-5 and C-5e. These NPs are manufactured through its spinoff company, Freescale Semiconductor.

#### 3.1.3.1 C-3e

The first member of the C-Port line of NPs is the C-3e [29, 30]. Its architecture consists of 17 programmable RISC cores, where one is used as the Executive Processor (XP) and the other 16 as Channel Processors (CPs). The CPs have 2 Serial Data Processors (SDPs) each, and 8 of them implement external programmable interfaces, while the other 8 are used internally, as Services Processors (SPs).

Also part of the architecture are an integrated Table Lookups Unit (TLU) coprocessor, a Queue Management Unit (QMU) coprocessor, a Buffer Management Unit (BMU) coprocessor, and a Utopia interface Fabric Processor (FP).

Integrated in the architecture are interfaces such as PCI, serial, 10/100 Ethernet MACs (RMII), 1000 Ethernet MAC (GMII, TBI), FibreChannel MACs (TBI) and Utopia. It supports OC-3 and OC-12 line rates.

The C-3e NP also provides complete programmability using a standard Application Programming Interface (API) and C programming language, which we need to state that are fully software compatible with the rest of the C-Port NP family.

Its operating frequency is up to 180 MHz with a typical power consumption of 5.5 W, and it comes in a highly-integrated 728-pin BGA package.

#### 3.1.3.2 C-5

The C-5 [31, 32] is the next NP of the C-Port family. This NP's architecture is comprised of 16 CPs and 5 coprocessors responsible for supervisory tasks (XP), high-speed fabric interface management (FP), networking lookups (TLU), queue control (QMU) and payload storage (BMU). Each of the CPs contains a RISC programmable core and 2 SDPs, the one to receive, the other to transfer.

The integrated interfaces are PCI, serial, Utopia, 10/100 Ethernet MACs (RMII), 1000 Ethernet MAC (GMII, TBI) and FibreChannel MAC. The line rates supported by the C-5 are OC-3, OC-12 and OC-48.

This NP supports extensive programmability, through the provided API and using C/C++ as programming languages.

The C-5's operating frequencies are 166, 180, 200 and 233 MHz with a respective typical power consumption of 15, 16, 17.5 and 20 W. The packaging of this NP is an 838-pin BGA.

A small list of C-5's breadth of applications follows:

- Multiservice Access Platforms (MSAPs)

- DSLAM

- Cable and wireless head-end systems

- Ethernet/IP/Frame Relay/ATM interworking

- Internet access switch/routers

- Load balancing web server switches

- Optical edge switch/routers and add/drop multiplexers

- IP Gigabit/Terabit routers

- WAN Customer Premises Equipment (CPE)

- MAN CPE and head-end equipment

#### 3.1.3.3 C-5e

The last member of the C-Port NP family we are presenting is the C-5e [33, 34]. The architecture is quite similar to its aforementioned siblings, since it also consists of 16 CPs (with a programmable RISC core and 2 SDPs each), an XP responsible for supervisory tasks and management of host processing, a FP for high-speed fabric interface management, a TLU for networking lookups and classification, a QMU for queue control and traffic management and a BMU for payload storage.

The interfaces integrated into C-5e's architecture are 10/100/1000 Ethernet MACs (RMII for 10/100, GMII and TBI for 1000), FibreChannel, PCI, serial and Utopia while the line rates supported are OC-3, OC-12 and OC-48.

Programming the C-5e is accomplished through the use of the C programming language and the provided standard API.

The C-5e NP comes in an 840-pin BGA package, with the available operating frequencies being 266 and 300 MHz, with a typical power consumption of 9.2 and 10.6 W respectively.

#### 3.2 Academic Research

In the academic domain, a lot of research has been conducted concerning NPs and their applications in security and routing and of course their processing capabilities. We are going to focus on the PRO3[35] architecture.

#### 3.2.1 The PRO3 Architecture - Overview

The PRO3 is a novel hybrid Network Processing Unit (NPU) architecture, which uses sophisticated interface hardware modules specifically designed from the ground up, special-purpose programmable processors with a low hardware complexity, high-performance general-purpose processors optimized for fast context switching and an on or off-chip control processor. As an overview, the aforementioned hardware modules and special-purpose processors are responsible for handling most of the computation-intensive and real-time protocol functions, while the general-purpose processors handle all the remaining functions, including the higher layer protocols. The on or off-chip control processor is responsible for all the computations that are not on the fast path, such as control-plane or exception processing. The main benefit of this architecture is that it combines wire-speed processing up to the Network layer with best-effort processing for higher layer protocols.

The PRO3 targets systems with requirements such as the following:

- Traffic concetrators supporting enhanced per-flow services, such as security systems performing packet filtering and protocol-aware connection tracking

- Signaling controllers

- Traffic-policing

- Traffic-metering

- Statistics-collecting

It has been designed taking into consideration that a number of functions frequently used in common protocols cannot be executed in an efficient manner using generic RISC processors. These functions are classified as follows:

- Bit and byte-level operations for header parsing and modification

- Efficient memory management

- Complex task and traffic-scheduling algorithms supporting QoS

- Context switching that occurs more frequently than in desktop processors

- Interconnecting a number of different processing modules avoiding the introduction of bottlenecks

The PRO3 resolves these issues by using its special-purpose processors, which are responsible for the header field's exctraction and modification, a sophisticated memory management hardware block and 2 very efficient hardware scheduling modules responsible for fair and balanced packet processing and for controlling data streams generated by the internal modules. In addition, the 2 general-purpose processors are used to complement the special-purpose processors and the hardware modules in the protocol processing parts that they cannot handle in an efficient manner. Communication between the aforementioned hardware parts of the architecture occurs using a 12.8 Gbps internal bus, which is coordinated by a central arbiter.

The PRO3 is implemented in 0.18  $\mu$ m technology, operates at 200 MHz and is packaged in a 1,096-pin Fine-Line Ball Grid Array (FLBGA).

#### 3.2.2 The PRO3 Architecture - In depth look

Now we are going to take a closer look at the building blocks in PRO3's architecture. These are:

- 1. The packet preprocessor,

- 2. the Data Memory Management (DMM) unit,

- 3. the Task Scheduler (TSC),

- 4. the Traffic Scheduler (TRS) and

- 5. the Reprogrammable Pipeline Module (RPM).

The packet preprocessor, the DMM unit and both of the schedulers are optimized for handling a very large number of independent queues while the RPM is very efficient at executing the majority of the required network protocol processing. Concerning the modules' bandwidth, the packet preprocessor, the DMM unit and both of the schedulers can all support a constant rate of 2.5 Gbps of traffic processing under any circumstances, while the RPM supported network rate is application-dependent.

At the following sections we are going to examine each of the aforementioned building blocks.

#### 3.2.2.1 Packet Preprocessor

The Packet Preprocessor block is responsible for looking up of address or other fields used by most network applications. It takes advantage of the features of the programmable field-processing engine which in fact are identical to the ones of the Protocol Processing Engine (PPE) although they are a different entity; it also makes extensive use of an external Ternary Content-Addressable Memory (TCAM) which is used for classification of incoming Protocol Data Units (PDUs).

The tasks performed by this block are header parsing, checksum calculation, classification and generation of a unique flow ID for the incoming PDUs. That flow ID specifies in which queue the packet belongs to — information that is handled by the DMM unit — as well as the internal processing unit needed to handle it and the corresponding software needed by that unit to accomplish the requested task.

#### 3.2.2.2 Data Memory Management unit

The DMM unit implements per-flow queuing for up to 512,000 flows and provides efficient queue handling, variable-length packet storage and access to specific packet segments by the processing engines to the PRO3 architecture. Its main functions are storing incoming traffic, receiving packet data and forwarding that data either to the processing modules or the output interface. It is able to handle both fixed and variable length packets.

Its interface consists of 4 ports, 2 incoming and 2 outgoing with a bandwidth of 2.5 Gbps each. One port is used to receive data from the network, one to transmit data to the network, and a bidirectional port for exchanging data from and to the internal bus.

In order to achieve the total aggregate througput of 10 Gbps, the DMM unit employs an optimized free list organization and memory access reordering. By using 2 separate free lists the memory accesses are reduced during buffer releasing by 70% during writes and 46% during reads. Also, by reordering the read and write commands — and subsequently their corresponding memory accesses — a 30% reduction in mean access latency is achieved.

#### 3.2.2.3 Scheduler modules

A need for scheduling arises since the RPM engines sometimes process packets at a lower rate than that of the packet arrival rate. To face this issue, the packets need to be stored and scheduled for processing once the target processing module is available. Concerning incoming traffic, the TSC maintains priority queues in order to schedule the forwarding of packets for processing according to a configurable priority per flow, which is set by the administrator. On the other hand, handling the scheduling of outgoing traffic is the TRS, which shapes transmitted traffic according to traffic management specifications. The overall scheduling is controlled by command and status messages issued by the DMM, the CPU and the Packet Preprocessor. These commands are routed to the appropriate scheduler through the Service and Redirect block.

Multiple flows are multiplexed round-robin in one scheduling queue. The TSC supports a total of 32 hierarchical scheduling queues, where the first queue is treated with highest priority than the others. The rest of the queues can be treated equally or by dividing them into 2 groups with different priorities. The TSC uses a connection table to store per-flow state information and connection-specific parameters such as the flow's priority weight. When flows map to the same scheduling queue, they are stored in a linked list. The TRS supports 32 scheduling queues as well and uses the same data structures as the TSC.

#### 3.2.2.4 Reprogrammable Pipeline Module

This is the block that is mainly responsible for protocol processing in the PRO3 architecture. It is comprised of 3 units: the PPE, the Field Exctraction Engine (FEX) and the Field Modification Engine (FMO). These units form a 3-stage pipeline that constitutes the PRO3's software-processing heart.

The PPE lies in the core of the RPM and contains a RISC-CPU core and external control logic. The RISC-CPU core is a Hyperstone E1-32XS which is modified by partitioning its registers into two sets, where the first one is accessible by the CPU while the other by the PPE control logic. The processor switches register sets and informs the external logic — via a special instruction — once it has finished processing a packet. Direct Input/Output (I/O) is feasible through the processor's dual-port data memory. Network processing is substantially accelerated since I/O operations and packet processing can be performed concurrently, thus these actions' latency is partly hidden.

The FEX is responsible for parsing packet headers and subsequently loading the required protocol fields to the PPE in order to be processed. Its instruction set consists of 9 basic instructions and 4 commands (instructions with no arguments) which operate on a First-In, First-Out (FIFO) buffer of 32-bit words. Supported by the instruction set are variable-length field extraction, backward and forward movement in the data FIFO, conditional branches — which are based on extracted fields and header parsing — and addition.

The FMO is tasked with packet construction or reconstruction and header modification. Its own instruction set includes 16 instructions and 6 commands, which support field extraction and insertion/modification.

The FEX and FMO use only 4 and 5 generic registers respectively, and additionally a special-purpose register and a Data Pointer. Their instructions can be combined and executed in parallel with any of the commands, thus reducing code size and increasing performance. It is also worth mentioning that the FEX and FMO are optimized for bit and byte processing.

#### 3.2.3 The PRO3 Architecture - Development Tools

On the software development side, the PRO3 is accompanied by a development suite used for configuring registers, initializing memory locations and loading software modules into the PRO3. The user is provided with a configuration GUI, which contains a separate page for each of the PRO3's hardware modules. On these pages, the user is able to configure or develop code for that specific module.

In its core, the development suite contains a Configuration Library (CL) which maintains an internal register map of the whole chip. The aforementioned GUI utilizes a set of functions implemented and exported by the CL in order to read and write the values of configuration registers and internal memory locations. The CL is also responsible for reading, parsing and compiling the configuration files and software programs for all of PRO3's processing units. Lastly, it maintains a TCP-based session with a configuration server which is running either on the on-chip or on-board control processor.

The development suite can be used to configure either the actual PRO3 chip, when connected with a development board, or a hardware description language model or netlist.

## Chapter 4

## Architecture

### 4.1 Virtex-5 FPGA Embedded Tri-mode Ethernet MAC

The Xilinx Virtex-5 (V5) FPGA board has an embedded Tri-mode Ethernet MAC (TEMAC) Wrapper [36, 37, 38], which is the base of our design and provides us with fully-fledged Physical and Data Link layers (see figure 4.1). Its key features [36] are:

- Fully integrated 10/100/1000 Mbps Ethernet MACs

- Designed to the IEEE standard 802.3-2002 specification

- Configurable full-duplex operation in 10/100/1000 Mbps

- Configurable half-duplex operation in 10/100 Mbps

- Management Data Input/Output (MDIO) interface to manage objects in the Physical layer

- User-accesible raw statistic vector outputs

- Support for VLAN frames

- Configurable IFG adjustment in full-duplex operation

- Configurable in-band Frame Check Sequence (FCS) field passing on both transmit and receive paths

- Auto padding on transmit and stripping on receive paths

Figure 4.1: Virtex-5 Tri-mode Ethernet MAC-supplied OSI Layers

- Configured and monitored through a host interface

- Hardware-selectable Device Control Register (DCR) bus or generic host bus interface

- Configurable flow control through Ethernet MAC PAUSE frames; symmetrically or assymetrically enabled

- Configurable support for jumbo frames of any length

- Configurable receive address filter for unicast, general and broadcast addresses

- Media Independent Interface (MII), Gigabit Media Independent Interface (GMII) and Reduced Gigabit Media Independent Interface (RGMII)

- 1000BASE-X Physical Coding Sublayer (PCS) and Physical Medium Attachment (PMA) sublayer included for use with the Virtex-5 RocketIO serial transceivers to provide a complete on-chip 1000BASE-X implementation

• Serial Gigabit Media Independent Interface (SGMII) supported through the RocketIO serial transceivers' interfaces to external copper Physical layer for full-duplex operation

It is able to provide 2 Ethernet MACs, which can be configured independently. A comprehensive list of some of the available configuration options along with all the possible choices for each of them is given in table 4.1.

| Option                            | Choices                                  |

|-----------------------------------|------------------------------------------|

|                                   | Tri-Speed                                |

| Ethernet Speed                    | $1000 { m ~Mbps}$                        |

|                                   | 10/100  Mbps                             |

|                                   | MII                                      |

|                                   | GMII                                     |

| Physical Layer Interface          | RGMII                                    |

|                                   | SGMII                                    |

|                                   | 1000BASE-X PCS/PMA (fibre)               |

| Transmit (Tx) Flow Control Enable | True/False                               |

| Receive (Rx) Flow Control Enable  | True/False                               |

| Jumbo Frame Enable                | True/False                               |

| In-band FCS Enable                | True/False                               |

| VLAN Enable                       | True/False                               |

| IFG Adjust Enable (Tx only)       | True/False                               |

| Rx Disable Length (Rx only)       | True/False                               |

| Address Filter Enable             | True/False; if True, specify MAC Address |

Table 4.1: Selection of configuration options for Virtex-5 FPGA Tri-mode Ethernet MAC

Using Xilinx's CORE Generator software, the V5 TEMAC is configured and the VHDL files that are needed in order to use it are generated; apart from the VHDL files, an example design is also generated, so one can use the TEMAC immediately. This example design connects the TEMAC with a client interface consisting of a Rx and a Tx FIFO, which are connected through a LocalLink Interface (LL) with an Address Swap Module (ASM). The example design functions as a loopback that receives frames from the TEMAC, stores them in the Rx FIFO, sends them through the LL to the ASM, which after exchanging the Destination MAC Address with the Source MAC Address, sends the modified frame to the Tx FIFO, which in turn sends the frame to the TEMAC for transmission back through the board's network adapter.

The LL is especially useful, since it renders communication with the TEMAC quite easier when compared to directly interfacing with the TEMAC component. The LL is described in table 4.2, where signals ending with "\_n" are active low.

| Path                    | Port Name             | Type       | Size (bits) |

|-------------------------|-----------------------|------------|-------------|

|                         | rx_ll_clock           | in         | 1           |

|                         | $rx\_ll\_reset$       | $_{ m in}$ | 1           |

|                         | rx_ll_data            | out        | 8           |

| Deseive (D)             | rx_ll_sof_n           | out        | 1           |

| Receive $(\mathbf{Rx})$ | rx_ll_eof_n           | out        | 1           |

|                         | rx_ll_src_rdy_n       | out        | 1           |

|                         | rx_ll_dst_rdy_n       | in         | 1           |

|                         | $rx_ll_fifo_status$   | out        | 4           |

|                         | tx_ll_clock           | in         | 1           |

|                         | $tx\_ll\_reset$       | $_{ m in}$ | 1           |

|                         | $tx\_ll\_data$        | $_{ m in}$ | 8           |

| Transmit $(Tx)$         | $tx_ll_sof_n$         | $_{ m in}$ | 1           |

|                         | $tx_ll_eof_n$         | $_{ m in}$ | 1           |

|                         | tx_ll_src_rdy_n       | $_{ m in}$ | 1           |

|                         | $tx\_ll\_dst\_rdy\_n$ | out        | 1           |

Table 4.2: LocalLink Interface

To get a better understanding of the way the LL operates, we are going to present a simple example (see figure 4.2). In order to exchange data through the LL, both src\_rdy\_n and dst\_rdy\_n have to be asserted at the same time; only then is data transferred across the LL. Should one of these two signals be deasserted at any time, transfer is paused, thus achieving flow control. The sof\_n signal is asserted only at the beginning of the frame and respectively, the eof\_n signal only at the end of the frame.

Figure 4.2: Frame Transfer with Flow Control across LocalLink Interface

# 4.2 Our Design

#### 4.2.1 Configuration of the Tri-mode Ethernet MAC

The TEMAC used in our design is configured to have a single MAC, Trispeed setting for the Ethernet speed, a SGMII Physical Layer interface, flow control for both Rx and Tx and an Address Filter set to a MAC address of "AA:BB:CC:DD:EE:FF".

The reason we selected a Tri-speed setting, is mainly to be compatible with any network adapter we connect the design to, without the need to regenerate the TEMAC for a different speed setting. The SGMII Physical layer interface was selected since it radically reduces I/O count when compared to the other choices and of course because regular copper Ethernet cables are widely available when compared to fibre optic cables (thus ruling-out the 1000BASE-X PCS/PMA interface). Finally, the Address Filter is used so that our design will only process frames containing the specified MAC Destination address.

By selecting not to enable In-band FCS passing, we let the TEMAC check the CRC field of the frame and if it is erroneous, it will not pass it along to our design. Moreover, this makes the TEMAC calculate the CRC field and add it to the frame before transmission. By not disabling the Rx length checking, the TEMAC is responsible for determining whether we have a length or type field and if it is a length field, to check if the value found in that field is consistent with the actual length of data in the frame. If it is not, then the frame is erroneous and so it is not passed from the TEMAC to our design. The latter choices take care of the necessary frame checks.

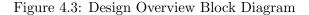

Our own design is implemented on the top level of the example design, as shown in figure 4.3, since we take advantage of the LocalLink Interface (see table 4.2) in order to communicate in a more high-level and understandable manner with the TEMAC.

#### 4.2.2 Architecture - Overview

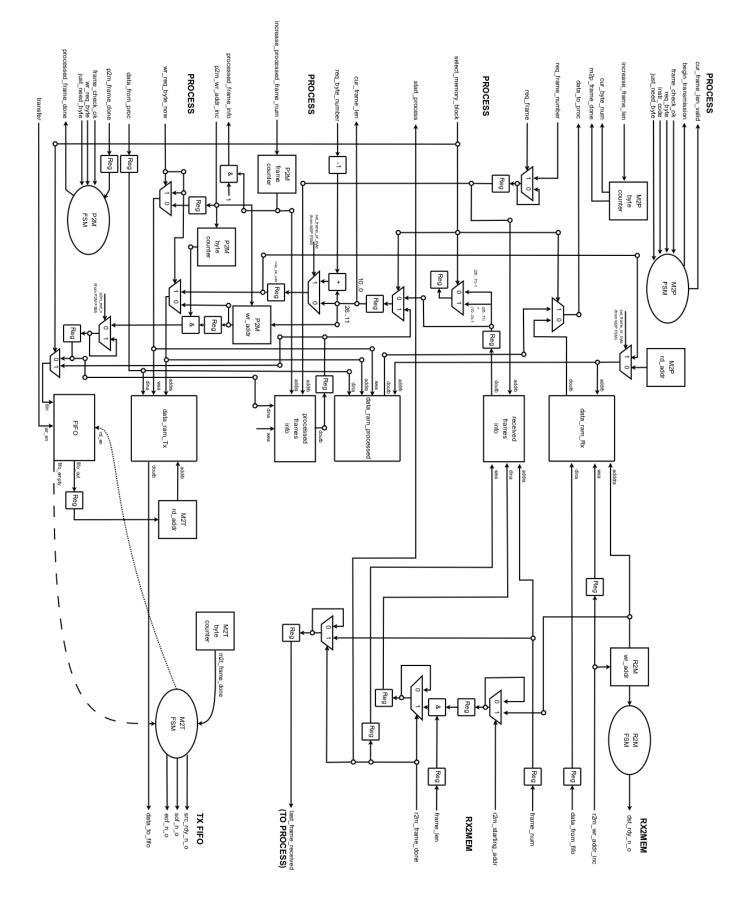

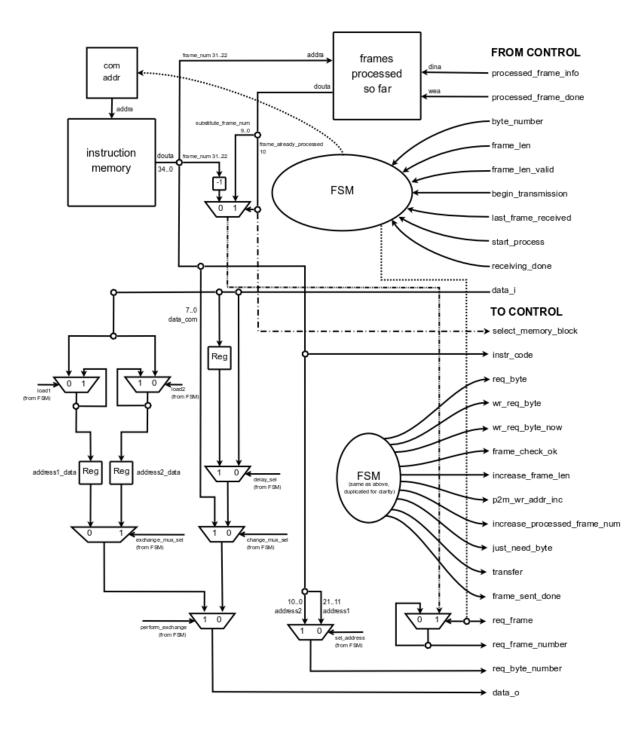

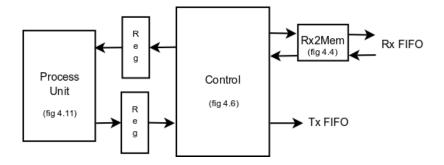

The Network Processor that we designed is implemented in a modular architecture with the datapath flow being as follows: connected with the Rx Client FIFO of the example design is the Rx2Mem module (an abbreviated version of Receive-to-Memory), whose main objective is to pass along frame data as it is received from the FIFO to the Control module, to provide the frame's length, once it has finished transmission and to provide the number of the currently received frame. The Control module is essentially the module where we store data and information about the frames we have received and processed, before forwarding them to either the Process module or the Tx client FIFO. The Process module is the heart of our Network Processor, since it is the module where frame processing occurs, according to the software program loaded in its instruction memory. After processing has finished, frame data is sent from the Process module back to the Control module, where it is stored either to be processed furthermore or to be transmitted to the Tx FIFO.

The commands supported by our NP are listed in table 4.3, showcasing their syntax and their corresponding opcode.

| Instruction | Syntax                          | Opcode |

|-------------|---------------------------------|--------|

| Add         | FrameNumber, Address1, Data     | 000    |

| Change      | FrameNumber, Address1, Data     | 001    |

| Compare     | FrameNumber, Data               | 100    |

| Exchange    | FrameNumber, Address1, Address2 | 101    |

| Remove      | FrameNumber, Address1           | 010    |

| Repor       | FrameNumber, Address1           | 011    |

| Transfe     | FrameNumber                     | 110    |

Table 4.3: Command Syntax and Opcodes

The functions performed by each command are:

- Add adds Data in position Address1 in the frame FrameNumber

- **Change** replaces data in position Address1 of frame FrameNumber with Data

- **Compare** compares (searches) frame FrameNumber for Data and returns byte number, if found

- **Exchange** exchanges data from position Address1 with data from position Address2 in frame FrameNumber

- Remove removes data in position Address1 from frame FrameNumber

**Report** reports data in position Address1 from frame FrameNumber

Transfer commences the transmission of frame FrameNumber

Commands refer to frames in a sequential manner and a Non-Transfer policy is followed. In order to make things a little bit clearer, the sequential manner of commands refers to the fact that commands are structured in a way that FrameNumbers are sequential: if a batch of commands refer to frame five, all subsequent commands must refer to either frame five or greater. The Non-Transfer policy means that a frame is transferred exclusively with the use of the Transfer command. So, if a frame does not have a Transfer command associated with it, no transmission of this frame's data is going to occur, regardless of whether other commands have processed it or not.

#### 4.2.3 Architecture - In-depth

Now we are going to provide an in-depth look at each of the modules of the architecture, their interfaces, their inside structure and their operation.

#### 4.2.3.1 Rx2Mem

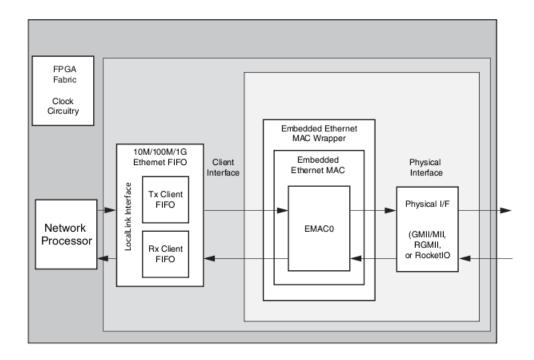

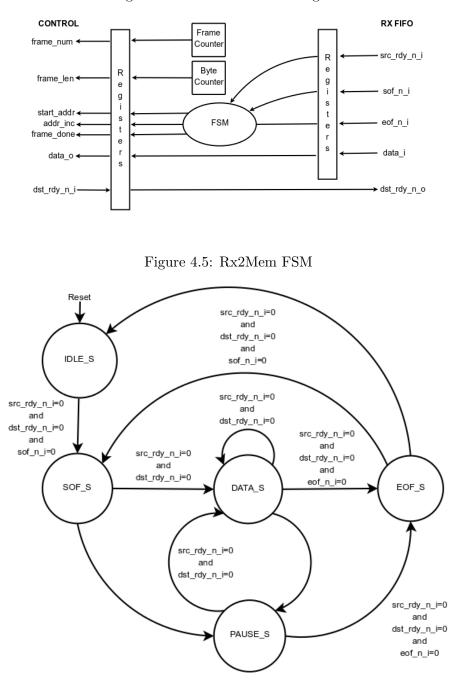

The Rx2Mem module is the first module of our design, whose purpose is to forward frame data received through the LL to the Control module, to calculate the length of each frame and to keep a count of all the frames it has received. Presented in table 4.4 is the module's interface, while in figure 4.4 a block diagram is given.