### **Technical University of Crete**

Department of Electronic and Computer Engineering Electronics Laboratory

### Design of a Variable Gain Amplifier (VGA) for a RF Receiver with DC-Offset Correction in 90nm CMOS Technology

A Thesis

by

### Vasileios Mylonakis

### Approved by:

Bucher Matthias, Assistant Professor (Supervisor) Kalaitzakis Konstantinos, Professor Balas Costas, Associate Professor

Chania, September 2011

### ABSTRACT

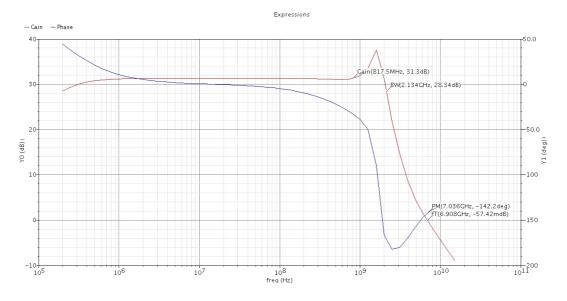

The purpose of this thesis is the design of a variable gain amplifier (VGA) for a Radio-Frequency (RF) receiver, providing simultaneously a noticeable gain range of approximately 40dB (-10.6dB~31.3dB) and achieving a 3dB bandwidth of 2.1GHz.The VGA is comprised of a 3-stage modified Cherry-Hooper amplifier while the embedded negative feedback deals with the DC-Offset Correction. One main feature of the Cherry-Hooper amplifier, which is the main building block of the circuit, is that is inductorless which helps in saving chip space. Along with that, inverse scaling technique is employed resulting in broadening the overall bandwidth if the VGA and reducing the power consumption. In the first Chapter an introduction to RF and wireless technology is made, emphasizing on the RF interface. Besides that, design issues and receiver's concepts are discussed. In the second Chapter VGA concepts are discussed, while in the third Chapter VGA design procedure is thoroughly described. Finally at fourth and final Chapter simulation results are shown with interesting conclusions respectively.

### ACKNOWLEDGEMENTS

This work was implemented at the Electronics Laboratory of Technical University of Crete under the supervision of Assistant Professor Matthias Bucher during the academic year 2009-10.

First of all, I would like to thank Matthias Bucher for giving me the opportunity to work on this project and pushing my interest towards the field of microelectronics. The meetings I had with him gave me invaluable insights into analog circuit design.

Moreover, I would like to express my gratitude to Professors Kalaitzakis Konstantinos and Balas Costas for being a part of my thesis evaluation committee .I acknowledge, especially, the contribution of PhD candidate Antonopoulos Aggelos and postgraduate students Dimakos Athanasios and Makris Nikos for their contribution in the completion of this project. Their help with the troubleshooting of the circuit and their suggestions for the design were of significant importance. Special thanks to Psillos Dimitrios PhD candidate at Electronics department of National Technical University of Athens, who in spite of his busy schedule, he always found time to answer my questions.

Finally, my deepest gratitude to my parents whose understanding and support made this thesis feasible. I would also like to thank my friends and family for their constant encouragement and patience.

# **TABLE OF CONTENTS**

### CHAPTER

| 1. | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | 1.1 The RF Interface 13                                                                                                                                                                                                                                                                                                                                                                                                        |

|    | 1.1.1 Small Desired Signals13                                                                                                                                                                                                                                                                                                                                                                                                  |

|    | 1.1.2 Large Interfering Signals14                                                                                                                                                                                                                                                                                                                                                                                              |

|    | 1.1.3 Adjacent Channel Interference                                                                                                                                                                                                                                                                                                                                                                                            |

|    | 1.2 Design Bottleneck16                                                                                                                                                                                                                                                                                                                                                                                                        |

|    | 1.3 Receiver's Concepts                                                                                                                                                                                                                                                                                                                                                                                                        |

|    | 1.3.1 Basics                                                                                                                                                                                                                                                                                                                                                                                                                   |

|    | 1.3.2 Sensitivity18                                                                                                                                                                                                                                                                                                                                                                                                            |

|    | 1.3.3 Noise Figure                                                                                                                                                                                                                                                                                                                                                                                                             |

|    | 1.3.4 Selectivity                                                                                                                                                                                                                                                                                                                                                                                                              |

|    | 1.3.5 Main Blocks20                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2. | FUNDAMENTALS OF VGA DESIGN21                                                                                                                                                                                                                                                                                                                                                                                                   |

|    | 2.1 Frequency Response and Stability of Amplifiers21                                                                                                                                                                                                                                                                                                                                                                           |

|    | 2.1.1 Miller Effect                                                                                                                                                                                                                                                                                                                                                                                                            |

|    | 2.1.2 Association of poles with nodes                                                                                                                                                                                                                                                                                                                                                                                          |

|    | 2.1.3 Multi-pole Systems                                                                                                                                                                                                                                                                                                                                                                                                       |

|    | 2.2 Gain and Bandwidth Specifications                                                                                                                                                                                                                                                                                                                                                                                          |

|    | 2.2.1 Cascoding                                                                                                                                                                                                                                                                                                                                                                                                                |

|    | 2.2.2 Gain boosting in differential amplifiers with diode                                                                                                                                                                                                                                                                                                                                                                      |

|    | connected loads                                                                                                                                                                                                                                                                                                                                                                                                                |

|    | 2.3 Frequency Compensation                                                                                                                                                                                                                                                                                                                                                                                                     |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                |

|    | 2.3.1 Single-stage amplifier review                                                                                                                                                                                                                                                                                                                                                                                            |

|    | 2.3.1 Single-stage amplifier review302.3.2 Two-stage amplifier with Simple Miller                                                                                                                                                                                                                                                                                                                                              |

|    | 2.3.2 Two-stage amplifier with Simple Miller                                                                                                                                                                                                                                                                                                                                                                                   |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                |

|    | 2.3.2 Two-stage amplifier with Simple Miller                                                                                                                                                                                                                                                                                                                                                                                   |

|    | 2.3.2 Two-stage amplifier with Simple Miller<br>Compensation (SMC)                                                                                                                                                                                                                                                                                                                                                             |

|    | <ul> <li>2.3.2 Two-stage amplifier with Simple Miller</li></ul>                                                                                                                                                                                                                                                                                                                                                                |

|    | <ul> <li>2.3.2 Two-stage amplifier with Simple Miller</li></ul>                                                                                                                                                                                                                                                                                                                                                                |

|    | 2.3.2 Two-stage amplifier with Simple Miller                                                                                                                                                                                                                                                                                                                                                                                   |

|    | 2.3.2 Two-stage amplifier with Simple Miller         Compensation (SMC)         .30         2.3.3 Two-stage amplifier with Simple Miller         Compensation with Nulling Resistor (SMCNR)         .33         2.3.4 Pole-splitting and zero-cancellation         .34         2.4 Gain Varying Techniques         .37         2.5 Harmonic Distortion and DC Offset                                                           |

|    | 2.3.2 Two-stage amplifier with Simple Miller       30         Compensation (SMC)       30         2.3.3 Two-stage amplifier with Simple Miller       30         Compensation with Nulling Resistor (SMCNR)       33         2.3.4 Pole-splitting and zero-cancellation       34         2.4 Gain Varying Techniques       37         2.5 Harmonic Distortion and DC Offset       40         2.5.1 Harmonic Distortion       40 |

|    | 2.3.2 Two-stage amplifier with Simple Miller                                                                                                                                                                                                                                                                                                                                                                                   |

|    | 2.3.2 Two-stage amplifier with Simple Miller                                                                                                                                                                                                                                                                                                                                                                                   |

|    | 2.3.2 Two-stage amplifier with Simple Miller                                                                                                                                                                                                                                                                                                                                                                                   |

|    | 2.3.2 Two-stage amplifier with Simple Miller                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                    | Page |

|----------------------------------------------------|------|

| 3. DESIGN OF THE VARIABLE GAIN AMPLIFIER           | 51   |

| 3.1 Blocks of the VGA                              | 52   |

| 3.1.1 High-pass Filter                             | 52   |

| 3.1.2 VGA Chain                                    |      |

| 3.1.2.1 Cherry Hooper amplifier                    | 54   |

| 3.1.2.2 Modified Cherry Hooper amplifier           | 61   |

| 3.1.2.3 VGA chain build-up                         |      |

| 3.1.3 Low-pass filter with feedback amplifier      |      |

| 3.2 Techniques utilized during design              | 71   |

| 3.2.1 Inverse Scaling                              |      |

| 3.2.2 Active Negative Feedback                     | 72   |

| 3.3 Design Optimization                            |      |

| 3.3.1 Inversion Coefficient-Performance Trade-offs | 73   |

| 3.3.2 MOSFET's Inversion Areas                     | 74   |

| 3.3.3 Optimization with design parameters          | 76   |

| 4. SIMULATION RESULTS                              | 77   |

| 4.1 Gain-Phase_slew Rate Figures                   |      |

| 4.2 DC-Offset, Noise Figures                       | 79   |

| 4.3 Worst Case Assumptions                         |      |

| 5. CONCLUSIONS                                     |      |

| 5.1 System's Performance                           | 83   |

| 5.2 Future Work and Suggestions                    |      |

| 5.3 Appendix                                       |      |

| REFERENCES                                         | 85   |

# LIST OF TABLES

|          |                                             | Page |

|----------|---------------------------------------------|------|

| TABLE 1  | HPF design values                           | 63   |

| TABLE 2  | Values-dimensions of 1 <sup>st</sup> stage  |      |

| TABLE 3  | 1 <sup>st</sup> stage efficiency            |      |

| TABLE 4  | Values-dimensions of 2 <sup>nd</sup> stage  | 66   |

| TABLE 5  | 2 <sup>nd</sup> stage efficiency            | 66   |

| TABLE 6  | Values-dimensions of 3 <sup>rd</sup> stage  |      |

| TABLE 7  | 3 <sup>rd</sup> stage efficiency            |      |

| TABLE 8  | LPF- Feedback amplifier design values       |      |

| TABLE 9  | System's Measured Performance               |      |

| TABLE 10 | Performance Comparison of VGA Architectures |      |

# LIST OF FIGURES

| Page                                                                              |

|-----------------------------------------------------------------------------------|

| Fig.1 A super heterodyne receiver's RF interface13                                |

| Fig.2 A digital direct conversion transmitter's RF interface                      |

| Fig.3 Spectrum of a narrowband signal passing through a nonlinear                 |

| circuit15                                                                         |

| Fig.4 RF and baseband processing in a transceiver16                               |

| Fig.5 Disciplines required in RF design17                                         |

| Fig.6 RF design hexagon17                                                         |

| Fig.7 Analog design octagon21                                                     |

| Fig.8 Miller effect on a floating impedance                                       |

| Fig.9 Voltage amplifier with negative feedback example                            |

| Fig.10 Typical case for valid application of Miller's theorem22                   |

| Fig.11 Cascade of amplifiers23                                                    |

| Fig.12 Example of interaction between nodes23                                     |

| Fig.13 Bode plots of loop gain for a two-pole system24                            |

| Fig.14 Bode plots of loop gain for a three-pole system25                          |

| Fig.15 Differential amplifier with active load                                    |

| Fig.16 Cascode amplifier                                                          |

| Fig.17 Folded cascode amplifier                                                   |

| Fig.18 Addition of current sources to increase the gain of differential amplifier |

| with diode-connected load                                                         |

| Fig.19 SMC amplifier                                                              |

| Fig.20 Frequency response of a SMC amplifier                                      |

| Fig.21 SMCNR amplifier                                                            |

| Fig.22 Two-stage op amp                                                           |

| Fig.23 Bode plots of loop gain of two-stage op amp                                |

| Fig.24 Miller compensation of a two-stage op amp                                  |

| Fig.25 Pole splitting as a result of Miller compensation                          |

| Fig.26 Simplified circuit of a two-stage op amp with the addition of $R_z$ .36    |

| Fig.27 Variable gain amplifier with MOS as a variable degeneration                |

| resistor                                                                          |

| Fig.28 Variable gain amplifier based on current steering technique39              |

| Fig.29 Input referred offset of a two stage amplifier42                           |

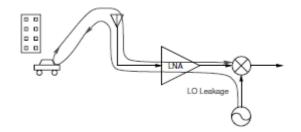

| Fig.30 Self-mixing due to LO leakage43                                            |

| Fig.31 Self-mixing due to LO leakage radiated44                                   |

| Fig.32 Self-mixing due to interferer leakage44                                    |

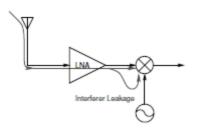

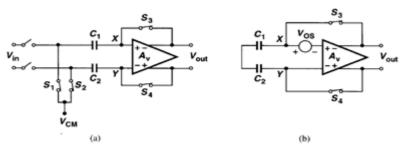

| Fig.33 (a)Simple amplifier with capacitive coupling at output, (b) circuit        |

| of (a)with its inputs and outputs shorted, (c) proper setting of the              |

| common- mode level during offset cancellation                                     |

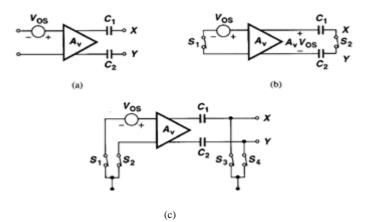

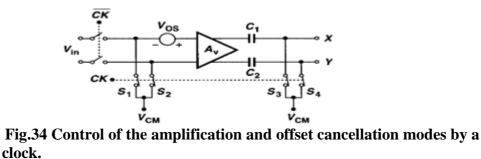

| Fig.34 Control of the amplification and offset cancellation modes by              |

| a clock45                                                                         |

| Fig35 (a) Input offset storage, (b) circuit of (a) in the offset cancellation     |

| mode                                                                              |

|                                                                                   |

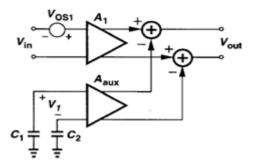

| Fig.36 Additional of an auxiliary stage to remove the offset46           |

|--------------------------------------------------------------------------|

| Fig.37 Auxiliary amplifier placed in a feedback loop47                   |

| Fig.38 Previous Circuit using G <sub>m</sub> and R stages47              |

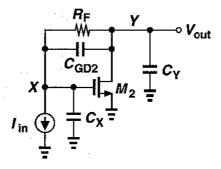

| Fig.39 Transimpedance amplifier48                                        |

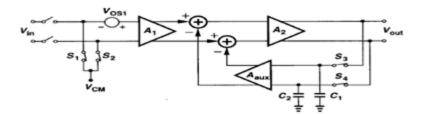

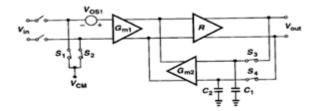

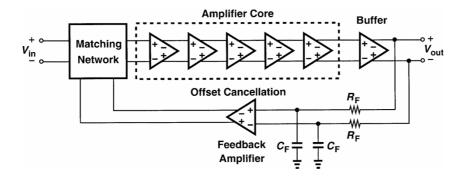

| Fig.40 Active Feedback Architecture48                                    |

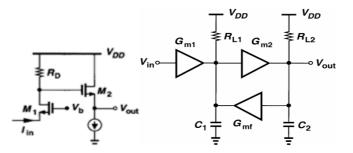

| Fig.41 Active-feedback cell realization                                  |

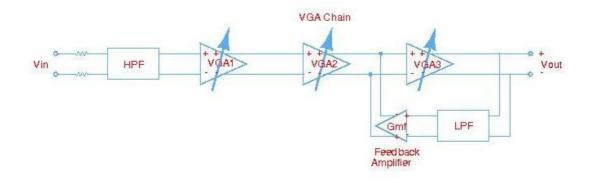

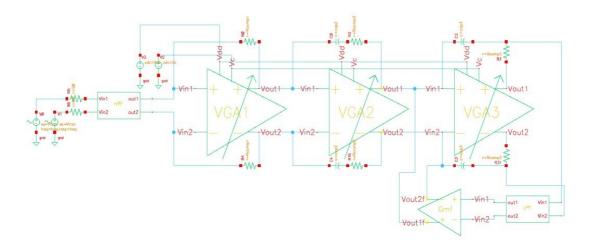

| Fig.42 VGA Architecture                                                  |

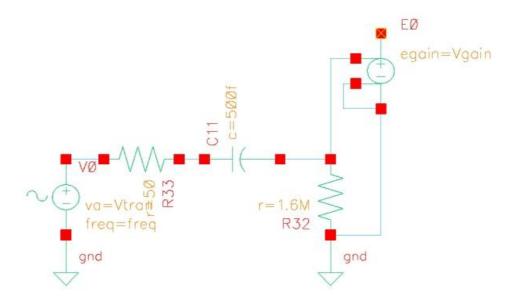

| Fig.43 HPF with 50 $\Omega$ resistance at transmission line and a source |

| follower                                                                 |

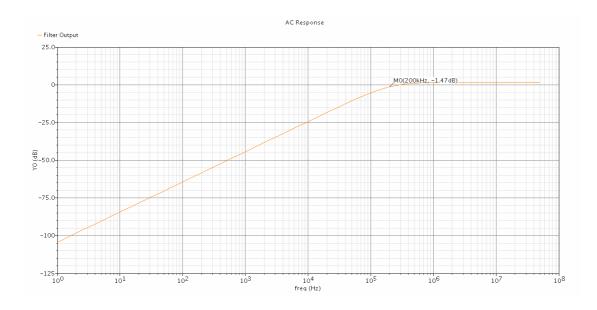

| Fig.44 Frequency Response of the HPF with 200 KHz cut-off frequency53    |

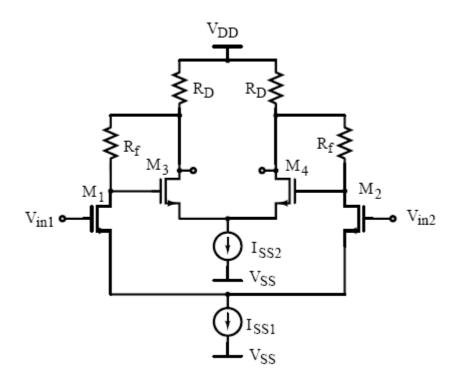

| Fig.45 Cherry Hooper amplifier54                                         |

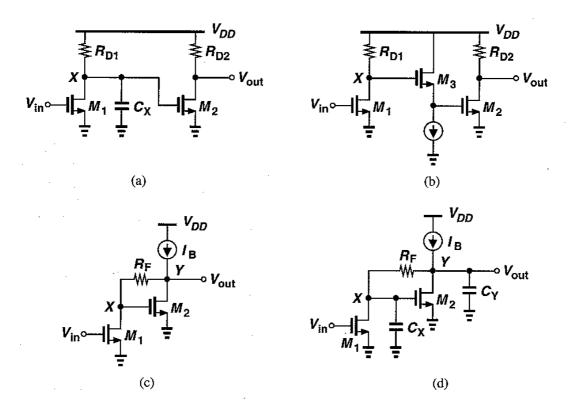

| Fig.46 (a) Cascade of two CS stages,(b) Employment of a source follower  |

| voltage buffer,(c)Two CS stages with feedback resistance,                |

| (d) previous circuit with node capacitances55                            |

| Fig.47 CS stage with resistive feedback                                  |

| Fig.48 Equivalent circuit of the Cherry Hooper amplifier57               |

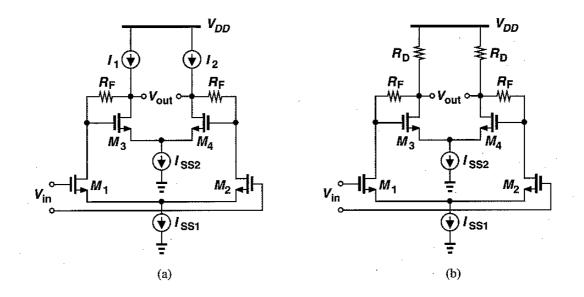

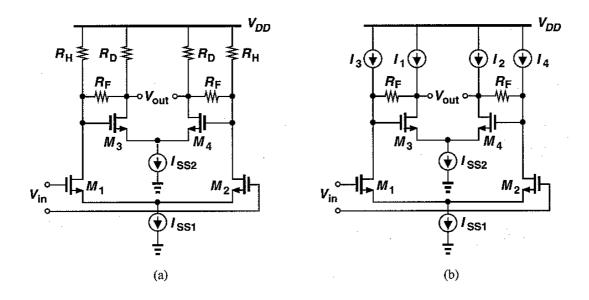

| Fig.49 Cherry Hooper amplifier with differential pair with               |

| (a) current-source loads and (b) resistive loads                         |

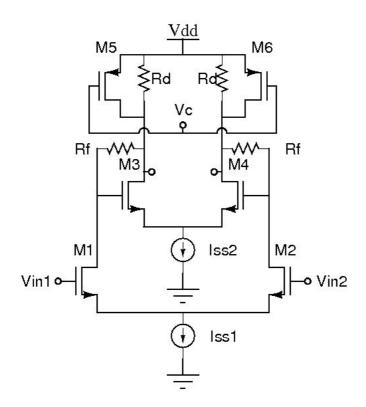

| Fig.50 Modified Cherry Hooper amplifier with (a) resistive loads and     |

| (b) current-source loads                                                 |

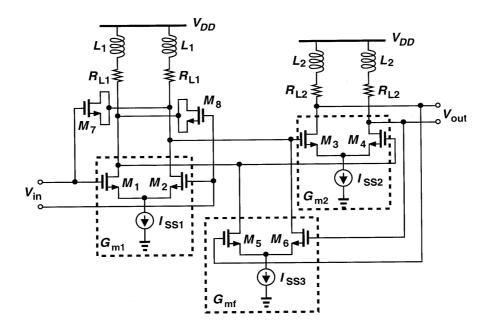

| Fig.51 Modified Cherry Hooper amplifier61                                |

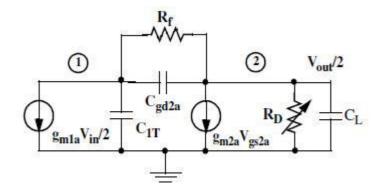

| Fig.52 Simplified small-signal half circuit                              |

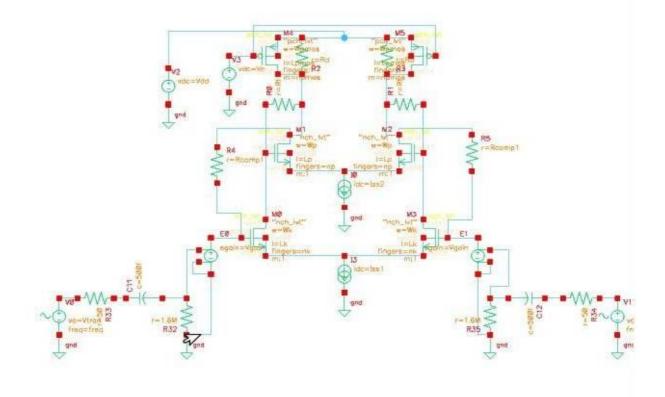

| Fig.53 Amplifier's 1 <sup>st</sup> stage schematic63                     |

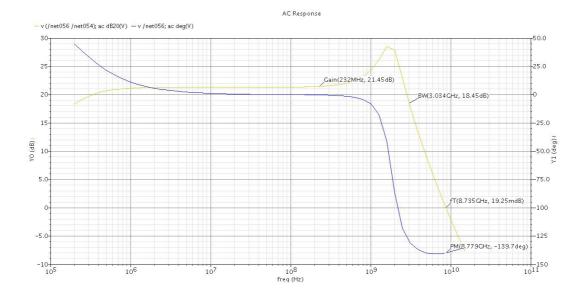

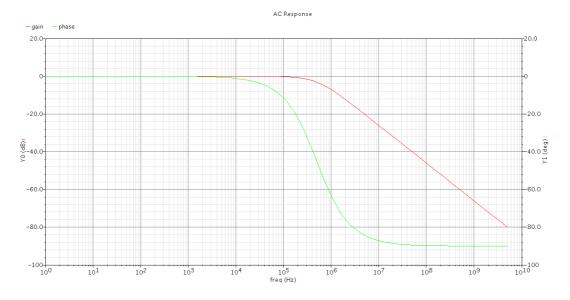

| Fig.54 Frequency Response of 1 <sup>st</sup> stage amplifier64           |

| Fig.55 Amplifier's 1 <sup>st</sup> stage schematic                       |

| Fig.56 Frequency Response of 2 <sup>nd</sup> stage amplifier             |

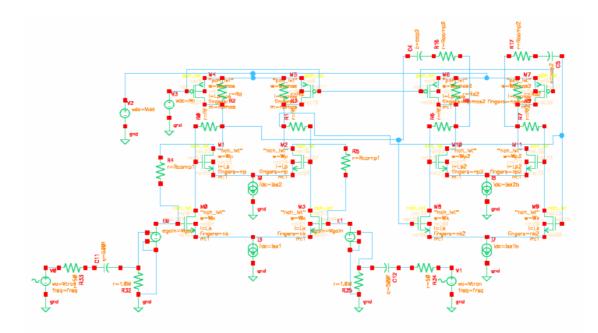

| Fig.57 Amplifier's 3 <sup>rd</sup> stage schematic67                     |

| Fig.58 Frequency Response of 3 <sup>rd</sup> stage amplifier             |

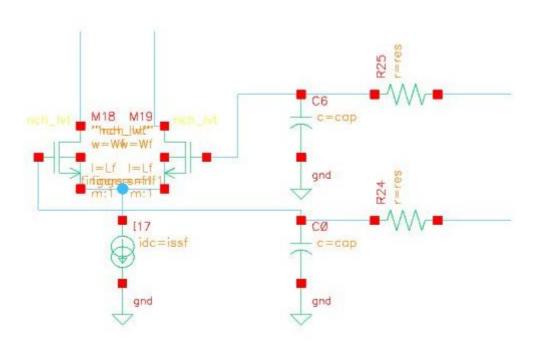

| Fig.59 Feedback amplifier's and LPF schematic                            |

| Fig.60 Frequency Response of LPF and feedback amplifier70                |

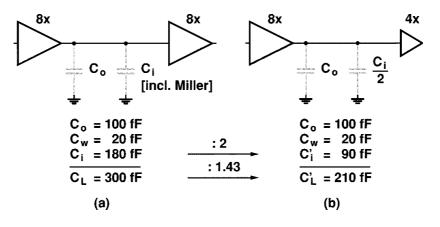

| Fig.61 (a) no scaling (b) inverse scaling                                |

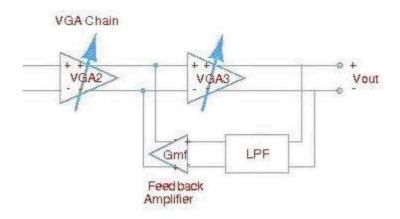

| Fig.62 DC-Offset Correction network72                                    |

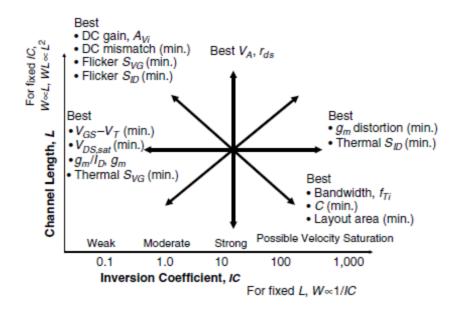

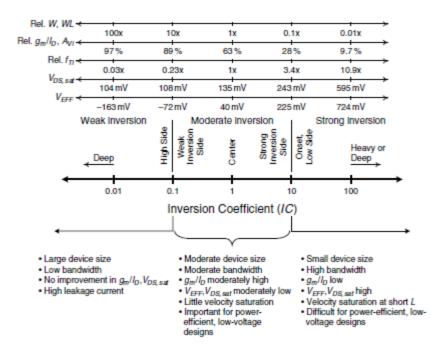

| Fig.63 Trade-offs at MOSFET operating plane74                            |

| Fig.64 Trade-offs of MOSFET's inversion areas75                          |

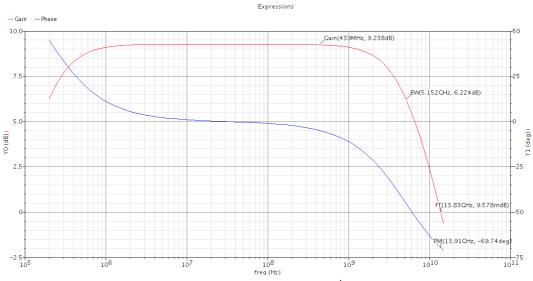

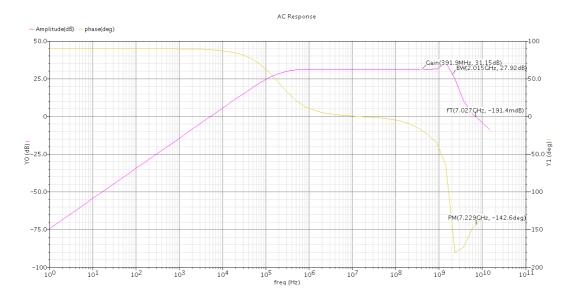

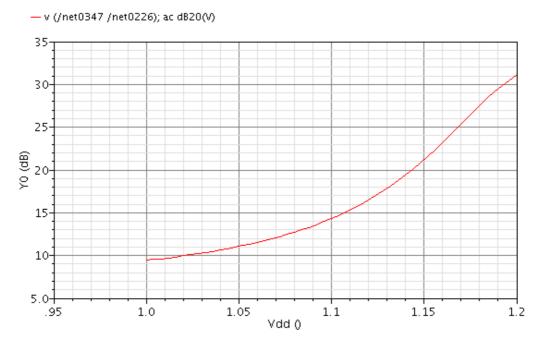

| Fig.65 Gain-Bandwidth of the VGA77                                       |

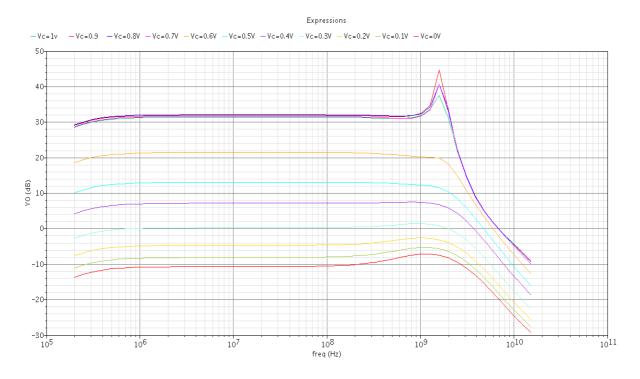

| Fig.66 Gain values when sweeping V <sub>c</sub>                          |

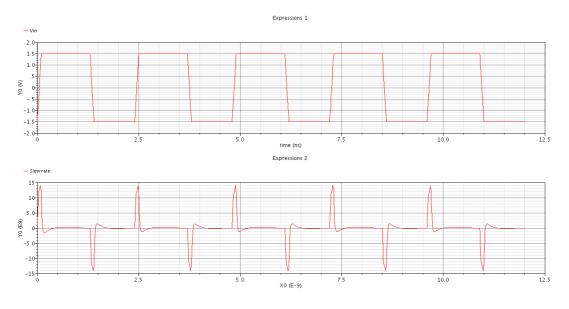

| Fig.67 Slew rate of the VGA                                              |

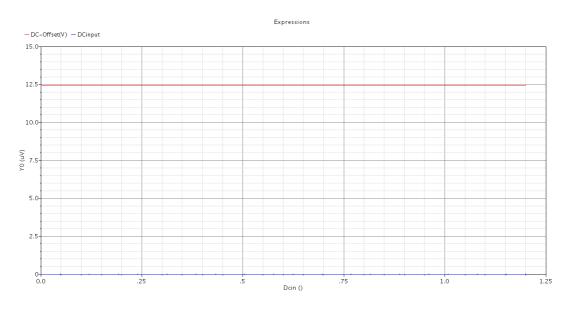

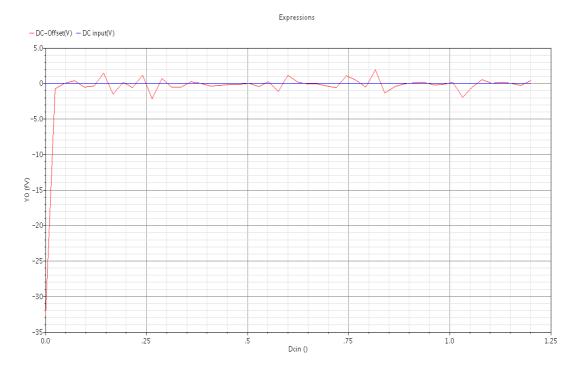

| Fig.68 DC-offset output without the correction network79                 |

| Fig.69 DC-offset output with the correction network80                    |

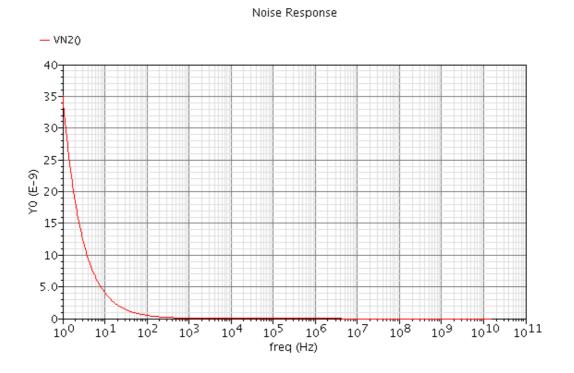

| Fig.70 Squared output noise of the system80                              |

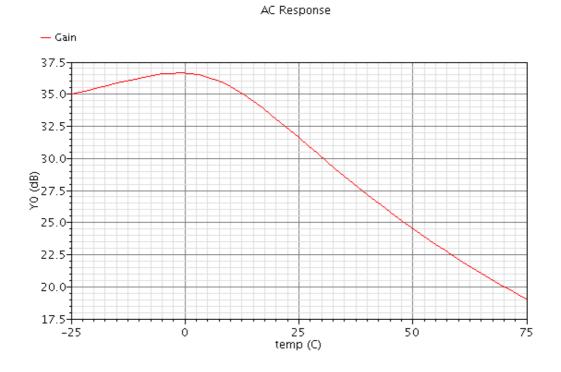

| Fig.71 Worst case assumption: gain versus temperature                    |

| Fig.72 Worst case assumption: voltage drop82                             |

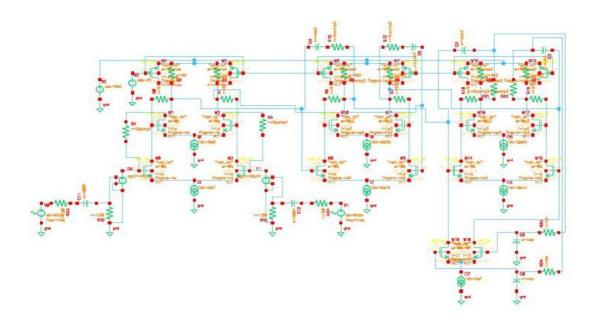

| Fig.73 VGA Hierarchy Design                                              |

|                                                                          |

## CHAPTER 1

### **INTRODUCTION**

The insatiable requirement for high-speed real-time computer connectivity anywhere, at any time, fuelled by the wide-spreading acceptance of the Internet Protocol, has accelerated the birth of a large number of wireless data networks. Buzzwords, such as WiFi, Bluetooth and WiMax, have already become everyday language even for people unfamiliar with their technological meaning. They all, however, refer to the same basic functionality: the transfer of high-speed data through wireless networks. As we proceed in the twenty-first century, the variety of wireless standards is far from converging, since each one has its own peculiar advantages. Trying to figure out their evolution is very difficult. The only certain fact is that all of them will seek to enable digital communications through broadband wireless equipment, and one of the main tasks being the capability of allowing a large number of different users to coexist and operate in a crowded and often unregulated electromagnetic environment. The design of modern digital wireless modems and transceivers, capable of supporting high-speed data protocols in such wild scenarios, is very different from the traditional one. Many of the components in the wireless chain require an integration scale whose cost can be justified only for extremely large production quantities, thus, their design and production is way beyond the capability of most hi-tech industries. As a consequence, as happened with digital processors and memories, R&D engineers must now learn how to manage using off-the-shelf multi-purpose components manufactured by a few giant chipmakers.

In contrast, several of the most critical subsystems, such as voltage controlled oscillators (VCO), linear power amplifiers, fast-hopping synthesizers and so on, are so diversified and application-dependent, that in many cases there exist no suitable components from standard lines of products.

### **1.1 The RF Interface**

Wireless transmitters and receivers can be conceptually separated into baseband and RF sections. Baseband produce their output over the range of frequencies that transmitters take their input from. The underlying rate at which data can flow through the system is determined by the bandwidth of the baseband section. The improvement of the fidelity of the data stream communicated requires a considerable amount of signal processing, as well as the reduction of the transmitter's load which is placed on the transmission medium for a particular data rate. The conversion of the processed baseband signal up to the assigned channel and the signal's injection into the medium is the prime responsibility of the RF section of the transmitter.

There are two primary design goals concerning the transmitters. Firstly, they ought to transmit a specified amount of power, while consuming as little power as possible. Secondly, they must avoid interference with transceivers operating on adjacent channels. When designing receivers on the other hand, there are three primary design goals. First, they must faithfully recover small signals. They also have to reject any possible interference outside the desired channel and finally, receivers must be frugal power consumers, like transmitters.

#### **1.1.1 Small Desired Signals**

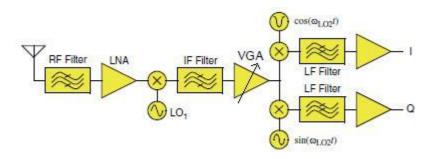

In order to detect small input signals, receivers have to be very sensitive. It is typical for receivers to operate with as little as 1  $\mu$ V at the input. It is the noise generated in the input circuitry of the receiver that limits its sensitivity. Therefore, noise and consequently the ability to detect noise by simulation are both important concerns. As shown in Figure 1, a typical superheterodyne receiver [1] first filters and then amplifies its input with a low noise amplifier or LNA. It then translates the signal to the intermediate frequency or IF by mixing it with the first local oscillator or LO. The noise performance of the front-end is determined mainly by the LNA, the mixer, and the LO.

Fig.1 A superheterodyne receiver's RF interface.

The small input signal level requires a tremendous amount of amplifications by the receivers. The need of 120 dB is a common case. As a result of such a high gain, any coupling from the output back to the input can cause problems. It is important to mention at this point that the superheterodyne receiver's architecture is used not only to spread that gain over several frequencies in order to reduce the chance of coupling, but also to result in the first LO being at a different frequency than the input. As a consequence, prevents the contamination of the small input signal by the large one. There are numerous reasons why the direct conversion or homodyne architecture is a candidate to replace the superheterodyne architecture in some wireless communication systems. In this architecture the RF input signal is directly converted to baseband in one step. Therefore most of the gain will be at baseband and the LO will be at the same frequency as the input signal. In this case, it is very important to determine the impact of small amounts of coupling. Thus careful modeling of the stray signal paths is required, such as coupling through the substrate, between package pins, bond wires and through the supply lines.

#### **1.1.2 Large Interfering Signals**

Receivers must be sensitive to small signals even in the presence of large interfering signals, often known as blockers. They are needed, when a strong transmitter broadcasting in an adjacent channel tries to receive a weak or distant signal. The interfering signal can be 60-70 dB larger than the desired signal. It can also act to block its reception by overloading the input stages of the receiver or by increasing the amount of noise generated in the input stage. Both problems result if the input stage is driven into a nonlinear region by the interferer. In order to avoid these problems, strict linearity is required from the front-end's part, which makes linearity a crucial factor in receivers. Receivers are narrowband circuits and so the nonlinearity is quantified by measuring the intermodulation distortion. This involves driving the input with two sinusoids that are in band and close to each other in frequency and then measuring the intermodulation products.

#### 1.1.3 Adjacent Channel Interference

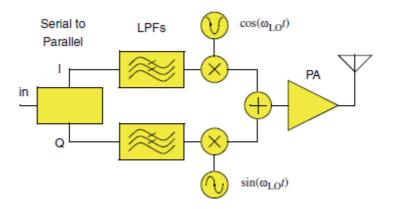

Another important factor in the transmitter is the distortion, since nonlinearity in the input stages can cause the transmitted signal's bandwidth to spread out into adjacent channels. The bandwidth of the signal is limited before the transmitter's power amplifier (PA, as shown in Figure 2) and the intermodulation distortion in the PA causes the bandwidth to increase again. This process is referred to as Spectral Regrowth. A large increase will prevent the transmitter from meeting the adjacent power requirements.

Fig.2 A digital direct conversion transmitter's RF interface.

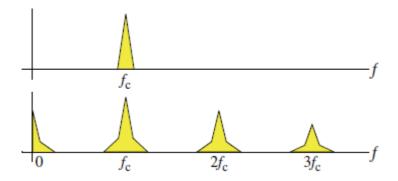

The spectrum of a narrrowband signal is described in Figure 3. The signal is replicated at multiples of the carrier due to nonlinearity, an effect known as harmonic distortion. It also adds a skirt to the signal that increases its bandwidth, am effect referred to as intermodulation distortion. Eliminating the effect of harmonic distortion is possible with a bandpass filter; however the frequency of the frequency of the intermodulation distortion products overlaps the frequency of the desired signal. For that reason it cannot be completely removed with filtering.

Fig.3 Spectrum of a narrowband signal passing through a nonlinear circuit.

### **1.2 Design Bottleneck**

Nowadays mobile devices and transceivers contain more than one million transistors, however a small proportion of that operates in RF range and the rest take place in low-frequency baseband and digital signal processing, Figure 4.

Fig.4 RF and baseband processing in a transceiver.

Nevertheless, despite the fact that transistors working in baseband frequencies are greater in number, RF transistors defines the design bottleneck for the following 3 reasons [2]:

#### • Multidisciplinary Field

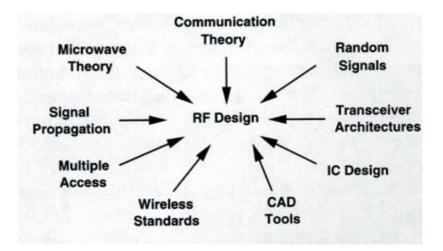

In contrast to other types of analog and mixed-signal circuits, RF systems demand a good understanding of many areas that are not directly related to integrated circuits (ICs). These areas shown in Figure 5 have been studied extensively over the last century, changing rapidly as time passes. That makes it quite difficult for an engineer to collect all the available information he needs in a small amount of time. As a result communication theory, RF system theory and analog design should be blended together in order to reach the desired outcome. This gives the RF engineer fewer options to work with since the standards of the other fields should be met. Moreover as the industry moves toward higher integration and lower cost, RF and wireless design demands increasingly more concurrent engineering, forcing IC designers to have sufficient knowledge of all sectors depicted in Figure 5.

Fig.5 Disciplines required in RF design.

#### • RF Design Hexagon

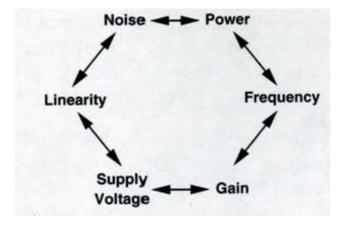

RF circuits must process analog signals with a wide dynamic range at high frequencies. It is interesting to note that the signals must be treated as analog even if the modulation is digital or the amplitude carries no information. The trade-offs involved in the design of such circuits are shown in the "RF design hexagon" shown in Figure 6.

Fig.6 RF design hexagon.

What the most important is that compared to analog design of IC circuits, RF circuits do not benefit that much from technological advancements due to the fact that they require external components such as inductors which are difficult to place on the chip even in most recent IC processes.

#### • Design Tools

Computer-aided analysis and synthesis tools for RF ICs are still in their infancy, forcing the designer to rely on experience, intuition, or inefficient simulation techniques to predict the performance. One issue is that circuits designed at a computer program are simulated in the time domain to include time-variant parameters and in order to obtain the spectrum of the frequency domain the resulting waveforms are transformed. However this procedure requires a significant amount of time, not to mention the fact that there are inaccuracies at the results since sometimes random noise is not taken into consideration. However it should be mentioned that as time passes these tools have shown dramatic evolution adding more features and accuracy at the hands of the designer. One of these tools is Cadence Virtuoso, the main design tool that this thesis was implemented.

### **1.3 Receiver's Concepts**

#### 1.3.1 Basics

The main purpose of the receiver is to accept the signals through the antenna from the transmitter and perform various tasks such as amplification, mixing, demodulation and then pass it on for digital signal processing. Selectivity and sensitivity are two parameters affect the performance of the receiver to a large extent. Apart from them, linearity gain and noise performance are crucial factors when designing a receiver.

#### 1.3.2 Sensitivity

Receiver's sensitivity is specified by the minimum amount of signal that can be sensed, with noise occurrence, at a standard distance. In simple words, the distance between receiver and transmitter is determined. Sensitivity is specified in terms of dBm (decibels relative to 1 mW). Total sensitivity is affected not only from the noise figure but also from the gain of all the individual blocks. The noise Figure is defined as the ratio between the SNR at the input and the SNR at the output of the circuit.

$$F \equiv \frac{InputSNR}{OutputSNR}$$

(1.1)

$$NF \equiv \log(F)$$

(dB) (1.2)

where F is the noise factor and NF is the noise figure of the system.

Noise Figure is usually estimated in relation to a specific source impedance and noise temperature. In wireless communication systems, the standard values for transmission lines resistance is  $Rs = 50\Omega$  and at temperature, T=293 K. The overall noise figure at an individual block like the VGA can be expressed combining the gain and the output noise added by the system. G is the power gain of the amplifier with input signal power  $P_{input}$  and input noise power  $N_{input}$ .  $N_{added}$  is the noise added externally to the system,  $GP_{input}$  the output signal power and by adding them results in output noise power. The noise figure is given by:

$$F = \frac{\left(\frac{P_{input}}{N_{input}}\right)}{\left(\frac{GP_{input}}{GN_{input} + N_{added}}\right)}$$

(1.3)

$$F = 1 + (N_{added} / GN_{input}) = 1 + (N_{added,input} / N_{input})$$

(1.4)

where N<sub>added,input</sub> is the input referred added noise from the amplifier.

#### 1.3.3 Noise Figure

:

The noise figure of the overall receiver can be calculated by the noise figure of the individual cascaded blocks in the receiver chain. The noise figure of the entire cascaded chain depends on the noise figure of the individual blocks as well as the gain distribution. For a receiver chain consisting of 2 blocks cascaded with proper matching, the total output noise is given by

$$P_{noise,output} = F_1 P_{noise,input} G_1 G_2 + (F_2 - 1) P_{noise,input} G_2$$

(1.5)

where G<sub>1</sub> and G<sub>2</sub> are the power gains of the individual blocks with corresponding noise figures F<sub>1</sub> and F<sub>2</sub>.

The output SNR of the cascaded blocks is given by

$$SNR_{output} = \frac{S_{out}}{P_{noise,output}} = \frac{S_{input}G_1G_2}{F_1P_{noise,input}G_1G_2 + (F_2 - 1)P_{noise,input}G_2}$$

(1.6)

Total cascaded noise figure can be calculated as

$$F = \frac{SNR_{output}}{SNR_{input}} = F_1 + \frac{(F_2 - 1)}{G_1}$$

(1.7)

From the above equation it can be seen that the total noise figure of the cascaded blocks depends on the noise figures of the individual blocks as well as the gain of the first block. If the gain G1 is large then the noise from the succeeding blocks will have less effect on the overall noise figure. Hence the first block of the receiver, usually LNA, and VGA in this thesis, must have low noise figure and enough gain.

#### 1.3.4 Selectivity

Selectivity is the measure of performance of the receiver to separate the wanted or required signals from those which are not required. Selectivity is significant when the receiver has to choose between a weak desired signal and a strong neighbouring interfering/undesired signal. There is no quantitative way to measure the selectivity of a receiver but usually specified as blocking masks used in filtering, nonlinearity and phase requirements in the circuit.

#### 1.3.5 Main blocks

The receiver is divided into 3 main functional blocks:

- Front end: all the circuits whose functionality is affected by the RF frequency, such as RF front filters, low-noise amplifiers (LNA), high frequency mixers etc.

- Intermediate frequency (IF) chain: all the circuits operating at non-zero IF frequency ,which are not always met like the circuits at the front end.

- Backend: all the circuits operating at a frequency below IF and RF frequencies, such as baseband processing, detector etc.

### CHAPTER 2

### FUNDAMENTALS OF VGA DESIGN

#### 2.1 Frequency Response and Stability of Amplifiers

#### 2.1.1 Miller Effect

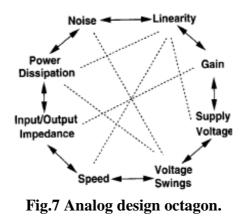

Nowadays in most analog circuits with high performance requirements, trade-offs between the speed and other important parameters, such as gain, power dissipation and noise, exist. In practice most of these parameters trade with each other, making the design a multi-dimensional optimization problem. The analog design octagon, illustrated in Figure 7, suggests that the design of high-performance amplifiers requires deep intuition and experience in order to achieve the specifications given [3].

Studying the frequency response of single-stage and differential amplifiers will make it easier to understand the frequency limitations of each circuit and the trade-offs set by them.

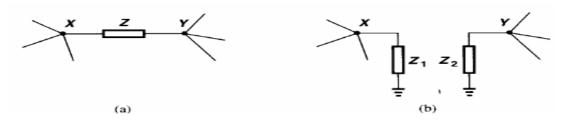

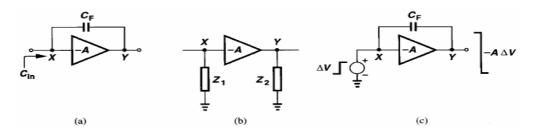

An important phenomenon that is related to frequency response, during the compensation techniques, is the **Miller Effect**. According to it, if the circuit depicted in Figure 8(a) can be converted to that of Figure 8(b) then  $Z_1 = Z/(1 - A_v)$  and  $Z_2 = Z/(1 - A_v^{-1})$ , where  $A_v = V_Y/V_X$ .

Fig.8 Miller effect on floating impedance.

This is very useful when it is needed to calculate the input and output impedance of a circuit. For example, let us consider the circuit shown in Figure 9(a), where the voltage amplifier has a negative gain equal to -A and is otherwise ideal. If it is needed to calculate the input capacitance we use the Miller Effect.

Fig.9 Voltage amplifier with negative feedback example.

First of all, according to the theorem, the initial circuit can be converted to the one depicted in Figure 9(b). If we apply a voltage step  $\Delta V$  at the input ,then the voltage at the output will be  $-A\Delta V$ , yielding a total change of  $(1+A)\Delta V$  in the voltage across C<sub>F</sub>. Thus, the charge drawn by C<sub>F</sub> from V<sub>in</sub> is equal to  $(1+A)\Delta VC_F$  and the equivalent input capacitance equal to  $(1 + A)C_F$ . As a result, the input capacitance is equal to  $C_F(1 + A)$ , meaning that  $Z = 1/(C_F s)$  and  $Z_1 = [1/(C_F s)]/(1 + A)$  Figure 9(c).

That was a simple example on how to calculate the input and output impedance of a circuit. However, Miller effect does not necessarily ensures us that we can calculate the input/output impedance of any complex circuit. It is important to know that the initial circuit can be converted to the one that Miller's theorem can be applied. If the impedance Z forms the only signal path between X and Y, then the conversion is often invalid (unique signal path). Nevertheless, Miller's theorem proves useful in cases where the impedance Z appears in parallel with the main signal Figure 10.

Fig. 10 Typical case for valid application of Miller's theorem

#### 2.1.2 Association of poles with nodes

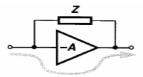

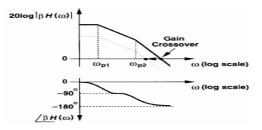

In order to understand the frequency response of a circuit we have to study the association of the poles created by the circuit, (and later the zeros) with the circuit's nodes. Considering the circuit depicted in Figure 11 it can be noticed that the circuit is consisted of two (ideal) voltage amplifiers in cascade form.

Fig. 11 Cascade of amplifiers.

$C_{in}$  and  $C_N$  are the input capacitances of the first and the second amplifier respectively, whereas  $C_P$  stands for the load capacitance of the circuit. The overall transfer function can be written as

$$\frac{V_{out}}{V_{in}}(s) = \frac{A_1}{1 + R_S C_{in} s} \cdot \frac{A_2}{1 + R_1 C_N s} \cdot \frac{1}{1 + R_2 C_p s}$$

(2.1)

According to the transfer function the circuit has three poles and more specifically  $\omega_1=1/R_sC_{in}$ ,  $\omega_2=1/R_1C_N$  and  $\omega_3=1/R_2C_p$ , each of them determined by the total capacitance from each node to ground multiplied by the total resistance seen at the node to ground. In this simple occasion it can be said that each node generates one pole. However this is not correct because in most circuits, resistances or capacitances placed in a node parallel to the initial nodes, interact with the poles changing the transfer function and the frequency response. One example of this is the circuit depicted in Figure 12.

Fig.12 Example of interaction between nodes.

#### 2.1.3 Multipole Systems

Observating the previous example, it can be easily concluded that a system with more than one pole is something common when it comes to analog design. In two-stage op amps, for example, each gain stage introduces a "dominant" pole. As it will be explained later, dominant pole is called that way because it crucially affects the system's total gain and phase margin in contrast with the other poles.

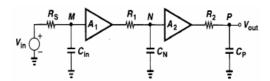

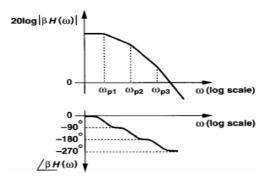

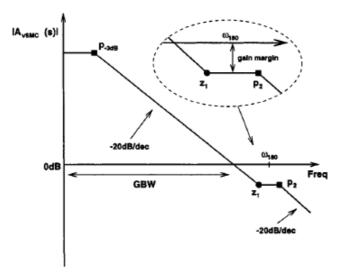

First of all it must be made clear how terms such as gain, bandwidth and phase margin are depicted on the Bode plots of a system and how can information be drawn from them. By studying the Bode plots of a feedback system at Figure 13, which depicts both gain  $|\beta H|$  and phase  $\langle \beta H \rangle$ , firstly it should be noticed that the value of the gain of the system is the initial **20log** $|\beta H(\omega)|$  value, where  $\beta$  is the feedback coefficient. That value is stable for  $\omega < \omega_{p1}$ , where  $\omega_{p1}$  is the dominant pole, and is the frequency point where gain starts to decrease. For  $\omega_{p1} < \omega < \omega_{p2}$  gain drops linearly and when  $\omega = \omega_{p2}$  then the gain will have been decreased by 20 dB/dec. At that point the bandwidth of the system can be found since it is the frequency of the  $\omega_{p2}$  pole. By observing the phase Bode plot we can calculate the phase margin, which is the stability indicator of the system. In order to find the phase margin, we first find the pole-frequency at which the gain reaches and drops below zero, **20log** $|\beta H(\omega)|=0$ . Then using that specific frequency on phase plot we find the respective angle in degrees ( $\langle \beta H \rangle$ ). By subtracting this angle from 180° the result is the phase margin (PM),  $PM = 180^\circ + \angle \beta H(\omega = \omega_1)$ , where  $\omega_{11}$  is the gain crossover frequency. The bigger the value of the result the more stable the system is and this will be explained later.

Fig.13 Bode plots of loop gain for a two-pole system.

First of all, to see theory in practice we consider that the above figure depicts the Bode plots of a loop-gain for a two-pole system. As described before, the magnitude begins to drop at 20 dB/dec at  $\omega = \omega_{p1}$  and at 40dB/dec at  $\omega = \omega_{p2}$ .On the same time phase changes at  $\omega = 0.1\omega_{p1}$ , reaching  $-45^{\circ}$  and  $-90^{\circ}$  at  $\omega = \omega_{p1}$  and  $\omega = 10\omega_{p1}$  respectively. Phase begins to drop again, because of the non-dominant pole  $\omega_{p2}$  and assuming that  $0.1 \omega_{p2} > 10 \omega_{p1}$ , by observing the figure it can be concluded that when  $\omega = \omega_{p2}$  then  $\angle \beta H = -135^{\circ}$ .As a result the phase margin is  $|180^{\circ}-135^{\circ}|=45^{\circ}$  declaring that the system is quite stable since the value is far from zero. However it is important to notice the system's behavior when changing the amount of the feedback, i.e. the value of  $\beta$ .Decreasing the  $\beta$  we reduce the feedback and this results in the faded gray plot of the Figure 13. First of all it is essential the fact that the phase plot does not change, in contrast with the gain plot where the curve is shifted to the left. This in turn moves the gain crossover point to the left too, resulting in more stable system since  $\angle \beta H$  is stable. All in all, the less feedback we demand the more stable the system is.

Moreover it is important to study, if additional poles or zeros affect the magnitude and the phase at the same rate. Going back to the previous example we noticed that, the phase begins to change at approximately one-tenth of the pole frequency whereas the magnitude begins to drop only near the pole frequency. For that reason the phase is much more affected by the addition of a pole or zero, than the magnitude. Studying the following plot Figure 14 will prove that.

Fig.14 Bode plots of loop gain for a three-pole system.

As it can be seen the third pole  $\omega_{p3}$  shifts the phase crossover point to the left (lower frequencies) and as a result  $|\beta H|$  drops to below unity at a frequency for which  $\angle \beta H$ >-180°. This leads to a non-stable system and oscillations.

After studying the frequency response of amplifiers and multipole systems basic topologies of a simple variable gain amplifier will be studied, examining their gain and bandwidth respectively.

#### 2.2 Gain and Bandwidth Specifications

The design of an amplifier requires an analysis of the trade-offs involved in fulfilling the specifications. For example, the higher the gain of the amplifier, the lower its bandwidth and the higher its non-linearity. It is apparent from the latter example that it is not trivial to achieve all specifications. Thus, the selection of a topology is based on fulfilling the most of the requirements, ensuring that the system operates in the desired output.

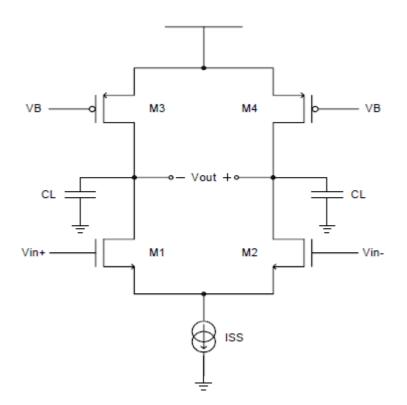

A simple differential amplifier is given in Figure 15. The gain of this amplifier is given by

$$A_{v} = g_{m}(r_{o2} \parallel r_{o4})$$

(2.2)

where  $g_m$  is the transconductance of the input transistors M1 and M2. The -3dB bandwidth of the amplifier is given by

$$\omega_{-3dB} = \frac{1}{C_L(r_{o2} || r_{o4})}$$

(2.3)

Equations 2.1 and 2.2 propose that that the gain of the amplifier is proportional and the -3 dB bandwidth is inversely proportional to its output resistance, leading to a trade-off between the maximum gain that can be achieved and the speed of the amplifier. Two stage amplifiers could be implemented to obtain higher gain, at the cost of additional poles and increased power consumption.

Fig.15 Differential amplifier with active load

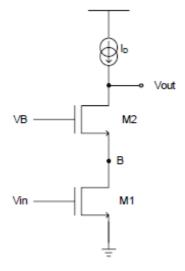

#### 2.2.1 Cascoding

By compromising the output voltage swing, the same gain as a two stage amplifier could be obtained by using a cascode structure with lower power dissipation [4]. The gain of the cascode stage shown in Figure 16 is given by

$$A_{v} = g_{m1}r_{o1}[(g_{m2} + g_{b2})r_{o2} + 1]$$

(2.4)

$$A_{v} \approx g_{m1} g_{m2} r_{o1} r_{o2}$$

(2.5)

Fig.16 Cascode amplifier

A major advantage of the cascode structure over a common-source stage is the significant reduction in the Miller effect observed by the gate-drain capacitor  $C_{GD1}$  due to the low impedance seen by the capacitor, looking into node B, for small values of  $R_D$ [3]. The pole associated with the capacitors at node B is given approximately by

$$\omega_{-3dB} = \frac{g_{m2} + g_{mb2}}{2C_{GD1} + C_{GB1} + C_{SB2} + C_{GS2}}$$

(2.6)

This normally results in a better frequency response of the cascode structure as compared to a simple common-source amplifier. On the other hand, the cascode structure has limited output voltage swing. This prevents using broadly the cascade structure from low voltage applications. The aforementioned drawback can be avoided achieving higher output voltage swing by employing the folded cascode structure as depicted in Fig. 17. An additional major advantage of the folded cascode structure is that it supplies the transistors with more headroom, preventing the cascode transistor from stacking on the top of the input device. However, the folded amplifier provides lower gain at lower bandwidth (due to lowering of the pole at the folding point) while consuming higher power.Poles and zeros theory with frequency compensation will be better examined at the end of this chapter.

Fig.17 Folded cascode amplifier

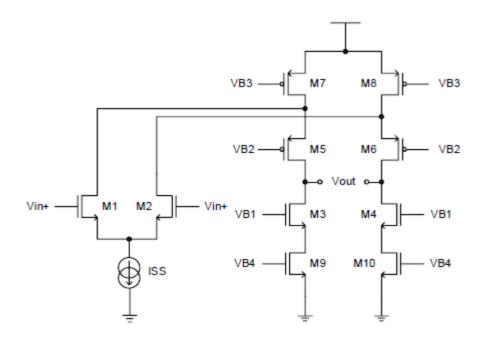

#### 2.2.2 Gain boosting in differential amplifiers with diode connected loads

In differential pair amplifiers with diode-connected loads, the loads consume voltage headroom, limiting the output voltage swing, gain and the input common mode range. One solution to boost the output voltage gain is to decrease the transconductance of the load transistor by reducing the W/L value of the load. However, this solution includes the drawback of increasing the overdrive voltage, and thus decreasing both the output common mode level and the voltage swing.

An alternative solution that bypasses the aforementioned disadvantage is to add PMOS current sources [4] in parallel to the load transistors, as shown in Fig. 18. The key feature of this scheme is that splits the current between the load and the current source. It leads to the advantage of reducing the W/L value of the load transistor without changing the overdrive voltage. Thus, the transconductance of the load can be decreased without compromising the output voltage swing.

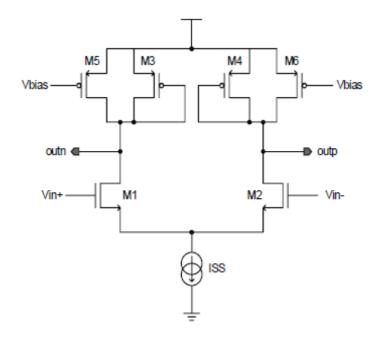

Fig.18 Addition of current sources to increase the gain of differential amplifier with diode-connected load.

In order to illustrate the function of the aforementioned scheme, we provide the following example: If transistors M5 and M6 of Figure 18 carry 40% of the drain current of M1 and M2, and the load transistors M3 and M4 carry the remaining 60%, their transconductance 10 decreases by a factor of 2/5 since the W/L ratios of M3 and M4 can also be decreased by the same amount without affecting their overdrive voltage. Thus, the differential gain increases by approximately 5/2 times that of the gain when the PMOS current sources are not included in the circuit. A disadvantage of this method of increasing the gain is that the current sources add parasitic capacitances to the output node of the circuit, slightly lowering the -3dB bandwidth.

### 2.3 Frequency Compensation

Nowadays, multistage amplifiers are an essential part when designing in modern technologies, as the single-stage amplifiers cannot live up to the expectations of low-voltage design. Furthermore, short-channel effect of the sub-micron CMOS transistor degrades output impedance and as a result the gain of the amplifier is reduced at a large scale. That makes frequency compensation at multistage amplifiers an essential sector and many frequency-compensation topologies have been reported based on pole-splitting and pole-zero cancelation techniques. These techniques will be explained later on having as an example a 2-stage amplifier. However, in order to reach the optimum results not only provided stability criteria but also trial and error procedure is required. At the same time, it should be noticed that the provided stability criteria find difficulties from theory to practice since any extra stage consumes more power, requires more complicated circuit structure and may reduce the bandwidth dramatically. In order to understand the more complex frequency compensation topologies, it is highly recommended to start examining the frequency response of a single-stage amplifier.

#### 2.3.1 Single-stage amplifier review

Single-stage amplifier's frequency behavior is quite stable since the amplifier has only one left-half-plane (LHP) pole, as it can be noticed from its transfer function.

$$A_{v \sin g l e}(s) = \frac{g_{mL} R_L}{1 + s C_L R_L}$$

(2.7)

where  $g_{mL}$  is the output stage transconductance,  $R_L$  is the loading resistance and  $C_L$  the loading capacitance, which is in fact the compensation capacitor of the amplifier. The GBW of the amplifier is obtained by the equation (2.8).

$$GBW = \frac{g_{mL}}{C_L}$$

(2.8)

and the phase margin PM of the amplifier is 90°, because of the single pole. From () it can be deducted that GBW can be increased, by increasing the  $g_{mL}$  factor or decreasing the loading capacitance. However, the existence of many parasitic poles and zeros ( $p_{par}$  and  $z_{par}$ ) should not be neglected as they affect the stability of the amplifier. The transistor's dimensions and the bias current determine the position of the parasitic poles and zeros, frequency of which, as a rule of thumb, should be at least the double of the GBW. In other words, there is a maximum  $g_{mL}$  and a minimum  $C_L$  for the single-stage amplifier at which min( $p_{par}$  and  $z_{par}$ )>2GBW. Nevertheless, the dc gain of the single-stage amplifier is relatively small and to deal with this drawback gain-boosting topologies are employed on the initial circuit. However, these topologies require a larger supply voltage, a more complicated circuit design and at the same time limit the maximum output voltage swing. It should be noticed though, that the bandwidth of the amplifier is not affected due to its independence of  $R_L$ .

#### 2.3.2 Two-stage amplifier with Simple Miller Compensation (SMC)

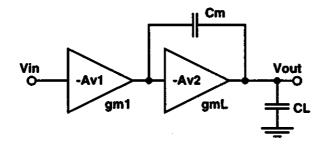

As mentioned above single-stage amplifier has excellent frequency response, however cascode configuration maybe be needed in order to increase the gain. Nevertheless, cascode configuration cannot live up to the expectations of the modern demanding low-voltage design. To face this problem two-stage SMC amplifier [5] is commonly used Figure (19).

Fig.19 SMC amplifier

The transfer function of the above structure is given by:

$$A_{V(SMC)}(s) = \frac{g_{m1}g_{mL}R_{o1}R_{L}(1-s\frac{C_{m}}{g_{mL}})}{(1+sC_{m}g_{mL}R_{o1}R_{L})(1+s\frac{C_{m}}{g_{mL}})}$$

(2.9)

It can be noticed that there are two LHP poles and one right-half-plane (RHP) zero. The dominant pole is  $p_{-3dB}=1/C_m g_{mL} R_{o1}R_L$ , the non-dominant pole is  $p_{2}=g_{mL}/C_L$  while the RHP zero is  $z_1=-g_{mL}/C_m$ , where  $C_m$  is the compensation capacitor. It is a rule that both  $p_2$  and  $z_1$  should be at frequencies higher than the unity-gain frequency in order to ensure circuit's stability. How can this condition be achieved? An easy solution is to use a relatively large capacitor  $C_m$  in order to move the dominant pole to a lower frequency. However by doing this, the GBW is linearly reduced since GBW= $g_{m1}/C_m$ .As a result it is suggested that GBW is set to be at the half of the frequency of  $p_2$  in order to obtain a good phase margin and bandwidth at the same time.

$$C_{L} = \frac{1}{2} \frac{g_{mL}}{g_{m1}} C_{m}$$

(2.10)

If  $g_{m1} / g_{mL}$  has a large value then  $C_m$  is quite large compared to  $C_L$  according to (2.10). In this case,  $z_1$  is at a frequency before or close to the one of  $p_{2,as}$  shown in Figure 20. On the other case where  $p_2$  is before  $z_1$  we receive a small gain and the amplifier shows a quite unstable behavior if there are parasitic poles and zeros. However if  $z_1$  is after  $p_2$  we may have low gain but the phase margin achieves quite good values. In other words the position of the RHP zero sets the tradeoff between gain and the phase margin.

Fig.20 Frequency response of a SMC amplifier

Using (2.9) and (2.10) GBW is given by

$$GBW = \frac{g_{m1}}{C_m} = \frac{1}{2} \left(\frac{g_{mL}}{C_L}\right)$$

(2.11)

which compared to the single-stage amplifier has the half value. The GBW of a twostage SMC amplifier cannot be increased by increasing  $g_{m1}$ . This happens because the required  $C_m$  is increased proportionally with  $g_{m1}$  so the  $g_{m1}/C_m$  has a constant value. One way of improving GBW is increasing the output transcoductance  $g_{mL}$  and decreasing the loading capacitance  $C_L$  at the same time. Then the PM is evaluated by the following expression:

$$PM = 180^{\circ} - \tan^{-1}(\frac{GBW}{p_{-3dB}}) - \tan^{-1}(\frac{GBW}{p_{2}}) - \tan^{-1}(\frac{GBW}{|z_{1}|})$$

$$\approx 63^{\circ} - \tan^{-1}(\frac{g_{m1}}{g_{mL}})$$

(2.12)

By noticing the equation (2.12) it can be concluded that the PM is highly affected by the  $g_{m1}/g_{mL}$  ratio, which in fact reveals the RHP zero effect on the PM. The RHP zero is created by the feedforward small-signal current that flows through the compensation capacitor  $C_m$  to the output. The first way to increase the  $g_{m1}/g_{mL}$  ratio is to search for a large  $g_{mL}$ . If the  $g_{mL}$  is large, then the small-signal output current is larger than the feedforward current and the effect of the RHP zero appears at very high frequencies. At this work we care about very high frequencies so the problem

still exists. As a consequence choosing a smaller  $g_{m1}$  is preferable. However there are some limitations when choosing the  $g_{m1}$  such as the bias current, which is related to the slew rate, and the size of the input differential pair. Moreover, if the size of the differential pair is relatively small, then there is the danger of having increased offset voltage at the output. All in all, a small  $g_{m1}$  cannot be obtained easily. In conclusion, according to the previous analysis, the RHP zero creates serious concerns regarding the stability of the amplifier. To deal with this problem, several methods can be employed such as the addition of a voltage buffer or a nulling resistor to the circuit. The presence of the nulling resistor at the circuit is a technique that will be studied later at this work.

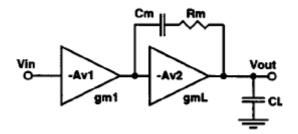

# **2.3.3** Two-stage amplifier with Simple Miller Compensation with Nulling Resistor (SMCNR)

As mentioned above the feedforward small-signal current creates the RHP zero. One way to eliminate this zero is to increase the impedance seen at the capacitance path, and this can be done by inserting a resistor to the circuit. The resistor, called nulling resistor, is inserted next to the compensation capacitor as shown in Figure 21.

Fig.21 SMCNR amplifier

It is significant to notice that the addition of the resistor affects not only the frequency position of the RHP zero but also the position of the poles. Theoretically speaking, when the value of the nulling resistor reaches infinity, the compensation network is open-circuit and as a result no **pole-splitting** takes place. Pole-splitting will be explained afterwards in this chapter. In other words there are limits regarding both the minimum and the maximum value of the nulling resistor.

The transfer function of the SMNCR (R<sub>m</sub>) amplifier is given by:

$$A_{\nu(SMCNR)}(s) = \frac{g_{m1}g_{mL}R_{o1}R_{L}[1+sC_{m}(R_{m}-\frac{1}{g_{mL}})]}{[1+sC_{m}(R_{m}+g_{mL}R_{o1}R_{L})][1+s\frac{C_{L}(R_{o1}+R_{m})R_{L}}{R_{m}+g_{mL}R_{o1}R_{L}}]}$$

(2.13)

The dominant pole is  $p_{-3dB}=1/C_m$  (Rm  $+g_{mL}R_{o1}R_L$ ), the non-dominant pole is  $p_2=(R_m+g_{mL}R_{o1}R_L)/C_L$  ( $R_{o1}+R_m$ )  $R_L$  and the zero is  $z_1=1/C_m$  (Rm -  $1/g_{mL}$ ).Later on, it will be proved that when  $R_m=1/g_{mL}$  the RHP zero is completely eliminated. In that case, the circuit is in practice a SMC amplifier and the  $C_m$  and GBW are given by the equations (2.10) and (2.11) respectively. Moreover, as proven before, the value of the phase margin is about 63° because of the absence of the zero. However, when using a nulling resistor in design it is preferable to choose a value larger than  $1/g_{mL}$  in order to transfer the zero to the left plane and in that way, increases the phase margin. Indeed, observing the transfer function (2.13), when the value of  $R_m$  is increased the position of the poles change as they move to lower frequencies. However we should be careful not to overpass the suggested value of  $R_m$  because there will be no pole-splitting effect. In other words, it is suggested that the value of  $R_m$  lies between  $1/g_{mL}$  and (1/10) Ro1. The upper limit is set by the assumption that the value of  $R_m$  is negligible when determining the frequencies of  $p_{-3dB}$  and  $p_2$  at the transfer function.

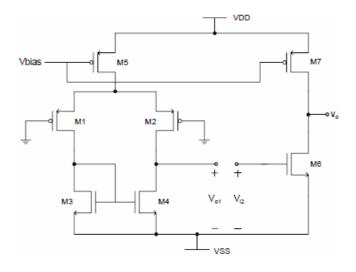

#### 2.3.4 Pole-splitting and zero-cancellation

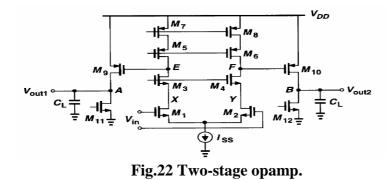

As mentioned before two important methods in order to utilize the frequency compensation are the pole-splitting and zero-cancellation methods. Studying an example will make it easier to understand not only the significance of the methods but also the way they work. Considering the circuit depicted in Figure 22, three poles  $p_x$ ,  $p_E$ ,  $p_A$  are identified at nodes X, E and A respectively.

Nodes X and Y are the nodes at the sources of the differential pair transistors, so it is known [3] that their frequencies are relatively high. However, examining the rest two poles it will point out that both their frequencies lay near the origin pole. First of all, regarding the  $p_E$  this happens because the small-signal resistance seen at E is quite high, which means that M<sub>3</sub>, M5 and M<sub>9</sub> are capable of creating a pole close to the origin one. On the other hand, the loading capacitance C<sub>L</sub> is quite high at node A and this brings the same result. As a result there are two dominant poles.

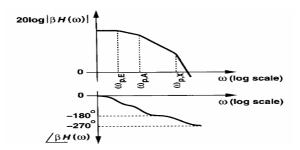

Assuming that  $p_E$  is more dominant than  $p_A$  the magnitude and phase plots are constructed as shown below in Figure 23.

Fig.23 Bode plots of loop gain of two-stage op amp.

It can easily be observed that due to the existence of two dominant poles near the origin, the phase starts to drop quite rapidly after the second pole and before reaching the third. The question is what kind of frequency compensation should be applied to this case.

In Figure 23, one of the dominant poles must be moved toward the origin so as to place the gain crossover well below the phase crossover. However, it is a rule that, the unity-gain bandwidth cannot exceed the frequency of the second dominant pole[3]. In case we decide to reduce the magnitude of  $p_E$ , automatically we limit the bandwidth near the frequency of  $p_A$ , which is a small value, not to mention the fact that in order to achieve that we need a large capacitor, which means consuming odd space at the circuit's design.

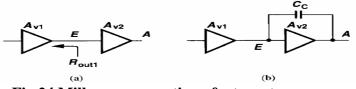

An effective way to save a considerable amount of chip area is to use the Miller compensation technique. Shown in Figure 24 the initial circuit is a two-stage amplifier, which assumable the first stage exhibits high output impedance and the second adds a moderate gain, conditions which make the employment of the Miller theorem feasible.

Fig.24 Miller compensation of a two-stage op amp

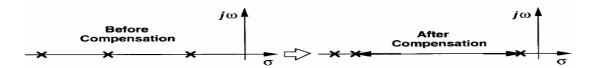

The goal is to create a large capacitance at node E, but using on the same time a capacitor of moderate size in order to save chip area. The capacitance that is created because of the Miller effect is  $C_c(1+A_{v2})$  and the total capacitance at node E, which denotes the frequency of the respective pole, is  $R_{out1}^{-1}[C_E + (1 + A_{v2})C_C]^{-1}$  where  $R_{out1}$  is the output resistance of the first stage and  $C_e$  the capacitance at node E before the addition of  $C_c$ . Besides improving the minimum chip area needed the Miller compensation moves the output pole away from the origin. This phenomenon shown in Figure 25 is called **pole-splitting.**

Fig.25 Pole splitting as a result of Miller compensation.

In simple words, the addition of the Miller capacitor moves the interstage pole towards the origin and the output pole in the different direction. This results in a far greater bandwidth compared to the occasion that a capacitance is interposed between a node and the ground.

However, during the previous analyses a serious fact was omitted: the presence of zeros in the transfer function. Whenever Miller compensation is applied, a RHP zero is created, as by doing that a parasitic path is formed from the input to the output. For instance, assuming that the frequency of the zero is  $\omega_z$ , this is expressed at the numerator of the transfer function as  $(1-s/\omega_z)$ , producing a phase of  $-\tan^{-1}(\omega/\omega_z)$ . This is a negative value since  $\omega_z$  is positive. In that way, like LHP poles, zeros increase the phase shift and move the phase crossover toward the origin. At the same time, a presence of a RHP zero slows down the magnitude curve positioning the gain crossover away from the origin. Combining the last two effects, it is easy to notice that the zero reduces the system's stability.

Figure 26 shows a simplified circuit of a two-stage opamp, and the RHP zero frequency  $\omega_z$  is given by  $g_m/(C_C + C_{GD})$  [3], where  $C_C$  is the Miller capacitance. Usually  $g_m$  has a small value so  $\omega_z$  is affected at a large percent by the  $C_C$ , which occasionally has a relatively high value, in order to set the dominant pole properly.

Fig.26 Simplified circuit of two-stage opamp, with the addition of R<sub>z</sub>

In order to eliminate the zero  $R_z$  resistor is added in series with the compensation capacitor. This happens because the altered  $\omega_z$  is calculated as

$$\omega_Z \approx \frac{1}{C_C(g_{m9}^{-1} - R_z)}$$

(2.14)

One simple way to eliminate the zero would be to set  $\omega_z=1/g_{m9}$ . However, it is a design trend to set a  $R_z$  so that  $\omega_z < 0$ . A good reason to move the zero to the left half plane as a way to neutralize the first non-dominant pole, whose frequency is

$$\omega_{p2} = \frac{-g_{m9}}{C_L + C_E}$$

(2.15)

Combining (2.14) and (2.15) and taking into consideration that  $C_E$  has typically a much smaller value than  $C_C$ ,  $C_L$ :

$$R_Z \approx \frac{C_L + C_C}{g_{m9}C_C} \tag{2.16}$$

Although canceling the first non-dominant pole is a quite attractive prospect, this method has two disadvantages. First of all, it is not easy to find the exact suitable value for  $R_{z_i}$  according to 2.16 as  $C_L$  in most cases has a variable value since the output of the opamp for example may be an input to a higher level circuit. As a result the load capacitance changes. Moreover since  $R_z$  a significant value, in order to save space, is substituted by a transistor working in triode region. A random voltage swing may upset the frequency of the zero and in that way preventing it from canceling the non-dominant pole.

# 2.4 Gain Varying Techniques

Fundamentally, the gain of an amplifier depends on the equivalent transconductance Gm and the output impedance. In order to vary the gain, one of the two parameters needs to be varied. As a result, variable gain can be achieved by tuning bias current, emitter/source degeneration and/or loading. This section briefly introduces and compares these design techniques together with some other techniques that can be employed for variable gain amplifiers.

#### • Variable Bias Current

The most direct way to tune the transconductance, which is highly related to the gain of the circuit, is by tuning the bias current. Although this is a simple technique, tuning the bias current lacks in versatility since noise, power, bandwidth, and linearity, which also depend heavily on it.

#### Variable Source Degeneration

Either using an emitter or source degeneration, another technique which enables the gain tuning is tuning the degeneration resistors, Figure 27. This is feasible if, a MOS transistor operating in its triode region as a variable resistor is employed. Its resistance is given by:

$$R = \frac{1}{\mu C_{ox} \frac{W}{L} (V_{GS} - V_T)}$$

(2.17)

The differential pair performs better when given a low power supply because when is low power supplied, the degeneration does not impose penalty on voltage headroom due to bias  $V_{GS}$ - $V_T$ . Nevertheless, the noise performance is poor.

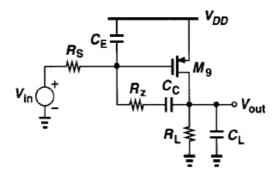

Fig.27 Variable gain amplifier with MOS as a variable degeneration resistor.

# • Variable Load

A technique that matches the variable bias current technique is the variable load tuning. By employing a MOS device operating in triode region, in parallel with  $R_D$  or substituting it, a variable load resistor is created. Although simple, this techniques main drawback is that it suffers from the severe trade-off of the amplifier's performance in terms of noise, linearity and bandwidth. The variable load technique is occupied in the main block of this thesis.

## • Current Steering

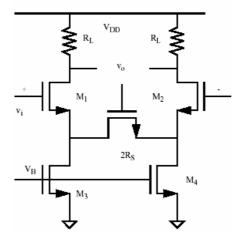

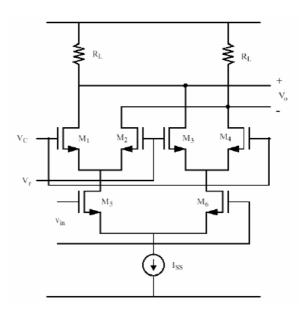

Another interesting technique, referred to as current steering, can be employed to realize a variable-gain amplifier. The simplified schematic is shown in Figure 28. Transistors M1-M4 are to steer the differential drain current of M5-M6 to the output according to the control voltage VC in relation to a reference voltage Vr.

Fig.28 Variable gain amplifier based on current steering technique.

The overall gain is given by:

$$A_V = (2a - 1)g_{m5}R_L \tag{2.18}$$

where  $\alpha$  is the fraction of the drain current from M5 flowing through M1 to the output[6]

$$0 < a = \frac{i_{d1}}{i_{d4}} = f(V_C, V_T) < 1$$

(2.19)

The key advantage of this current-steering technique is that the amplifier's parameters, including bias current, noise, bandwidth and linearity, are all independent of the control voltage and thus the gain setting. The disadvantages include more active devices and thus more noise and more voltage headroom, which may not be suitable for low-voltage and high-swing applications. It is interesting to note that the transistors M1-M4 do not need to cross couple from each other. In this case, the voltage gain becomes:

$$A_V = ag_{m5}R_L \tag{2.20}$$