### Diploma Thesis: Hardware Task Scheduling Targeting a Realistic FPGA device

by George Charitopoulos

Department of Electronic and Computer Engineering Technical University of Crete Chania, February 2013 Advisor Professor: Prof. Dionisios Pnevmatikatos

Evaluation Committee: Professor Dionisios Pnevmatikatos Professor Apostolos Dollas Associate Professor Ioannis Papaefstathiou

### Abstract

The last few years FPGAs have penetrated the mainstream and have experienced wide usage through the users. Also the concept of reconfigurable computing has benefited numerous application domains, with FPGAs being the stronger representative of that. One of the most crucial technologies incorporated in some specific FPGA families is called partial reconfiguration. It allows for the reprogramming of part(s) of the FPGA chip without disturbing the rest of its operation, even during runtime.

FPGAs have been widely adopted in embedded systems. Partial reconfiguration technology can leverage these systems by swapping in and out task modules in an operating-system fashion. A task can be downloaded upon arrival or when needed, during the system operation. To this direction one of the most important parts of said embedded system is the Scheduling Algorithm.

The Scheduling Algorithm is responsible for the placement and scheduling of hardware tasks on the device when those are needed. Thus far many scheduling algorithms have been proposed by the research community. However these algorithms have the drawback that they are not compatible with the target devices, due to the neglecting of several technology restrictions.

In this thesis we present a novel scheduling algorithm that manages the arrival of hardware tasks and places them on the FPGA. This algorithm could be incorporated at any complete runtime system inhabited on a FPGA.

### **Dedication**

I would like to dedicate my thesis in my passed away grandmother, Harikleia, with the hope that this work will finally convince her that I, in fact, was accepted and finished my education at the Technical University of Crete.

### Acknowledgments

I would like to thank, first and foremost, my family, who I deeply love, for their love and support, during all these years.

Also I would like to thank Dr. Kyprianos Papadimitriou, for without his help and guidance this work would never see the light of day, also for always being there to talk about the difficulties of this work and making said talks easy, pleasant and educational, while giving them a friendly vibe, which was very kind and helpful.

Also I would like to thank Professor Dionysios Pnevmatikatos for giving the opportunity to work on this very interesting field of research and for his support throughout the elaboration of this thesis.

Additionally I would like to thank Professor Apostolos Dollas and Associate Professor Ioannis Papaefstathiou, for taking the interest in my work and agreeing to evaluate it.

Last but not least I would like to thank the Theatrical Team of the university, without which my studies here would have been longer and more difficult and also my friends in Crete and in Athens for coping with me all these years.

# Contents

| Abstract                                                                     | ii  |

|------------------------------------------------------------------------------|-----|

| Acknowledgments                                                              | iii |

| 1 Introduction                                                               | 1   |

| 1.1 Field Programmable Gate Arrays                                           | 1   |

| 1.2 Partial Reconfiguration                                                  | 2   |

| 1.2.1 Module-Based Partial Reconfiguration                                   |     |

| 1.2.2 Difference-Based Partial Reconfiguration                               |     |

| 1.2.3 Applications of Partial Reconfiguration                                |     |

| 1.3 The Embedded Operating System Hypothesis and the Scheduling Issue        |     |

| 1.4 Thesis Contribution.                                                     |     |

| 1.5 Thesis Structure                                                         | 7   |

| 2 Related Work                                                               | 8   |

| 2.1 Related work regarding OS for partially reconfigurable FPGAs             | 8   |

| 2.2 Related work on Scheduling and Placement Algorithms                      | 11  |

| 2.3 Related work in the Technical University of Crete's Microprocessor and   |     |

| Hardware Laboratory                                                          |     |

| 2.4 Conclusion                                                               | 15  |

| <b>3 Development of scheduling algorithms for Partially Reconfigurable</b>   |     |

| FPGAs.                                                                       | 17  |

| 3.1 Basic Device Area Models                                                 | 18  |

| 3.2 A C-Language Implementation of Steiger's 1D Horizon Technique            | 18  |

| 3.3 A C-Language Implementation of Steiger's 1D Stuffing Technique           |     |

| 3.4 Expansion to the 2D model of Steiger's Stuffing Technique                |     |

| 3.5 The Technology Restriction that prevent the implementation of schedulers |     |

| realistic FPGAs                                                              |     |

| 3.6 Conclusion                                                               | 42  |

| 4 A Scheduling Algorithm targeting a realistic Partially Reconfigurab        | le  |

| FPGA                                                                         |     |

| 4.1 Scheduling ideas used in our Scheduling Algorithm                        |     |

| 4.2 Partial Reconfigurable Module Relocation on FPGA devices and its potenti |     |

| in Scheduling Algorithms                                                     |     |

| 4.3 The Partial Reconfigurable Module true FPGA size issue | 49 |

|------------------------------------------------------------|----|

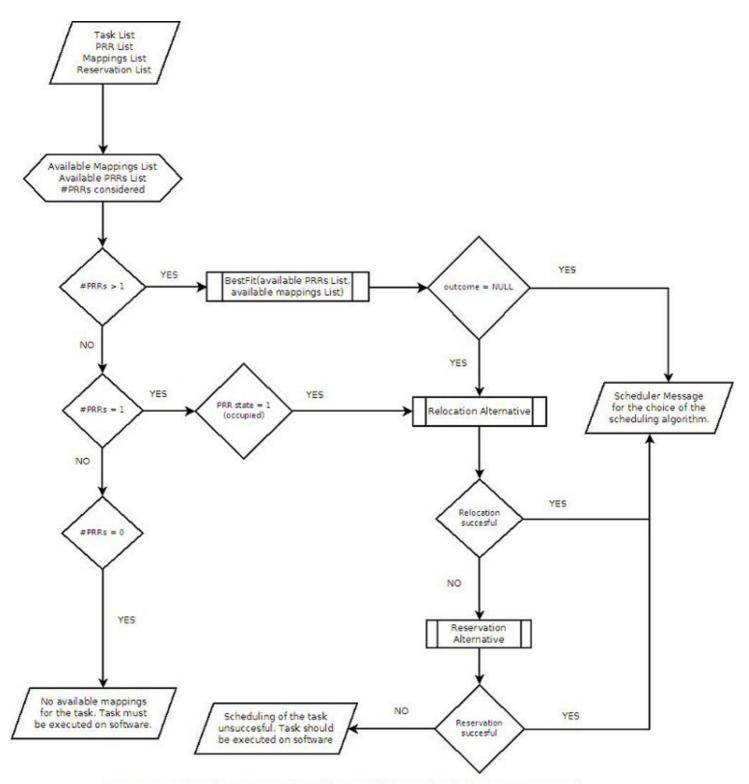

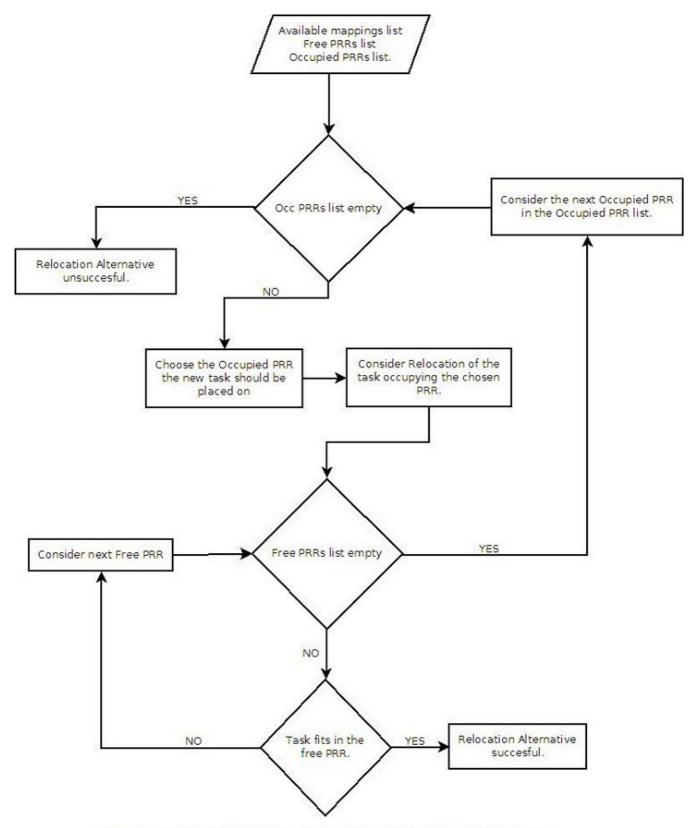

| 4.4 The Scheduler Analysis                                 | 51 |

| 4.5 Conclusion                                             |    |

| 5 Evaluating our Algorithm                                 |    |

| 5.1 Evaluations with our Task Sets                         |    |

| 5.2 Evaluations with task sets from other research groups  |    |

| 6 Conclusions and Future Work                              | 68 |

| Bibliography                                               | 70 |

### Chapter 1

### Introduction

In this chapter, an introduction is made about FPGAs, partial reconfiguration, scheduling and the problems regarding an embedded operating system. Also, a presentation is made regarding the subjects of this thesis.

### **1.1 Field Programmable Gate Arrays**

The Field Programmable Gate Arrays (FPGAs) are integrated circuits designed to by configured by the end-user, in order to execute different applications. The final FPGA configuration is specified, by using a hardware description language (HDL), similar to that used for an application specific integrated circuit (ASIC). FPGAs can be programmed to implement any logical function that an ASIC could perform. Over the years FPGAs have increased their popularity amongst users due to the ability to update their functionality after shipping, partial re-configuration of a portion of the design and the low non-recurring engineering costs relative to an ASIC design.

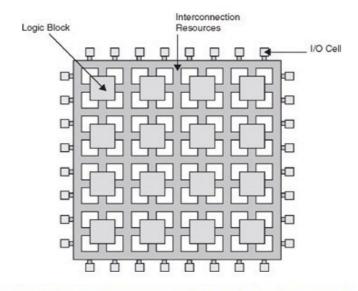

FPGAs contain programmable logic components called "configuration logic blocks" (CLB) and a reconfigurable network used for interconnection between those blocks. Logic blocks can be configured in order to perform complex combinatorial functions or simple logic gates like AND and XOR. Also this blocks can include memory elements like flip-flops or more complete blocks of memory and many other more specific pieces of hardware logic (dedicated multipliers, Block RAMs etc). A representation of the internal structure of an FPGA, is shown in Figure 1.1.

Figure 1.1: A graphic representation of the internal structure of a FPGA.

In the recent years, FPGAs have become a powerful tool, due to their many advantages and are broadly used in several applications such as, digital signal processing, softwaredefined radio, ASIC prototyping, medical imaging, computer vision, speech recognition, cryptography, bio-informatics, computer hardware emulation, radio astronomy, metal detection and a growing range of other areas.

### **1.2 Partial Reconfiguration**

Partial Reconfiguration (PR) is the process of changing the portion of a reconfigurable hardware circuitry. This can be done, either when the rest of the design is operational and the device is active (dynamic partial reconfiguration) or when the device is inactive (static partial reconfiguration). PR gives the ability to share the same hardware amongst different applications, increase resource utilization, update the hardware remotely and to adapt hardware algorithms. Some of the benefits of PR are:

- **Increased System Performance:** PR provides the ability, to the user, to use more efficient implementations of a design for different situations, while the rest of the system continues its execution without performance loss or disputed results during the reconfiguration process.

- **Reduced Power Consumption:** In power-constrained designs the user can simply download a more power-efficient version of a module, or a blank bitstream when the particular region of the device is not needed, therefore reducing the power

consumption of the design.

- Adaptability: Designs with the use of PR can adapt to changes in their environment, their input data or even their functionality. This capability makes the design more efficient, compared to a more generic one.

- Hardware Upgrade and Self Test: The ability to change hardware. Xilinx FPGAs can be updated at any time, locally or remotely. Partial reconfiguration allows the end user to easily support, service and update hardware in the field. Also with the use of self test components, the user can check, on demand, the integrity of the system. [1]

- Shorter reconfiguration times: The configuration time is directly proportional to the size of the configuration bitstream. Partial reconfiguration allows you to make small modifications without having to reconfigure the entire device. By changing only portions of the bitstream as opposed to reconfiguring the entire device the total reconfiguration time is shorter. [1]

The first device able to support partial reconfiguration of their circuitry was released by Xilinx in the mid 90s and it was the model XC6000. Since Xilinx has released many devices with the capability of partial reconfiguration ranging, from the high-end Virtex-6 to the low-end Spartan 3/E family. Xilinx supports two basic styles of partial reconfiguration, module-based and difference-based.

### **1.2.1 Module-Based Partial Reconfiguration**

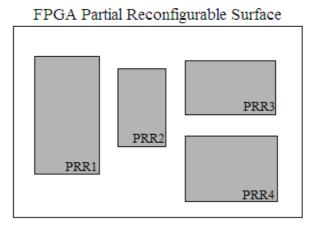

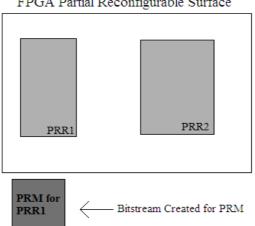

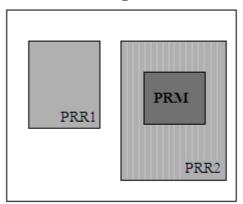

Module-based partial reconfiguration uses modular design concepts to reconfigure large block of logic. These modules are known as partially reconfigurable modules (PRM) and each of them implements a certain function or algorithm. These modules are loaded in certain regions, defined statically, called partial reconfigurable regions (PRR). In order to perform the loading of a PRM to a certain PRR the device needs information, which is encrypted in a file called partial bitstream. A partial bitstream is created at design time and is used to reconfigure a specified region with a PRM. It is important to note that a partial bitstream is in direct accordance, first to the PRM for which it was created and to the PRR, this PRM will be loaded on.

The communication access to the PRR is achieved through special pre-defined static buses called Bus Macros. These bus macros are the "gateways" through which all the System – PRM communication processes will occur, with the exception of clock signals. Bus macros can be placed, during compile time, on the boundaries of PRRs in order to

define pins where PRMs can hook themselves. These macros are made with pairs of CLBs; one side of the CLB pair is connected to a RR signal, while the other is connected to a static logic signal.

### **1.2.2 Difference-Based Partial Reconfiguration**

Difference-based partial reconfiguration can be used when a small change is made to the design, for example changing LUT equations or BRAM contents. In order to use this method the user needs to make modifications of the device layout and routing with the use of low-level software. The resulting partial bitstream contains only information about the differences, between the current design structure, that resides in the FPGA, and the new content of the FPGA. Despite the fact, that this method allows really fast reconfiguration it introduces two limitations:

- Difficulty to change the design's routing.

- It cannot be used with a wide range of applications, due to the fact that it applies only in simple designs.

#### **1.2.3** Applications of Partial Reconfiguration

As stated before partial reconfiguration is a very important ability the FPGAs offer and with the help of, have become more popular amongst users. Currently, many application domains are being studied, in order to explore the benefits gained from their implementation with partial reconfiguration technology. Currently PR is the cornerstone for power-efficient and cost-effective software-defined radios (SDRs) [2].

Another usage of partial reconfiguration is in the migration and recovery of single-event upsets (SEUs). More specifically applications that are space-based have a high probability of experiencing SEUs. With the use of partial reconfiguration, a system can detect and repair SEUs in the configuration memory of the device without disruption of its operations or completely reconfiguration of the FPGA.

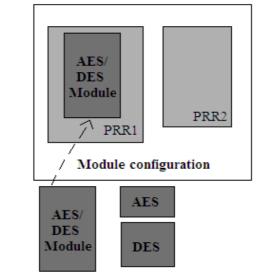

Implementation of cryptographic systems, can also benefit from the use of PR. PR in these systems gives the ability to support a range of cryptographic algorithms without the need of having them all integrated in the design. The system can swap algorithms in and out on demand with the use of PR. This not only makes these designs more simple but allows for more inexpensive FPGAs to be used, thus reducing the overall cost.

# **1.3 The Embedded Operating System Hypothesis and the Scheduling Issue.**

Since the first time Xilinx released FPGAs with the ability of dynamic partial reconfiguration, many research groups contemplated the construction of an operating system accommodated in a FPGA. More specifically, the goal of the research community, was to create an OS that would manage the hardware implementations of numerous tasks and their execution on hardware. The advantages of such an OS were many, first the hardware acceleration produced by the device would make certain processes run much faster that they would in software, also the portability of the device was a great asset, plus the fact that even without an embedded OS the FPGAs were experiencing a vast use amongst experienced and simple users. The first field the researchers worked on towards their goal of an embedded Operating System was the Scheduling Algorithms.

The term scheduling was first introduced to describe algorithms used for operating systems. The main job for a scheduling algorithm is to give access to threads, processes or data flows, to the system resources, mainly the CPU time or the memory. In real-time systems the scheduler is important to ensure that the processes can meet their deadlines. A good scheduler is characterized by its ability to keep fairness between the distribution of system resources to the several processes, a low declined processes rate, when our tasks have deadlines, good utilization of the device's resources and a low response time.

Thus, from the beginning a great deal of work was spent on the design of said Scheduling Algorithms for the OS. Instantly the researchers saw that the traditional Scheduling Algorithms derived from the software OS area could not work. The main problem was, that in hardware, we are concerned about the space used by a task in the device and as a conclusion, in order to plan tasks in the future; we need to implement a free space manager or placement manager, as it is usually referred to, inside the scheduling algorithm or in co-operation with the scheduling algorithm.

In those first attempts researchers tended to work towards the 2D area model. Despite the fact that the 2D area model was not yet available in the Xilinx devices, the researchers used it because it offered the ability to better manage the free space and produced less area fragmentation. The placement manager was responsible for finding, at each point in time, the maximum rectangles in the device. This problem can be compared to the 2D bin packing problem, which is known to be a combinatorial NP-hard problem. For this problem several solutions have been proposed, most of them consider different ways to

partition the device, in order to create maximum rectangles. Many of those works evaluate their solutions in a discrete time framework constructed in C language. At that time, the researchers choose that way to implement their designs because it seemed logical, the same program could run in the Microblaze processor inhabited in the device with minimum changes to the code, that has been already created.

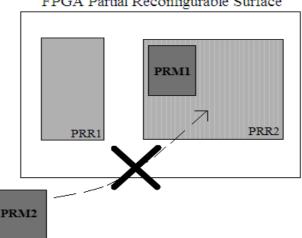

However after many attempts to a complete Embedded OS system inhabited in a Partially Reconfigurable FPGA, the researches tend to neglect other restrictions induced by the target device. First there is the PRRs restriction, which states that the device has to be pre-partitioned in PRRs, that clearly state the position a PRM while be accommodated on. Also it is important to state that a runtime change in those PRRs is not feasible.

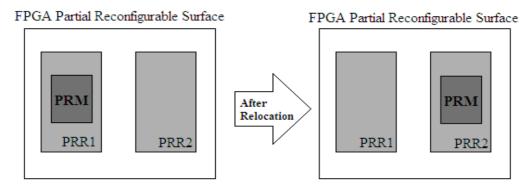

Second the FPGA has certain restrictions regarding the binding between a PRR and a PRM, that binding is done through the bitstream as it is necessary, in order for a PRM to be placed on a PRR, that a bitstream would be created that binds these two. Finally the researchers have made many wrong assumptions regarding the use of module relocation on modern FPGAs.

All the above, prevent the algorithms created thus far and that will be presented in Chapter 2, to be implemented and work on a realistic FPGA device, thus rendering them useful, only for theoretical work and research, or applicable on the future, when a different partial reconfiguration technology will be available.

### **1.4 Thesis Contribution.**

In this thesis we consider the module-based dynamic partial reconfiguration of a FPGA. This thesis studies the scheduling algorithms developed through the years for Reconfigurable Hardware Operating Systems and presents a novel scheduling algorithm we constructed.

With this work we attempt to create a scheduling algorithm that not only successfully schedules hardware tasks on a FPGA device, but also takes in consideration all the known restrictions induced by the device. That way this thesis offers one of the few complete and implementable scheduling algorithms for hardware tasks done so far.

More specifically the thesis's subjects are the following:

- First, we study previous scheduling algorithms along with other related work on the field of an Operating System inhabited in a FPGA.

- · Second, we present the results of our implementation off three scheduling

algorithms we chose to implement. The implementation of other scheduling algorithms was important in order to take ideas and gain useful knowledge on how to create efficiently a scheduling algorithm.

- Then, we discuss why any of the implemented or presented algorithms are not implementable in a realistic Partially Reconfigurable FPGA. Here we present also, a thorough analysis of each algorithm and which particular FPGA restrictions it violates.

- Moreover, we present a scheduling algorithm, we created, targeting a realistic FPGA with partial reconfiguration capability. The scheduling algorithm we created is implementable in almost any device, as it obeys to every known technology restriction, contrary to most of the current state of art.

- Finally, we implement and evaluate our algorithm on a simulating framework. The data we feed our framework with simulate one of the most well known technologically realistic FPGAs.

### **1.5 Thesis Structure.**

In Chapter 2 we will provide references and analysis of the related work used in this thesis, mainly the preexisting scheduling algorithms we studied and research work regarding the creation of an Operating System inhabited on an FPGA. In Chapter 3 we present, the implementations we made of three preexisting scheduling algorithms, along with a study of, why any of the algorithms presented or implemented, are not applicable in a realistic scenario. Also presented here are, the technology restrictions of the Partial Reconfiguration process. In Chapter 4 we present, our ideas regarding a novel scheduling algorithm obedient to the technology restrictions analyzed previously, which also uses the process of Module Relocation. In Chapter 5 we present evaluations we made on our algorithm not only with task sets created by us, but also with task sets taken from other researchers or similar to them. Finally, Chapter 6 summarizes our work and provides ideas for future modifications of the existing algorithm.

### Chapter 2

### **Related Work**

So far, several researches have been published regarding the implementation of scheduling and placement algorithms for hardware tasks. Also there are few projects trying to implement an Operating System based on a FPGA partially reconfigurable device. In this chapter we describe these works, we managed to collect information for and then we continue with the previous work, that has been conducted in the Microprocessor and Hardware Laboratory of the Technical University of Crete.

# 2.1 Related work regarding OS for partially reconfigurable FPGAs.

One of the first works, regarding the idea, of creating an operating system inhabited in a partially reconfigurable device was [3]. In this study J. Burns et al. depending on three different applications, manage to extract a set of common requirements and design a runtime system for managing the dynamic reconfiguration of FPGAs. The resulting system incorporates operating-system style services, that permit sophisticated and high level operations on circuits. Even though their work shows an understanding of the technology restrictions, some aspects of the above-mentioned high level operations on circuits are not yet applicable in current devices. However, despite the fact that, one might consider their job chronologically old regarding the knowledge the research community had for the technology restrictions induced by the FPGAs, they correctly consider that circuits can be downloaded at pre-defined, at compile time, areas on the

FPGA. Also the term "library of circuits", that is often mentioned in their work, is an important fact of the scheduling process. It is important in order to have a quality scheduler to have many choices in different implementations of the same circuit.

A more complete study regarding the advantages, that can be derived from the use of Partial Runtime Reconfiguration (PRTR) in high-performance reconfigurable computing is done in [4]. There, El-Araby et al. first analyzed the execution model of PRTR, exploring what are the key aspects that affect its performance and then experimentally verified his findings. This work showed that PRTR can become the trend for improving the performance, in high-performance reconfigurable computing, as the experiments showed that PRTR can be almost twice faster than the Full Runtime Reconfiguration (FRTR) alternative. Although the researchers had to assume that practical considerations induced by the technology, mainly the overhead induced by the slow ICAP, might overweight the gains. However with the potential future use of an *Operating System* it is clear that PRTR is far more beneficial than FRTR for versatility purposes, multitasking applications and hardware virtualization.

Shortly after, P. Lysaght, B. Blodget and J. Mason presented a partial reconfiguration design flow that helps the end-user efficiently create dynamic reconfigurable designs in [5], along with a description of some enhancements done to Xilinx FPGAs in order to provide better support for the creation of dynamically reconfigurable designs. Their work offers important insight, on the way a system should be built, in order to be implementable in a realistic partially reconfigurable device. Moreover the authors here present terms like PRR, PRR-PRM binding via a bitstream and device partitioning at compile time, that are crucial on understanding correctly the PR process.

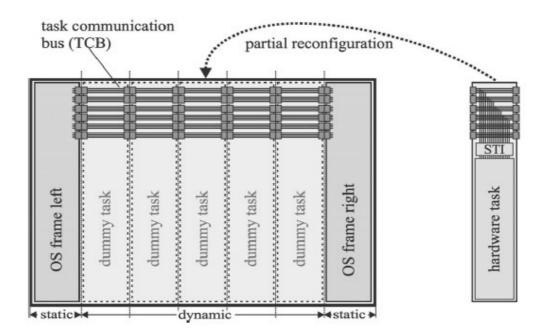

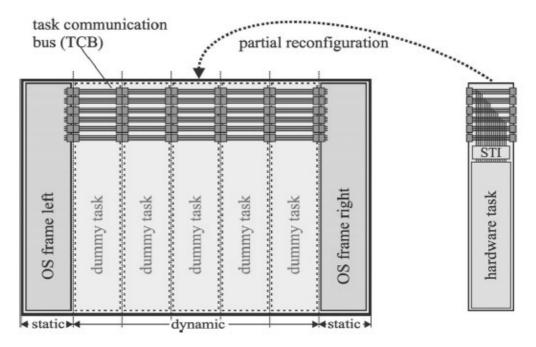

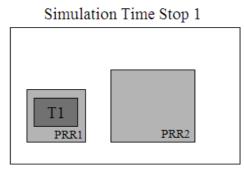

Also, a work regarding the implementation of an operating system can be found in [6]. In their work, H. Walder and M. Platzner, present a runtime environment that partially reconfigures and executes hardware tasks on a Xilinx Virtex device. Their implementation splits the reconfigurable surface of the device into vertical task slots that can accommodate hardware tasks. The static region that includes all operating system modules is organized into two OS frames. Also a bus-based communication infrastructure is created that allows tasks communication and I/O. A system graphical representation is shown in Figure 1. Their works has been tested in a Virtex-II device allowing for task partial reconfiguration and execution.

**Figure 2.1**: Here we see the system model presented by Steiger. In this Steiger considers pre-defined PRRs and a Task Communication Bus, based on hardware macros.

A work that has made all this possible can be found in [7], where B. Blodget et al. offered many insights towards the improvement of the already existing external reconfiguration control interface called internal configuration access port (ICAP). Their Self Reconfiguring Platform (SRP) defines two APIs. The lower level one is the ICAP API, which provides access to the configuration cache and controls reading and writing the cache to the device. The higher level API is the Xilinx Partial Reconfiguration Toolkit (XPART), which abstracts the bitstreams details providing access to select FPGA resources.

Although all these years many works have tried to create a complete runtime system for reconfigurable devices, the problem is that it has yet to penetrate the mainstream. The reason why this happens is examined in [8], where K. Compton and W. Fu also offer some solutions to this issue. According to their work, one of the biggest problem is the management of reconfigurable hardware in a multi-threaded environment. Also in their work they propose simple schedulers like, a *Most Frequently Used* scheduler, a *Best Fit* scheduler, both of which are based on simplistic greedy methods and a more complex *Multi-Constraint Knapsack* scheduler. These schedulers not only choose which kernels, i.e. hardware tasks, should be implemented in hardware for each scheduling interval, but also the specific hardware implementation for those kernels.

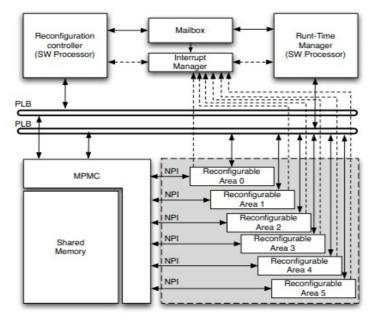

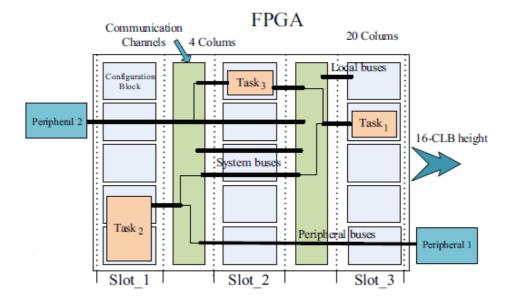

One of the most thorough works on the field of creating a complete Runtime Manager has been shown in [9]. In this paper a Run Time Manager (RTM) is introduced able to map multiple applications on the underlying hardware and execute them concurrently. The target architecture the researchers use for designing their system is shown in Figure 2. Moreover it is illustrated how to generate this RTM and how its modular implementation, along with the use of partial reconfiguration, allows the user to explore different policies regarding reconfiguration, task scheduling and resource assignment. Here the researchers take in consideration almost every restriction induced by the device and create a complete Runtime Manager that schedules task on the device. However one of the setbacks this work has is that the researchers do not consider deadlines for their tasks, which allows them to eventually place all the task on the FPGA.

Figure 2.2: The target architecture of the device the researchers used on [9].

# 2.2 Related work on Scheduling and Placement Algorithms.

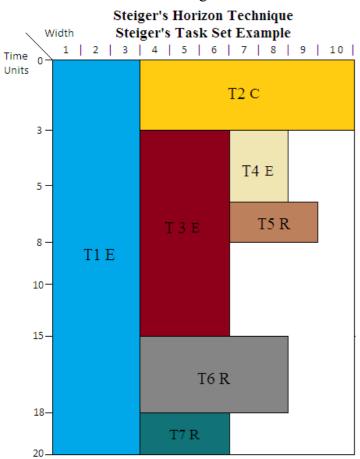

Many researchers after proposing their system have tried to create unique schedulers coupling them with that design. One of the first works in the field regarding a hardware task scheduling algorithm was done by C. Steiger et al. at [10]. Their work offered the first two online scheduling algorithms designed for operating systems for reconfigurable embedded platforms, which, since then, have influenced many researchers. In this paper, design issues for reconfigurable hardware operating systems are first discussed similar to the ones presented in [6]. Then for the 1D and 2D resource models the scheduling

problem is formulated and two heuristics, the *horizon technique* and the *stuffing technique* are presented. For evaluation, a discrete-time simulation framework has been devised. Further analysis of Steiger's *horizon* and *stuffing techniques*, as well as, our C-language implementation of these algorithms can be found in Chapter 3 of the current thesis.

A great deal of work in creating a scheduler for managing hardware tasks has been spent from T. Marconi et al. One of the first schedulers presented by this research group is in [11]. There T. Marconi and Yi Lu, inspired by Steiger's work in [10] and Y.-H. Chen and P.-A. Hsiung work in [12], create a scheduling and placement algorithm for partially reconfigurable devices. The main idea used by the algorithm is to place each task on the opposing side of the device in order to have more space in the middle and thus better space utilization. The proposed algorithm outperforms the existing algorithms in terms of reduced total wasted area up to 89.7%, has 1.5 % shorter schedule time and 31.3% faster response time. The simulation experiments where done by implementing several algorithms in ANSI-C and run them on a Pentium-IV 3.4 GHz PC using the same artificial task sets.

Furthermore, in [13] T. Marconi et al. present a novel 3D total contiguous surface heuristic, for equipping a scheduler with the "blocking-awareness" capability. The proposed algorithm tends to allocate tasks at positions where blocking of future tasks will be avoided, in order to achieve that, the algorithm calculates the horizontal and vertical contiguous surface between the new incoming task, previously or next scheduled tasks and the FPGA boundary. The main idea of the algorithm is to compactly pack the tasks on the device. The resulting algorithm is evaluated in a discrete-time simulation framework in C.

Moreover, in [30] T. Marconi et al. present the scheduling algorithm that encompasses the 3D total contiguous surface heuristic. However this algorithm is also applicable in 3D Partial Reconfigurable FPGAs, mainly the Virtex-6 family. Nevertheless we can see that the logic of the algorithm is easily applicable to 2D Partial Reconfigurable FPGAs too. The algorithm presented first tries to pack compactly on the device the tasks on space and then in time, thus maximizing the acceptance rates. The resulting algorithm was evaluated in a discrete-time simulation framework in C.

In addition Yi Lu and T. Marconi have created, in [14], the first scheduling algorithm that takes into account the data dependency and the data communication, amongst hardware tasks and between hardware tasks and external devices. The algorithm has three steps,

first a suitable placement for the task is found regarding its size, then the configuration port is checked for any conflicts and finally the task is scheduled in a free time and space slot, in accordance with, its communication requirements. The resulting algorithm is evaluated in a discrete-time simulation framework in C.

In order to create an efficient scheduling algorithm, it is very important to create an equally efficient placement algorithm. The speed and the quality placement of hardware tasks on the device, in addition to the proper free space management, are very important attributes, not only for a good online placement algorithm, but also for a good scheduler. Actually those issues have been the first thing researchers examined when the partial reconfiguration feature became available. In order to be more accurate, almost every proposed scheduling algorithm comes along with a placement one.

A very important work on this field is presented in [15]. There K. Bazargan et al. offered the first methods and heuristics for fast and quality online and offline placement of templates on reconfigurable computing systems. The methods introduced here, were the main inspiration for many placement algorithms created in the future. Also the work done by Bazargan here, offers the first proof that, the creation of many representations of the same PRM (library of bitstreams) can improve up to 10% the system's acceptance rate.

Also in the field of task placement a highly respectable work was presented by K. Compton and et al. in [29]. There K. Compton inspired by the concept of task relocation proposes several techniques, that optimize the already existing process. Those techniques include several task transformations in order to achieve better defragmentation via task relocation. However, the transformations proposed here were not applicable at the time so K. Compton proposes a new Relocation Architecture, that implements and fully exploits the benefits of her proposed transformations.

H. Walder, C. Steiger and M. Plantzer in [16] try to create methods that outperform the ones introduced by K. Bazargan and are focused on finding efficient ways to partition the reconfigurable resources space, as well as, creating a hash matrix data structure to maintain the free space. More specifically the researchers try to avoid the direct partitioning of the device after the insertion of a PRM and maintain a series of overlapping rectangles. According to simulations, which were made in a discrete time simulation framework, their placement methods offer an improved placement quality against previous art in the field.

In [17] H. Walder and M. Platzner focus on a major aspect of a reconfigurable operatingsystem; task placement and transformation. First they discuss the task characteristics and system models, and then they investigate task placement techniques for non-rectangular, coarse-grained tasks and propose footprint transforms; that change task shapes, in order to find possible mappings. However, many of the proposed footprint transformations are not realistic, due to the complexity of the re-routing process.

In [18] T. Marconi and Yi Lu propose three techniques regarding space management: Merging Only if Needed (MON), Partial Merging (PM), and Direct Combine (DC). These technique focus on the merging of non-overlapping empty rectangles, created by the placement of a task on the device and the partitioning done by its placement. The algorithm proposed uses the above techniques dynamically to exploit their advantages. For their simulations they constructed in a discrete-time simulation framework in ANSI-C, to evaluate the performance of the proposed techniques and compare it to related art.

Also, in [19] T. Marconi et al. present a new strategy for online placement algorithms on 2D partially reconfigurable devices, termed the Quad-Corner. The main difference between QC and other work in the field are the abilities of quad-corner spreading of the tasks in the reconfigurable surface, i.e. the algorithm spreads the hardware tasks close to the four corners of the device thus maximizing the free area in the middle, an idea also used in [11]. The resulting algorithm is evaluated in a discrete-time simulation framework in C.

In [20] T. Marconi et al. present yet another task placement algorithm. Their goal is first to exploit the fast search capabilities, offered by the pre-partitioned model. For that purpose in their work the FPGA is pre-partitioned into three different size logic blocks, small, medium and large. Also in order to manage the FPGA resources more efficiently the algorithm performs split, merge and recover operations. Even though the first premise of this algorithm is obedient to the FPGA restrictions (pre-partitioning model), the operations done during runtime by the algorithm are in violation of other FPGA restrictions. The algorithm is programmed using C language, and executed under Linux 2.6 with Intel(R) Pentium(R) 4 CPU 3.00GHz.

Finally in [21] A. Montone et al. try a different approach in hardware task placement and space management. Their work focuses on a resource- and configuration-aware floorplacement framework, using an objective function, based on external wirelength. Their simulations showed a great reduction in wirelength and a huge reuse probability of existing links, i.e. pre-placed, at design time, bus macros, but has introduced significant area fragmentation.

# 2.2 Related work done in the Technical University of Crete's Microprocessor & Hardware Laboratory.

In the works presented above, several aspects of reconfiguration time, throughput and the overall performance of partial reconfiguration in FPGA systems, are vague and often wrong assumptions are made by the researchers. Also, there is no clear clarification of the metrics used to evaluate the scheduling and/or the placement algorithms presented. For example, the assumptions made by T. Marconi et al. at [18] regarding the reconfiguration time of a task are very simplistic. Also the term "quality of placement" is yet undefined. T. Marconi et al. in all of their work consider the placement quality a measure defined by the total wasted area in a reconfigurable device during scheduling, whereas H. Walder et al. in [16], focus more on the *total execution time* of the algorithm and the *average waiting time* of the scheduled tasks. Additionally it is proven to be really difficult for researchers to determine the *penalty factor* induced to a system from executing a task's software implementation instead of its hardware one. For example in [15] K. Bazargan simply multiplies a declined task's dimension with the time that it would be accommodated on the device.

However in our lab a substantial amount of work has been made in order to clarify these aspects of reconfiguration. In [22] and [23] K. Papademetriou et al. offer detailed descriptions of how reconfiguration works internally and an exact cost model that measures accurately the time spent in the reconfiguration process and the actual throughput of FPGAs. That way, we can have a more specific way of measuring the overhead introduced in the system by the scheduling algorithms.

Moreover in [24] the researchers discuss the feasibility for keeping transparent the acceleration of certain kernels to the user, by injecting automatically configuration bitstreams into the FPGA co-processor. Also, in [25] and in more details in [26], K. Papademetriou and A. Dollas present a novel idea, regarding task prefetching and preloading in dynamically reconfigurable processors that can prove very beneficial in future scheduling algorithms.

### **2.3 Conclusion**

As presented above, many researchers have proposed and created many scheduling algorithms, placement algorithms, for managing hardware tasks on a FPGA based

partially reconfigurable operating system, and complete runtime systems inhabited in partially reconfigurable devices. However, as we can see from the above descriptions of these works, very few of the scheduling and/or placement algorithms have been evaluated using an actual partially reconfigurable device. On the contrary most of them, if not all, have been evaluated using a C-language discrete-time framework.

That is due to the inability of those designs to be implemented on a realistic FPGA device, which derives from the technology restrictions neglected, while creating the algorithms. Also almost all of the works listed, have made many and sometimes oversimplifying assumptions regarding the partial reconfiguration process.

In Chapter 4 of this thesis, those assumptions will be presented, additionally with the technology restrictions and we will present, why most of the above-mentioned works cannot be implemented in a real device.

# **Chapter 3**

# **Development of scheduling algorithms for Partially Reconfigurable FPGAs.**

In this Chapter, after studying and analyzing the most notable works on the field of hardware task scheduling in partially reconfigurable FPGAs, we will present three scheduling algorithms implementations, we made. The algorithms implemented, in C language, and presented here are:

- Steiger's 1D Horizon Technique

- Steiger's 1D Stuffing Technique

- Steiger's 2D Stuffing Technique, with Bazargan's Shorter Segment Heuristic

Our work was focused on Steiger's algorithms, because these algorithms are the ones that influenced most of the following work done on the area. First, we briefly analyze the two main models used for the mapping of tasks in a reconfigurable device. Then we present and analyze our implementations of the above-mentioned algorithms and we continue analyzing, if any of these algorithms, along with the algorithms presented in Chapter 2 are implementable in a realistic Partially Reconfigurable FPGA. Finally we begin the discussion of the restrictions induced by the FPGA technology and how these restrictions affect the implementation of, almost every algorithms presented. It must be noted that all the schedulers presented in this Chapter consider tasks with deadline, i.e. a task must complete its execution before its deadline time is met.

### **3.1 Basic Device Area Models.**

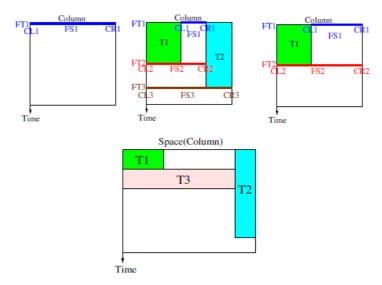

The complexity of mapping tasks to devices depends heavily on the area model used. In the area of Reconfigurable Computing two area models are commonly used from researchers. In the simpler 1D area model, tasks can be placed anywhere along the horizontal device dimension, the vertical dimension is fixed and covers the total height of the hardware task area. Despite the fact that the 1D area model leads to simplified scheduling and placement problems, it suffers from two types of external fragmentation.

The first one occurs when the hardware tasks do not utilize the full height of the reconfigurable area. The second one occurs when the remaining area is split into several small but non adjacent vertical stripes. The creation of external fragmentation is a huge disadvantage of scheduling algorithms as it can prevent the placement of a task on the device, despite the fact that enough area exists.

The more complex 2D area model allows us to place hardware tasks anywhere on the reconfigurable area and thus creates less external fragmentation. As a result, the 2D area model, offers higher device utilization.

# **3.2 A C-Language Implementation of Steiger's 1D** Horizon Technique.

In [10] Steiger et. al presented the Horizon Technique, which was the first attempt in creating an online scheduling algorithm designed for operating systems targeting reconfigurable embedded platforms. Our C-language implementation of the 1D Horizon Technique will be presented in this section.

The 1D Horizon Technique maintains three linked lists, the *reservation* list, the *execution* list and the *scheduling horizon*. The reservation list (R) holds the currently scheduled, but not yet executed tasks, the list entries the task's number, its placement and its starting time and is sorted according to increasing starting times. The execution list (E) hold all the currently executing tasks, the list entries, the task's number, its placement and its finishing time, the list is sorted according to increasing finishing times. Finally the scheduling horizon list (H) consists of all the intervals  $[x_I, x_J]$  in the device with their release times. In order for such an interval to exist in the list at a certain point in time, it must not be occupied after its release time, by any task neither in the reservation nor execution lists, the list is sorted according to increasing release times. The linked lists are

a very useful structure in maintaining the data needed for the scheduling process. An example of the lists state at a random point in the algorithms execution time can be seen in Figure 1.

$$\begin{array}{l} \underline{t=x}; H = \{ [1,5] @20, [5,10] @14 \} \\ E = \{ (\mathrm{T}_2, 5, 10), (\mathrm{T}_3, 1, 14) \} \\ R = \{ (\mathrm{T}_4, 5, 10), (\mathrm{T}_5, 7, 10), (\mathrm{T}_6, 1, 14) \} \end{array}$$

**Figure 3.1:** A graphical representation of the lists used in the *Horizon Technique* at a random point in the execution of the algorithm.

The Horizon Technique's main execution flow can be described in three steps. At each time the online method first checks for terminating tasks, i.e., tasks with finishing time equal to the current time. Then reserved tasks with starting time equal to the current are removed from the reservation list and added to the execution list. Finally for each newly arrived task the scheduling function is called, which either accepts a task, therefore adding it to the reservation list, or rejects it.

When a new task arrives the scheduler walks through the list of all horizon intervals with release times equal to the arrival time of the task and checks whether the task can be appended in the horizon. At any point of this walk the scheduler maintains a new list L, which contains all these intervals (line 2). Then the scheduler calls the *BestFit* function (line 4), which selects the smallest interval from the L list, that is large enough to accommodate the new task, the function then returns either an empty set, when no such interval exists, or the placement x for the task. If such a placement exists, the task is added to the reservation list, if not the schedulers proceeds to the next release time of the horizon list and merges adjacent horizon intervals with this release time. If at any point, the next release time is bigger than the latest starting time of the task, the task is rejected. A task's latest starting time is calculated, by the scheduler, and it is the difference between its deadline time and its execution time. As a result the task's scheduling period is the time interval [arrival time, latest starting time]. The pseudocode for the horizon scheduler is shown in Algorithm 1.

#### Algorithm 1: 1D Horizon Scheduler $\sigma_{1D-horizon}(T_i, H)$

| 1.            | $t \leftarrow a_i$                              |  |  |  |

|---------------|-------------------------------------------------|--|--|--|

| 2.            | $L \leftarrow$ horizon interval with $t = t_r$  |  |  |  |

| 3.            | <b>while</b> $(t \le s_{i-latest})$ <b>do</b>   |  |  |  |

| 4.            | $x = BestFit(L, w_i)$                           |  |  |  |

| 5.            | if $x \neq 0$ then                              |  |  |  |

| 6.            | add reservation( $T_i$ , $x$ , $t$ )            |  |  |  |

| 7.            | return(ACCEPT)                                  |  |  |  |

| 8.            | end if                                          |  |  |  |

| 9.            | $t \leftarrow t_r$ of the next horizon interval |  |  |  |

| 10            | $. \qquad L \leftarrow MergeIntervals(L, H, t)$ |  |  |  |

| 11. end while |                                                 |  |  |  |

**12.** *return*(REJECT)

In order to make the scheduler more easy-to-understand many functions were created. The main functions were, *schedule, BestFit, MergeIntervals* and all the functions needed for list management, i.e. add, remove and print. All these were the functions that were presented by Steiger, however there is another one, that is not mentioned on Steiger's work. That is the *UpdateHorizon* function, which must be called after every function that performs a change in the execution and/or the reservation lists. After this analysis we continue to the implementation of the scheduler. At the first phase we tried to maintain the order that Steiger suggested in his work, first check for terminating tasks, then execute waiting tasks and finally schedule.

After many tries it was concluded that in a C simulation of the scheduler this order cannot be maintained. In C things are done sequentially or the use of threads and multiprogramming is required. The main problem with Steiger's order was that when a task arrives at t\_sim=x, it is scheduled with t\_start=x. Therefore, this task will never be added to the execution list, because the scheduling at Steiger's order is done at the end, so when the algorithm tries to add the task to the execution list t\_sim would be x+1, which will be different from the starting time assigned to the task. Thus, we decided to first schedule tasks, then complete the execution of any finishing tasks and finally add starting tasks to the execution list.

Subsequently, we began the development of the four above-mentioned functions. While

Steiger fully explains the way, the *schedule* function works, the absence of pseudocode for the *BestFit, MergeIntervals* functions, required some improvisations. That was more necessary with the *UpdateHorizon* function's implementation, which is based in an original idea of ours.

The *schedule* function's inputs are: the task to be scheduled, the horizon list and the maximum width of the reconfigurable region. The function returns a pointer to a structure consisting of the task's placement, starting time, number and a number representing whether the task has been accepted or not. The way the function works is exactly as described by Steiger, with no modifications made by us.

The *BestFit* function's inputs are: the *L* list, which consists of horizon intervals, the task's width, the current scheduling time, i.e. the current *L* intervals' release time, and the maximum width of the reconfigurable region. The function walks through the *L* list trying to find the smallest interval, that can accommodate the scheduled task. If found the function returns the  $x_I$  value of the interval, as the placement of the task or the value -1, if no such interval exists.

The *MergeIntervals* function's inputs are: the current L list, the horizon list and the time t at which the merging will occur. For each horizon interval X in the horizon list with release time equal to t the function checks all the horizon intervals with equal or lower release times and if they are adjacent to X it merges them. After all the intervals are checked with X, the final merged interval is added to the L list and the next horizon interval undergoes the same processing, only if it was not one of the intervals that X was merged with. Upon completion the function returns the head of the L list.

Finally, we explain, the *UpdateHorizon* function, which was the most demanding function to implement as there was no description of it in Steiger's paper. The only information for the function, was its functionality:

• The UpdateHorizon function updated the horizon list with adding or removing intervals according to the current state of the reservation and execution lists.

From that first description of the function its inputs were determined; the reservation list, the execution list, the task list, in order to have specific information for every task, the current simulation time and the maximum width of the reconfigurable device. First a temporary horizon list with one-width intervals [0, x] and release time the current simulation time is created, that fully partitions the spatial resource dimension.

Then every interval is cross-checked with all the entries of the reservation list, if at any point any task uses the interval, its release time is set as the maximum finishing time, i.e.

the starting time of the task, plus its execution time. Then upon completion of the check, the new interval was added in the temporary horizon list. The same check is performed with the tasks in the execution list. After these checks the temporary horizon list consists of many one-width intervals with various release times, in order to list every interval only once we kept in the list only the one-width intervals with their maximum release times. Finally the adjacent intervals with same release time were merged and the resulting interval was added to the horizon list. The final horizon's list head was the output of the function.

The other functions needed for the completion of the Horizon Scheduler were trivial list management functions, for each list used in it. In order to examine the accuracy of our implementation, we created a task set same to the one Steiger uses in his paper, then we cross-checked the state of the reservation, execution and horizon lists, at simulation times 1, 2, 3 and 21 with Steiger's. The task set we created is shown below:

| Task      | Arrival Time | Execution Time | Deadline | Width | Height |

|-----------|--------------|----------------|----------|-------|--------|

| T1        | 0            | 20             | 30       | 3     | 3      |

| T2        | 0            | 3              | 10       | 7     | 5      |

| Т3        | 1            | 12             | 15       | 3     | 5      |

| <b>T4</b> | 1            | 3              | 10       | 2     | 2      |

| T5        | 2            | 2              | 10       | 3     | 4      |

| <b>T6</b> | 2            | 3              | 20       | 5     | 1      |

| T7        | 3            | 2              | 20       | 3     | 2      |

**Steiger's Task Set Table**

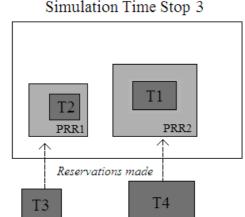

The above task set produced the same results as Steiger mentions in his work. At Figure 2 a graphical representation of the reconfigurable area after the arrival and scheduling of all the tasks is shown.

Thus having confirmed the functionality of the Horizon Technique we proceeded in testing the Horizon Technique in a corner situation, where it produced high space and time fragmentation. The task set we constructed was:

| Task      | Arrival Time | Execution Time | Deadline | Width | Height |

|-----------|--------------|----------------|----------|-------|--------|

| T1        | 0            | 5              | 20       | 10    | 2      |

| T2        | 0            | 10             | 15       | 3     | 4      |

| Т3        | 1            | 3              | 10       | 2     | 2      |

| T4        | 1            | 3              | 10       | 4     | 2      |

| T5        | 1            | 3              | 15       | 3     | 5      |

| <b>T6</b> | 2            | 4              | 20       | 10    | 3      |

| <b>T7</b> | 3            | 3              | 20       | 3     | 2      |

**High Fragmentation Task Set Table**

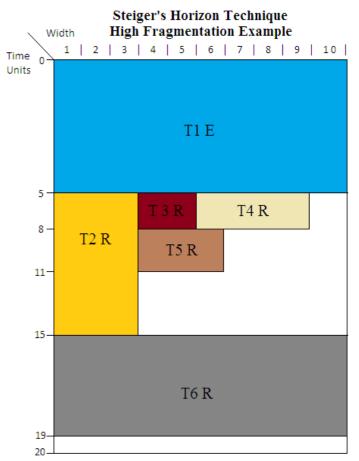

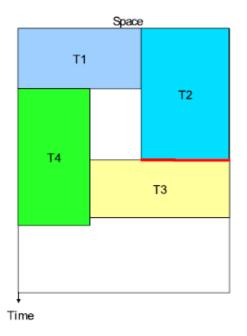

With this task set the Horizon Technique has one rejected task (T7). Although if we observe the scheduling process and the utilization of the reconfigurable area it is clear that this rejection can be avoided. More specific at  $t_sim=2$  the reconfigurable area is shown in Figure 3.

**Figure 3.2:** A graphical representation of the reconfigurable area at t\_sim=3. The E means that the task is currently in execution, the R means it is reserved and the C means the task is completed

**Figure 3.3:** A graphical representation of the reconfigurable area at t\_sim=2. The E means that the task is currently in execution, the R means it is reserved. In this example task 7 is rejected.

When Task 7 arrives plenty of area exists in the device for it to be accommodated in. In fact two placements for T7 can be found, either placement 7 with starting time 8 or placement 4 with starting time 11, but instead the task rejected. In order to understand why that happens, we need to observe the Horizon List, the algorithm produces. Specifically the Horizon List after the scheduling of T6 is:

#### \*\*\*\*\*HORIZON LIST\*\*\*\*\*

Horizon interval x1 1, x2 10, release time 19.

So the Horizon Technique, in order to list an interval at the Horizon List, needs the interval to be free from the time of its release and to not be occupied afterward, as mentioned before.. That is the reason why the intervals 8-9 at release time 8 and 4-6 at release time 11 are not considered as possible entries in the Horizon List, as both of them are later occupied by Task 6. That is the main disadvantage of the Horizon Technique as it produces high area fragmentation.

# **3.3 A C-Language Implementation of Steiger's 1D Stuffing Technique.**

In the previous section we presented Steiger's Horizon Technique. It should be acknowledged that the Horizon Technique has faults, especially regarding the free area management. However it was a first attempt from Steiger to successfully schedule hardware tasks in a partially reconfigurable device. Having realized the disadvantages induced by the maintenance of the Horizon List, Steiger tried to make the area management process more efficient, the resulting algorithm was the Stuffing Technique. In this section we present our C-language implementation of the 1D Stuffing Technique.

The Stuffing Technique also maintains three linked lists, the *reservation* list, the *execution* list and the *free space list*. The reservation (R) and execution (E) lists hold the appropriate information for each task listed in one of them, task number, starting time, placement for the reservation list and task number, finishing time, placement for the execution list. Finally the free space list consists of all the intervals  $[x_1, x_3]$  that identify currently unused resource intervals in the device, sorted according to increasing *x*-coordinates. The main difference between the Horizon and the Stuffing Technique can be seen in the *free space list*, while in the Horizon Technique the intervals are list only if

there release is permanent until the current time, in the Stuffing Technique lists the all the intervals that are currently unused, regardless of whether or not they will be used in a future time.

The scheduling sequence for the Stuffing Technique is the same as the Horizon one, first the algorithm checks for terminating tasks, i.e. tasks with finishing time equal to the current time. Then reserved tasks with starting time equal to the current are removed from the reservation list and added to the execution list. Finally for each newly arrived task the scheduling function is called which either accepts a task, therefore adding it to the reservation list, or rejects it.

When a new task arrives, the scheduler starts walking through the task's planning period, simulating all future allocations of the device, by simulating future task terminations and starts together with the underlying free space management. In line 1 of Algorithm 2, the current free space is copied to a simulated free space list, which is then modified during the scheduling process. At any given time, the scheduler first checks for terminating tasks and then reserved tasks are started. In line 12, the function *BestFit* returns all the intervals in the simulated free space list that can accommodate the newly arrived task or returns an empty set if no such interval exists. The reported intervals are then checked for conflicts with existing reservations in a best-fit order. If an interval without conflict is found, Ti is accepted and the planning stops. Otherwise, the scheduler proceeds to the next event, until the end of the scheduling period of the task. The pseudocode for the Stuffing Technique is shown in Algorithm 2.

#### Algorithm 2: 1D Stuffing Scheduler $\sigma_{1D-Stuffing}(T_i, F)$

| <b>1.</b> $F_s \leftarrow F$ ; $t \leftarrow a_i$         |              |  |  |  |

|-----------------------------------------------------------|--------------|--|--|--|

| <b>2.</b> <i>check</i> $\leftarrow$ TRUE                  | <b>2.</b> ch |  |  |  |

| <b>B. while</b> $(t \leq s_{i-latest})$ <b>do</b>         | 3. w         |  |  |  |

| $for all T_j \varepsilon E with (f_j = t) do$             | 4.           |  |  |  |

| 5. TerminateTasks $(T_j, F_s)$                            | 5.           |  |  |  |

| <b>6.</b> <i>check</i> $\leftarrow$ TRUE                  | 6.           |  |  |  |

| 7. end for                                                | 7.           |  |  |  |

| <b>6.</b> for all $T_j \varepsilon R$ with $(s_j = t)$ do | 8.           |  |  |  |

| <b>9.</b> $StartTask(T_j, F_s)$                           | 9.           |  |  |  |

| 10. end for                                               | 10.          |  |  |  |

| 1. if check then                                          | 11.          |  |  |  |

| <b>12.</b> $X \leftarrow BestFit(F_{s}, w_{i})$           | 12.          |  |  |  |

| 13.                               | for all $(x \in X)$ do                                              |  |  |

|-----------------------------------|---------------------------------------------------------------------|--|--|

| 14.                               | <b>if</b> (( $x$ , $t$ , $x+w_i$ , $t+e_i$ ) is not conflicting any |  |  |

|                                   | reservation in <i>R</i> ) then                                      |  |  |

| 15.                               | add reservation $(T_i, x, t)$ to R                                  |  |  |

| 16.                               | return(ACCEPT)                                                      |  |  |

| 17.                               | end if                                                              |  |  |

| 18.                               | end for                                                             |  |  |

| 19.                               | $check \leftarrow FALSE$                                            |  |  |

| 20.                               | end if                                                              |  |  |

| 21.                               | $t \leftarrow$ next event form $E \cup R$                           |  |  |

| 22. ei                            | nd while                                                            |  |  |

| <b>23.</b> <i>return</i> (REJECT) |                                                                     |  |  |

This scheduler was also created with the use of many functions for increased efficiency and less complexity. A first examination showed that the needed functions were, *schedule, BestFit* and all the functions we needed for list management, i.e. add, remove and print. However after careful consideration two functions that are not mentioned by Steiger were found. The first was the *UpdateSpace* function, which is called after every function that performs a change in the execution list. The second was the function *check\_conflict*, which is used inside the *schedule* function, but we decided it would be better if implemented as a separate function, in order to have better classification of the functions in our scheduler.

Subsequently we began the development of the four above-mentioned functions. While Steiger fully explains the way the *schedule* function works, the absence of pseudo code for the *BestFit* function, required some improvisations. Although the implementation of the *BestFit* function is the same as the one in the Horizon Technique, the *UpdateSpace* and the *check\_conflict* functions, were solely based in our ideas.

The *schedule* function's inputs are: the task to be scheduled, the tasks list, the execution and reservation lists and the free space list. The function returns a pointer to a structure consisting of the task's placement, the task's starting time, the task's number and a number representing whether the task has been accepted or not. The way this function works is exactly as described by Steiger, with no modifications made by us. Though some extra logic was added to this function, for example we constructed a new linked list, called *events* which holds the times of each event in the reservation and execution lists and also adds the finishing event time of a simulated starting task during scheduling. The *BestFit* function's inputs are: the simulated free space list, i.e. the  $F_s$  list and the task's width. The function walks through the free space list trying to find intervals that can accommodate the scheduled task. The function returns the set of intervals found or an empty set if no such interval exists.

Next the *UpdateSpace* function, which was the most demanding function to implement as there was no description of it in Steiger's paper, is presented. The only information for the function, was its functionality:

• The UpdateSpace updated the free space list with adding or removing intervals according to the current state of the execution list.

From that first description of the function we determined its inputs; the execution list, the task list, in order to have specific information for every task, and the maximum width of the reconfigurable device. In the beginning, every one-width interval that fully partitions the spatial resource of the device, i.e. from interval [0,0] to [x, x], where x the maximum width of the reconfigurable area, is cross-checked with all the entries in the execution list. If any task in the execution list uses the interval, the interval is not added in the temporary free space list. After this check the temporary free space list consists of many one-width intervals, for every adjacent interval we perform a merge and then the merged entry is added to the free space list which is the output of our function. If no tasks exist in the execution list then the function returns a set, which contains the whole width of the device.

Finally the *check\_conflict* function was implemented. The function's inputs are: the set of intervals produced by the *BestFit* function, the time during which the check occurs, the reservation list and the scheduled task. For each interval in the intervals list the function checks, if it conflicts in space and in time with any entry in the reservation list. If the above conflict occurs the interval is rule out, as a suitable placement option for the task. If more than one intervals are eligible for placement the choice between them is done with a best-fit fashion.

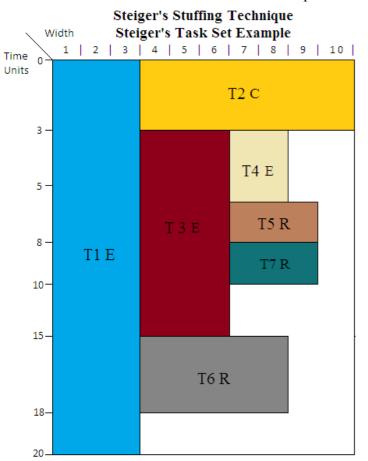

The other functions needed for the completion of the Stuffing Scheduler were trivial list management functions, for each list used in it. In order to examine the accuracy of our implementation, we created a task set same to the one Steiger uses in his paper, then we cross-checked the state of the reservation, execution and free space lists, at simulation times 1, 2, 3 and 21 with Steiger's. The task set we created is the same as the one used in Section 3.2. The task set produced the same results as Steiger mentions in his work. At Figure 4 a graphical representation of the reconfigurable area after the arrival and scheduling of all the tasks is shown.

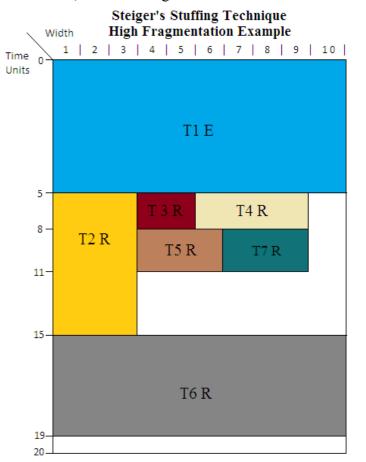

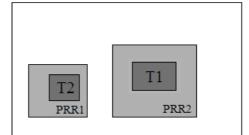

Steiger introduced the Stuffing Technique in order to correct certain drawbacks he had in the Horizon Technique. One of them was the necessity for the Horizon Technique to consider intervals that were free must be appended to the horizon. That rule created high fragmentation in many tasks sets we created. When the input to the Stuffing Technique was the high fragmentation task set used in Section 3.2, all tasks were successfully scheduled and the device's space was utilized much better, as seen in Figure 5.

**Figure 3.4:** A graphical representation of the reconfigurable area at t\_sim=3. The E means that the task is currently in execution, the R means it is reserved and the C means the task is completed

Figure 3.5: A graphical representation of the reconfigurable area at  $t\_sim=2$ . The E means that the task is currently in execution, the R means it is reserved. In this example task 7 is accepted.

Another advantage found in Stuffing is that the scheduler can handle well tasks, with really small deadlines. In order to show that we created the task set show bellow.

| Task      | Arrival Time | Execution Time | Deadline | Width | Height |

|-----------|--------------|----------------|----------|-------|--------|

| T1        | 0            | 4              | 10       | 2     | 3      |

| T2        | 0            | 14             | 20       | 4     | 5      |

| T3        | 1            | 4              | 15       | 4     | 5      |

| T4        | 2            | 2              | 6        | 2     | 2      |

| T5        | 2            | 2              | 10       | 3     | 4      |

| <b>T6</b> | 2            | 3              | 17       | 5     | 1      |

| <b>T7</b> | 3            | 2              | 8        | 2     | 2      |

#### **Small Deadlines Task Set Table**

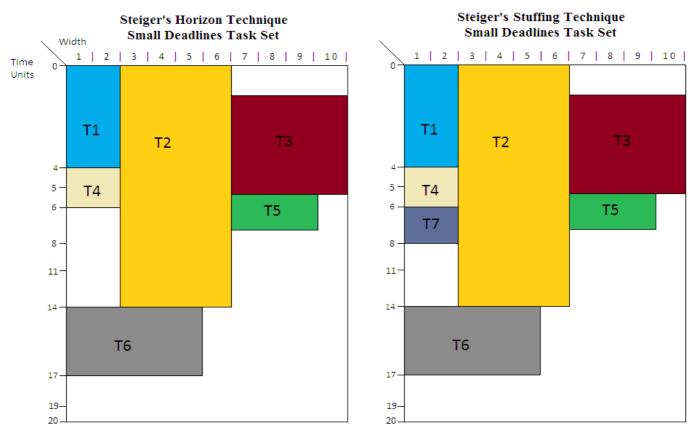

In the above task set we can see that task 7 has a scheduling period of only 3 time units, while task 4 has a scheduling period of only 2 time units. When in this task set the Horizon Technique, is applied, task 7 is rejected, because although there is space in the left side of the device, the deadline of the task is not met. Also we can see that there is space in the right side of the device also, but the Horizon algorithm dismisses that space as it is not free in the entire time horizon.

**Figure 3.6:** A graphical representation of the reconfigurable area after the arrival of all the tasks. We can see that although enough space exists for the planning of task 7, the Horizon Technique rejects it, while the Stuffing Technique accepts it.

When the Stuffing Technique is applied to that task set, all the tasks are scheduled successfully. The device after the arrival of all the tasks for the two algorithms is shown in Figure 6.

## **3.4 Expansion to the 2D model of Steiger's Stuffing** Technique.

The algorithms described so far are designed for the 1D model of a reconfigurable device. However the space utilization achieved with the 1D model is not ideal, in order to achieve better results on resource utilization researchers directed their work on the 2D area model. In the previous section, the superiority of the Stuffing Technique against the Horizon, in the 1D model, is shown. For that reason the scheduler we choose for further expansion to the 2D area model is the Stuffing Technique.

During the expansion of the Stuffing Technique to the 2D area model, several problems must be considered. First it was clear that the execution flow of the algorithm would remain the same as the 1D one. Also it was observed that the main functions, i.e. *schedule, BestFit* and *check\_conflict,* used for the 1D Stuffing Technique could be easily upgraded to support the 2D area model. Also the lists used for maintaining the data the scheduler needs, i.e. *execution, reservation* and *free space* lists, could also be used in the 2D area model with minor modifications. It is important to note that now the *free space list* entries, list a space rectangle like that [x<sub>1</sub>, y<sub>1</sub>, x<sub>3</sub>, y<sub>3</sub>]. However, the most important and difficult changes in the scheduler were relevant to the placement management.

When considering a two-dimensional plain, the problem of managing the space left becomes a problem of maintaining a list of free maximal rectangles in space and time. This problem can be compared to the 2D bin packing problem, which is known to be a combinatorial NP-hard problem. For this problem several solutions have been proposed, most of them consider different ways to partition the device, in order to create maximum rectangles.

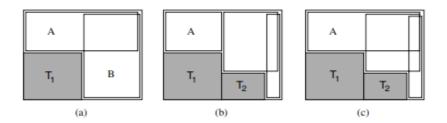

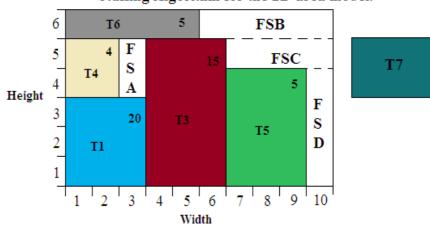

In [10] Steiger et al. do not present the placer or the way the 2D Stuffing Algorithm manages the free space, instead the placer used is presented in [16]. The placer considers no permanent partitioning of the device, but instead creates overlapping rectangles, in order to have at each point the maximal rectangles as seen in Figure 7.

During the implementation process of the algorithm, we made, excessive efforts to recreate Steiger's placer. However, due to the lack of information provided by Steiger in

[16], our tries were unsuccessful. Also because of our studies, regarding the technology restrictions in FPGA devices, we were already aware of the infeasibility of Steiger's design. More on that matter will be presented later. Nonetheless this failure prompted us to search for other solutions.

**Figure 3.7:** Here we see the place management technique presented by Steiger in [16]. We can observe that the splitting decision is delayed by the placer algorithm, thus creating two or more overlapping rectangles, representing the free space in the reconfigurable area.

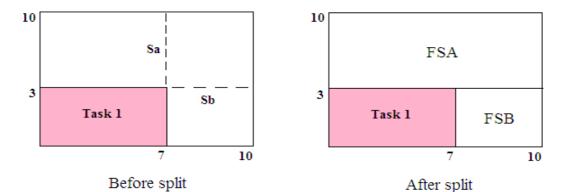

In [16] it is clear that the main influence of the placer presented is Bazargan's work in [15]. In his work Bazargan presents many heuristics that will ultimately help the placer perform the best split possible, the results of the experiments showed that the best heuristic was the Shorter Segment Heuristic (SSEG). In that heuristic after the insertion of a task, the split is performed, choosing the shorter of the two segments created. A simple example of Bazargan's SSEG is shown in Figure 8. So we decided the *UpdateSpace* function used for place management to be created according to Bazargan's SSEG Heuristic.

**Figure 3.8:** A representation of Bazargan's SSEG Heuristic. Before the splitting of the reconfigurable area the placer considers the length of the two segments *Sa* and *Sb* and splits the area along the shorter one, thus creating Free Space Area *A* and *B*.

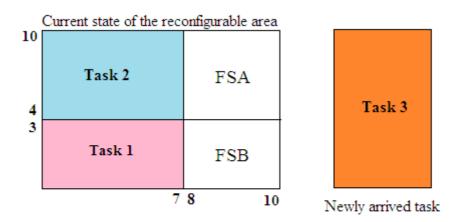

Despite the fact that a solution was found and the expansion in the 2D model could be made, this solution introduced a huge disadvantage. More specifically after many task insertions, it was observed that the reconfigurable area would be split in many small rectangles. That meant that although enough area would exist on the device to accommodate a newly arrived task, the partitioning of this area would not allow the acceptance of said task.

An example of that can be seen in Figure 9. In this example, we see that the reconfigurable area is split in two Free Space rectangles, ([8,1], [10,3]) and ([8, 4], [10, 10]). The FSA rectangle is 3 space units wide and 7 space units high while the FSB rectangle is 3 space units wide and 3 space units high. The newly arrived task however is 3 space units wide and 10 space units high. Due to the current partitioning of the free space area this task would be rejected. However if a merging would occur between the two rectangles, enough space would exist for the task to be placed on.

In order to overcome this disadvantage a new *mergeIntervals* function was created. In this function, when two adjacent rectangles are found, the algorithm merges them into one, while removing the merged intervals from the *free space list*. More specifically the function would merge adjacent rectangles that had at least one equal dimension. In the figure above the *mergeIntervals* function would merge the FSA and FSB rectangles, as they both have a width of 3 space units. into one Free Space rectangle, large enough to accommodate Task 3.

Another change needed for the expansion of the Stuffing Technique in the 2D area model was the creation of a new function called *removeExecUpdate*. After the completion of a task, that task would be removed from the device. After the removal, this function would

add a Free Space entry, to the *free space list* with dimensions equal to the removed task's ones. The new *free space list* would then be given as an input to the *mergeIntervals* function in order to better utilize the free space created from the task removal, applying the appropriate merges.

After implementing all the changes needed for the expansion of the Stuffing Technique to the 2D area model, a task set was created to test the correct functionality of our algorithm. The task set created was Steiger's task set, used in all the previous evaluations, however, in order to present the better space management done by the 2D area model, we decreased the device's dimensions from  $10 \times 10$  to 10 space units wide and 6 space units high. The final results produced by our program were the following:

> Task 7 was rejected! The number of declined tasks is: 1 The percentage of declined tasks is: 10.00

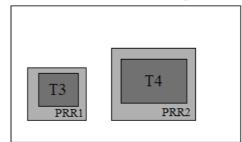

The results shown above are different, from the results Steiger showed in his work. Specifically this task set produced no rejected tasks when the 2D Stuffing Algorithm was applied in Steiger's. A graphical representation of the reconfigurable area before the arrival of task 7 is shown in Figure 10.

**Figure 3.10:** A graphical representation of the reconfigurable area before the arrival of task 7. Along with the entries of free space area listed in the *free space list*.

In the figure above it is clear that although there is enough space in the device for Task 7 to be accommodated on, the algorithm rejects this task. In order to understand why this happens the instance of the *free space list* before the arrival of Task 7 is presented.

#### \*\*\*\*\*FREE SPACE LIST\*\*\*\*\*

Free Space interval x1 3, y1 4, x2 3, y2 5. Free Space interval x1 6, y1 6, x2 10, y2 6. Free Space interval x1 7, y1 5, x2 10, y2 5. Free Space interval x1 10, y1 1, x2 10, y2 4.

Now it is clear, why our implementation of the algorithm produces a rejected task. The chosen way of merging the intervals in the *free space list* after each update and the choice of conducting the split after the insertion of a task, opposing to Steiger's overlapping rectangles technique, led to this device instance, where the intervals are managed and listed in a way that is not optimal and leads to space fragmentation and finally to the rejection of Task 7. However as stated before this choices were inevitable.

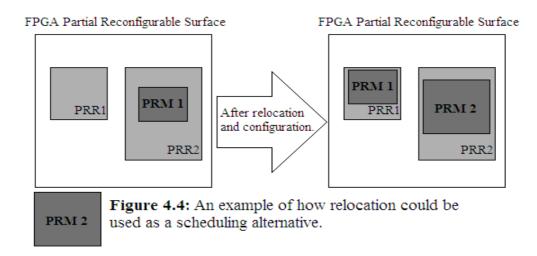

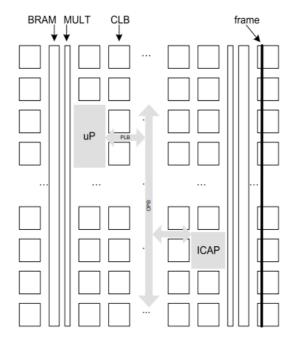

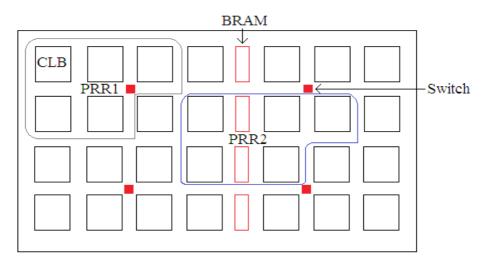

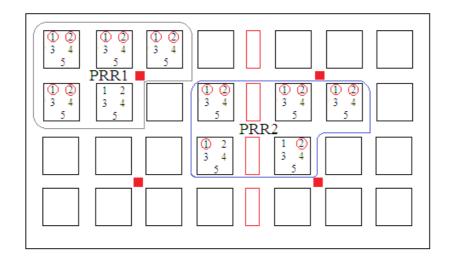

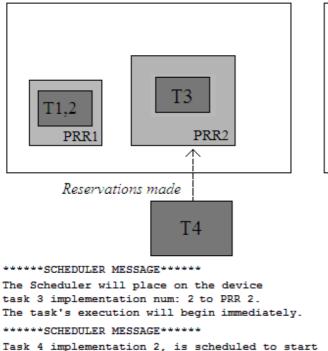

It is important to note that, despite the fact, the same task set used in the 1D model, in 2D model produces one rejected task, ultimately the 2D model surpasses the 1D model in terms of space utilization, as we can see that the device's dimensions are clearly smaller, in the 2D area model evaluation.