#### TECHNICAL UNIVERSITY OF CRETE DEPARTMENT OF ELECTRONIC AND COMPUTER ENGINEERING

Master Thesis

#### Programming high-performance applications on the Cell BE processor

## CHRISTOU PANAGIOTIS

#### Selection Committee

Ioannis Papaefstathiou, Assistant Professor of the Technical University of Crete (Supervisor) Apostolos Dollas, Professor of the Technical University of Crete Dionisios Pnevmatikatos, Associate Professor of the Technical University of Crete

## CHANIA 2010

# Contents

| 1        | Intr | roduction                                                   | 13              |

|----------|------|-------------------------------------------------------------|-----------------|

| <b>2</b> | Plat | tform                                                       | 15              |

|          | 2.1  | Cell Broadband Engine                                       | 15              |

|          |      | 2.1.1 Power Processor Element                               | 16              |

|          |      | 2.1.2 Synergistic Processor Element                         | 18              |

|          |      | 2.1.3 Element Interconnect Bus                              | 21              |

|          | 2.2  | Playstation3                                                | 22              |

|          |      | 2.2.1 Operating System                                      | 23              |

|          |      | 2.2.2 Memory System                                         | 23              |

|          |      | 2.2.3 Network Card                                          | 24              |

|          |      | 2.2.4 Graphics Card                                         | 24              |

| 3        | Glii | mmer Algorithm                                              | 25              |

| 0        | 3.1  | An Introductory Background On Biology                       | 25              |

|          | 3.2  | Gene Identification Problem                                 | $\frac{-0}{26}$ |

|          | 3.3  | Interpolated Markov Models and Markov Chains                | 26              |

|          |      | 3.3.1 Markov Chains                                         | 27              |

|          |      | 3.3.2 Interpolated Markov Models (IMMs)                     | $\frac{-}{28}$  |

|          |      | 3.3.3 Interpolated Context Models (ICMs)                    | 29              |

|          | 3.4  | Glimmer Algorithm                                           | $\frac{-0}{30}$ |

|          | 0.1  | 3.4.1 Algorithm Input                                       | 30              |

|          |      | 3.4.2 Algorithm Output                                      | 31              |

|          |      | 3.4.3 The Glimmer System                                    | 31              |

| 4        | Loi  | ng-Range Noise Propagation and Helicopter Path Optimization |                 |

|          |      | Noise Reduction                                             | 33              |

|          | 4.1  | Introduction and Background                                 | 33              |

|          | 4.2  | Problem Statement                                           | 35              |

|          | 4.3  | The PE-method in sound propagation                          | 36              |

|          | 4.4  | PDE Solution with Crank-Nicholson Algorithm                 | 36              |

|          |      | 9                                                           |                 |

|          | 4.5                                                                                              | Curvilinear Transformations of Coordinates                                                                                                                                                                                                                                                    | 37                                                                                                                                                                                                    |

|----------|--------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 4.6                                                                                              | CNPE Algorithm                                                                                                                                                                                                                                                                                | 38                                                                                                                                                                                                    |

|          |                                                                                                  | 4.6.1 Algorithm Input                                                                                                                                                                                                                                                                         | 38                                                                                                                                                                                                    |

|          |                                                                                                  | 4.6.2 Algorithm Output                                                                                                                                                                                                                                                                        | 38                                                                                                                                                                                                    |

|          |                                                                                                  | 4.6.3 Basic Steps Of The Application                                                                                                                                                                                                                                                          | 39                                                                                                                                                                                                    |

| <b>5</b> | Imp                                                                                              | plementation Of The Glimmer                                                                                                                                                                                                                                                                   | 43                                                                                                                                                                                                    |

|          | 5.1                                                                                              | The Programming Model                                                                                                                                                                                                                                                                         | 44                                                                                                                                                                                                    |

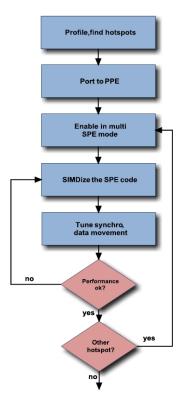

|          | 5.2                                                                                              | The Application Enablement Process                                                                                                                                                                                                                                                            | 44                                                                                                                                                                                                    |

|          | 5.3                                                                                              | Profiling                                                                                                                                                                                                                                                                                     | 45                                                                                                                                                                                                    |

|          | 5.4                                                                                              | The Hotspot of the Glimmer                                                                                                                                                                                                                                                                    | 47                                                                                                                                                                                                    |

|          | 5.5                                                                                              | Data Flow Analysis                                                                                                                                                                                                                                                                            | 48                                                                                                                                                                                                    |

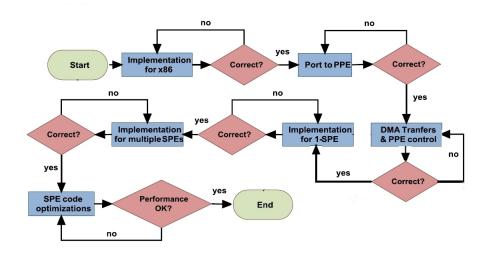

|          | 5.6                                                                                              | Development Stages                                                                                                                                                                                                                                                                            | 51                                                                                                                                                                                                    |

|          |                                                                                                  | 5.6.1 Implementation on x86 Architecture                                                                                                                                                                                                                                                      | 52                                                                                                                                                                                                    |

|          |                                                                                                  | 5.6.2 Port to PPE                                                                                                                                                                                                                                                                             | 53                                                                                                                                                                                                    |

|          |                                                                                                  | 5.6.3 PPE control                                                                                                                                                                                                                                                                             | 53                                                                                                                                                                                                    |

|          |                                                                                                  | 5.6.4 DMA Transfer                                                                                                                                                                                                                                                                            | 60                                                                                                                                                                                                    |

|          |                                                                                                  | 5.6.5 Implementation with One and Multiple SPEs                                                                                                                                                                                                                                               | 62                                                                                                                                                                                                    |

|          |                                                                                                  | 5.6.6 Code Optimizations                                                                                                                                                                                                                                                                      | 63                                                                                                                                                                                                    |

|          | 5.7                                                                                              | Software Tools problems                                                                                                                                                                                                                                                                       | 64                                                                                                                                                                                                    |

|          |                                                                                                  |                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                       |

| 6        | Imp                                                                                              | plementation Of the CNPE algorithm                                                                                                                                                                                                                                                            | 65                                                                                                                                                                                                    |

| 6        | <b>Imp</b><br>6.1                                                                                | -                                                                                                                                                                                                                                                                                             | <b>65</b><br>65                                                                                                                                                                                       |

| 6        | -                                                                                                | Dementation Of the CNPE algorithm         The Programming Model         The Application Enablement Process                                                                                                                                                                                    |                                                                                                                                                                                                       |

| 6        | 6.1                                                                                              | The Programming Model                                                                                                                                                                                                                                                                         | 65                                                                                                                                                                                                    |

| 6        | $6.1 \\ 6.2$                                                                                     | The Programming Model                                                                                                                                                                                                                                                                         | $\begin{array}{c} 65\\ 65\end{array}$                                                                                                                                                                 |

| 6        | 6.1<br>6.2<br>6.3                                                                                | The Programming Model                                                                                                                                                                                                                                                                         | $65 \\ 65 \\ 65$                                                                                                                                                                                      |

| 6        | 6.1<br>6.2<br>6.3<br>6.4                                                                         | The Programming Model                                                                                                                                                                                                                                                                         | 65<br>65<br>65<br>66                                                                                                                                                                                  |

| 6        | $ \begin{array}{c} 6.1 \\ 6.2 \\ 6.3 \\ 6.4 \\ 6.5 \end{array} $                                 | The Programming Model                                                                                                                                                                                                                                                                         | 65<br>65<br>66<br>70                                                                                                                                                                                  |

| 6        | $ \begin{array}{c} 6.1 \\ 6.2 \\ 6.3 \\ 6.4 \\ 6.5 \end{array} $                                 | The Programming Model                                                                                                                                                                                                                                                                         | 65<br>65<br>66<br>70<br>70                                                                                                                                                                            |

| 6        | $ \begin{array}{c} 6.1 \\ 6.2 \\ 6.3 \\ 6.4 \\ 6.5 \end{array} $                                 | The Programming ModelThe Application Enablement ProcessProfilingOutputThe Hotspot of the CNPEDataflow AnalysisDevelopment Stages6.6.1Implementation on x86Architecture                                                                                                                        | 65<br>65<br>66<br>70<br>70<br>72                                                                                                                                                                      |

| 6        | $ \begin{array}{c} 6.1 \\ 6.2 \\ 6.3 \\ 6.4 \\ 6.5 \end{array} $                                 | The Programming ModelThe Application Enablement ProcessProfilingProfilingThe Hotspot of the CNPEDataflow AnalysisDevelopment Stages6.6.1Implementation on x86 Architecture6.6.2Port to PPE                                                                                                    | 65<br>65<br>66<br>70<br>70<br>72<br>72                                                                                                                                                                |

| 6        | $ \begin{array}{c} 6.1 \\ 6.2 \\ 6.3 \\ 6.4 \\ 6.5 \end{array} $                                 | The Programming ModelThe Application Enablement ProcessProfilingOutputThe Hotspot of the CNPEDataflow AnalysisDevelopment StagesControl6.6.1Implementation on x86 Architecture6.6.2Port to PPEControlControl                                                                                  | $65 \\ 65 \\ 65 \\ 66 \\ 70 \\ 70 \\ 72 \\ 72 \\ 72 \\ 72$                                                                                                                                            |

| 6        | $ \begin{array}{c} 6.1 \\ 6.2 \\ 6.3 \\ 6.4 \\ 6.5 \end{array} $                                 | The Programming ModelThe Application Enablement ProcessProfilingThe Hotspot of the CNPEDataflow AnalysisDevelopment Stages6.6.1 Implementation on x86 Architecture6.6.2 Port to PPE6.6.3 PPE control6.6.4 DMA Transfer                                                                        | $65 \\ 65 \\ 65 \\ 66 \\ 70 \\ 70 \\ 72 \\ 72 \\ 72 \\ 72 \\ 74$                                                                                                                                      |

| 6        | 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6                                                           | The Programming ModelThe Application Enablement ProcessProfilingThe Hotspot of the CNPEDataflow AnalysisDevelopment Stages6.6.1Implementation on x86 Architecture6.6.2Port to PPE6.6.3PPE control6.6.4DMA Transfer6.6.5Implementation with One and Multiple SPEs                              | $\begin{array}{c} 65\\ 65\\ 65\\ 66\\ 70\\ 70\\ 72\\ 72\\ 72\\ 74\\ 74\\ 75\\ \end{array}$                                                                                                            |

|          | 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6                                                           | The Programming ModelThe Application Enablement ProcessProfilingThe Hotspot of the CNPEDataflow AnalysisDevelopment Stages6.6.1Implementation on x86 Architecture6.6.2Port to PPE6.6.3PPE control6.6.4DMA Transfer6.6.5Implementation with One and Multiple SPEs6.6.6Code Optimizations       | $65 \\ 65 \\ 65 \\ 66 \\ 70 \\ 70 \\ 72 \\ 72 \\ 72 \\ 74 \\ 74$                                                                                                                                      |

|          | <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>6.6</li> </ul> Eva     | The Programming Model                                                                                                                                                                                                                                                                         | <ul> <li>65</li> <li>65</li> <li>65</li> <li>66</li> <li>70</li> <li>70</li> <li>72</li> <li>72</li> <li>72</li> <li>72</li> <li>72</li> <li>74</li> <li>74</li> <li>75</li> <li><b>79</b></li> </ul> |

|          | <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>6.6</li> </ul> Eva 7.1 | The Programming ModelThe Application Enablement ProcessProfilingThe Hotspot of the CNPEDataflow AnalysisDevelopment Stages6.6.1 Implementation on x86 Architecture6.6.2 Port to PPE6.6.3 PPE control6.6.4 DMA Transfer6.6.5 Implementation with One and Multiple SPEs6.6.6 Code Optimizations | 65<br>65<br>66<br>70<br>72<br>72<br>72<br>72<br>72<br>74<br>74<br>75<br><b>79</b><br>79                                                                                                               |

|          | <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>6.6</li> </ul> Eva 7.1 | The Programming Model                                                                                                                                                                                                                                                                         | 65<br>65<br>66<br>70<br>72<br>72<br>72<br>72<br>74<br>74<br>75<br><b>79</b><br>79<br>80                                                                                                               |

#### CONTENTS

| 8 | Eva | luation and Verification Of the CNPE | 85  |

|---|-----|--------------------------------------|-----|

|   | 8.1 | Measuring Performance                | 85  |

|   | 8.2 | Performance                          | 85  |

|   |     | 8.2.1 Performance of SPEs            | 85  |

|   |     | 8.2.2 Final Comparison               | 91  |

|   | 8.3 | Verification                         | 102 |

| 9 | Con | clusions and Future Work             | 105 |

|   | 9.1 | Conclusions                          | 105 |

|   | 9.2 | Future Work                          | 105 |

CONTENTS

# List of Figures

| 2.1  | Cell Broadband Engine Architecture                                  | 16 |

|------|---------------------------------------------------------------------|----|

| 2.2  | PPE Block Diagram                                                   | 17 |

| 2.3  | SPE Block Diagram                                                   | 18 |

| 2.4  | Synergistic Processor Element architecture                          | 19 |

| 2.5  | Latencies and pipe assignment for SPE                               | 20 |

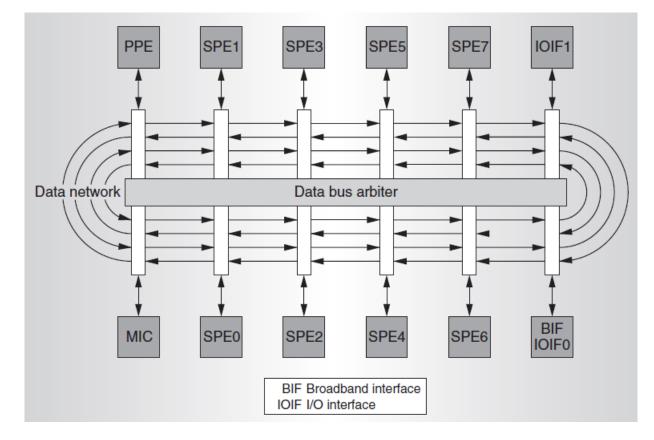

| 2.6  | Element interconnect bus (EIB)                                      | 22 |

| 3.1  | Sample ICM decomposition tree                                       | 30 |

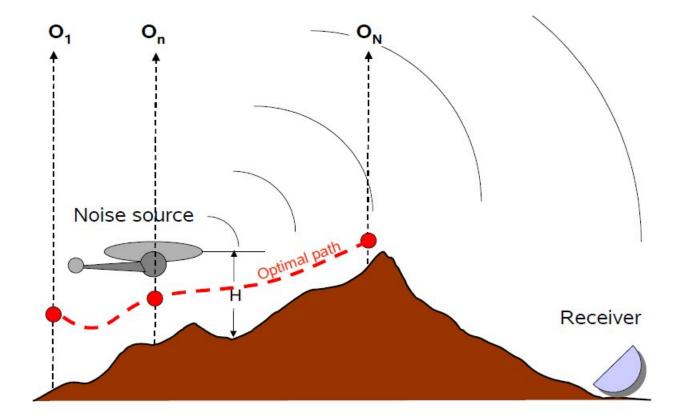

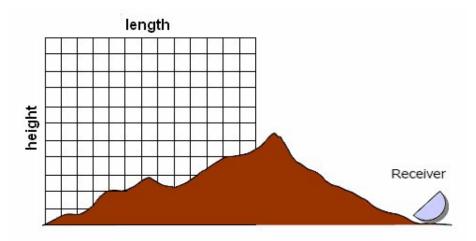

| 4.1  | Schematic of long-range noise propagation of a helicopter flying at |    |

|      | height H                                                            | 35 |

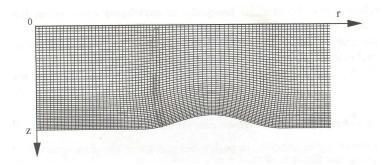

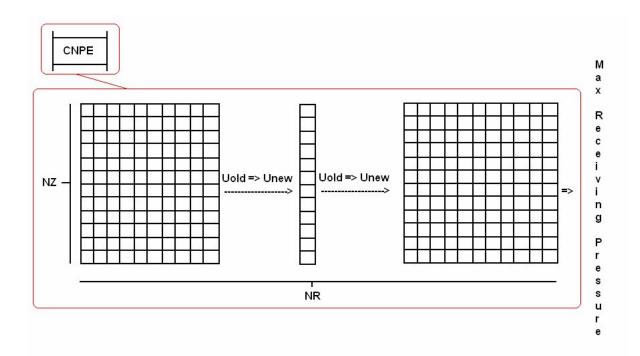

| 4.2  | Orthogonal mesh over an irregular bottom                            | 38 |

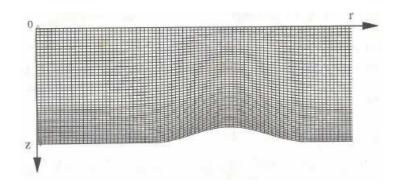

| 4.3  | Non-Orthogonal mesh over an irregular bottom                        | 38 |

| 4.4  | Schematic of the seperated territorial region                       | 39 |

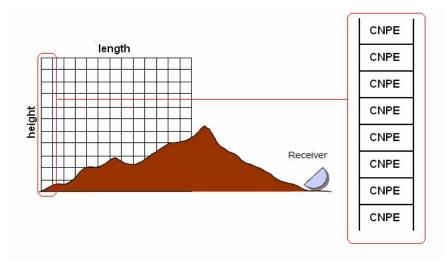

| 4.5  | The CNPE is applied for each height                                 | 39 |

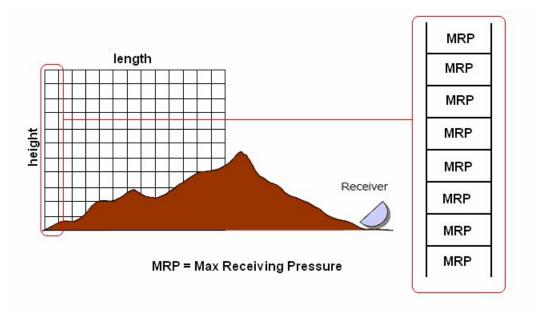

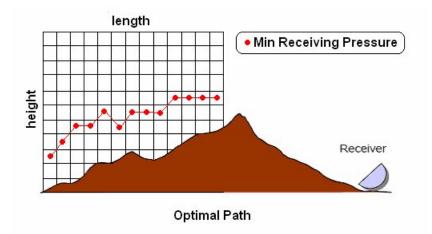

| 4.6  | The calculation of the Max Receiving Pressure of the receiver       | 40 |

| 4.7  | The Max Receiving Pressure of the receiver for each height          | 41 |

| 4.8  | The optimal flight path                                             | 41 |

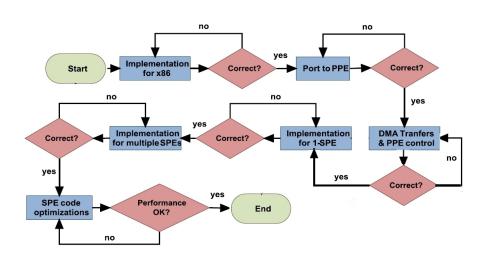

| 5.1  | Application enablement process.                                     | 45 |

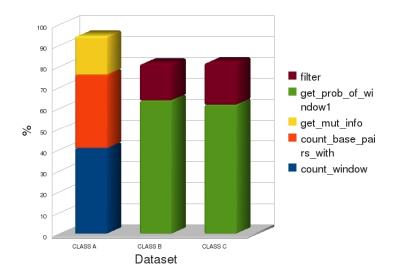

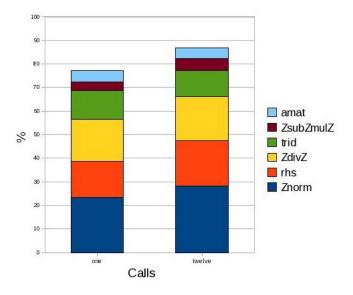

| 5.2  | Function-Wise Breakout for various datasets                         | 48 |

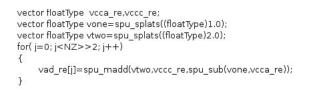

| 5.3  | The code of the function get_prob_of_window1                        | 49 |

| 5.4  | The code where the function $get_prob_of_window1$ is called         | 51 |

| 5.5  | The development flow chart                                          | 51 |

| 5.6  | An interative development process                                   | 52 |

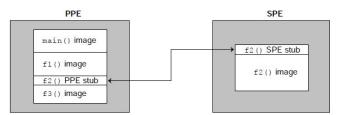

| 5.7  | Function-Offload (or RPC) Model with stubs.                         | 54 |

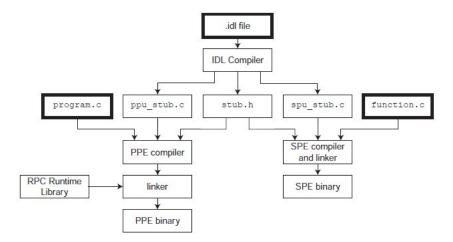

| 5.8  | Production Flow for Function Offload (or RPC) Model                 | 55 |

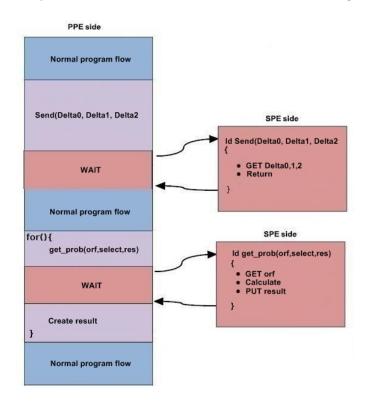

| 5.9  | Overall scheduling process for 1st implementation of GLIMMER.       | 56 |

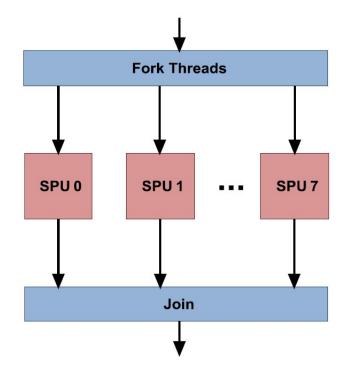

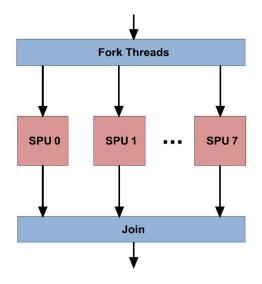

| 5.10 | Fork-join model                                                     | 57 |

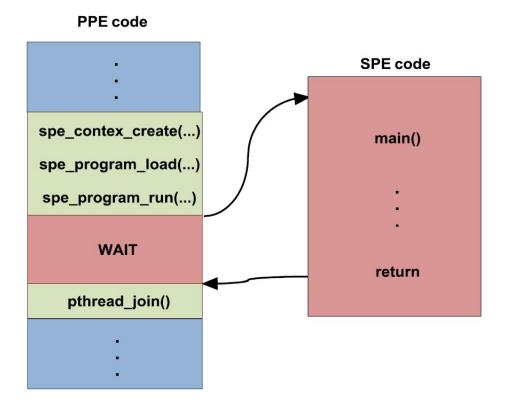

| 5.11 | PPE control.                                                        | 58 |

| 5.12 | Overall scheduling process for GLIMMER.                             | 59 |

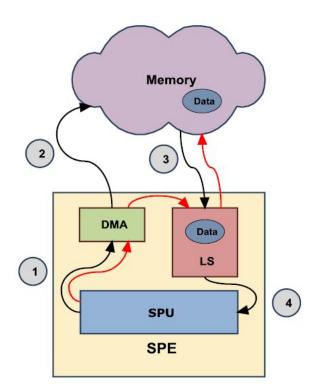

| 5.13                                                                                                               | Data Transfer from and to LS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

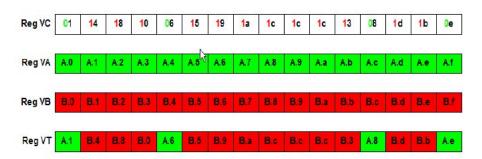

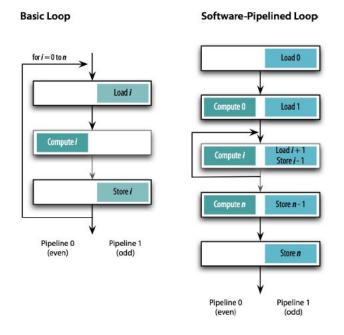

| $\begin{array}{c} 6.1 \\ 6.2 \\ 6.3 \\ 6.4 \\ 6.5 \\ 6.6 \\ 6.7 \\ 6.8 \\ 6.9 \\ 6.10 \\ 6.11 \\ 6.12 \end{array}$ | Data Transfer from and to LS.6Function-Wise Breakout for CNPE.6The code of the function CNPE.6The code of the function Amat.6The code of the function Rhs.6The code of the function Trid.6The development flow chart.7An interative development process.7Fork-join model.7Overall scheduling process for CNPE.7A part of the amat code.7A part of the amat's vector code.7Shuffle example: spu_shuffle VT,VA,VB,VC instruction.7                                                                                        |

|                                                                                                                    | Pipelining and dual-issue                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

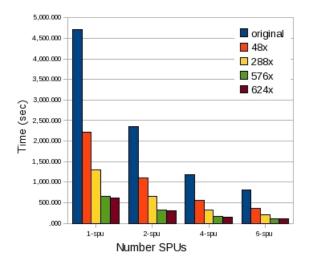

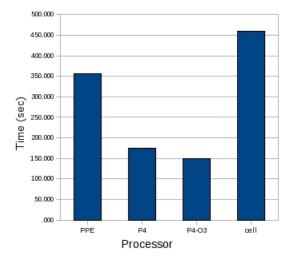

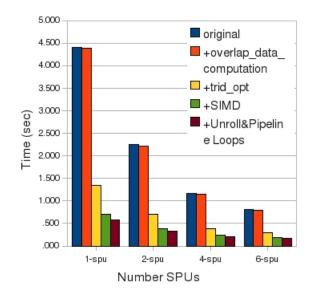

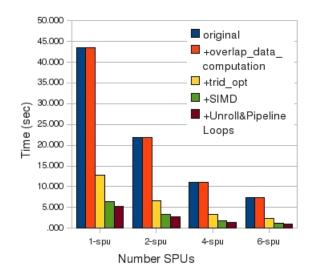

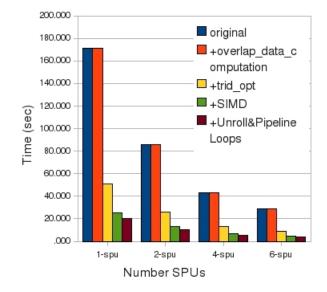

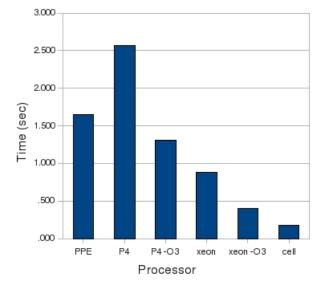

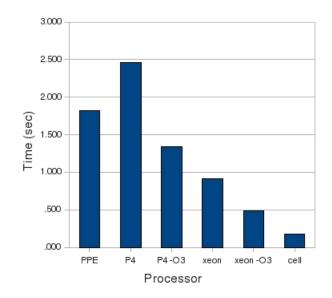

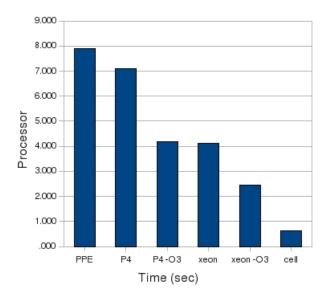

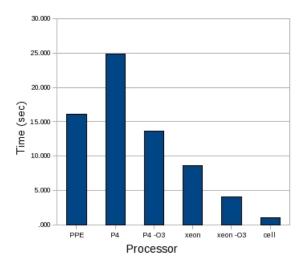

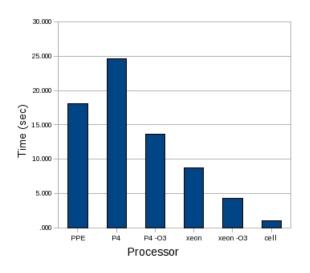

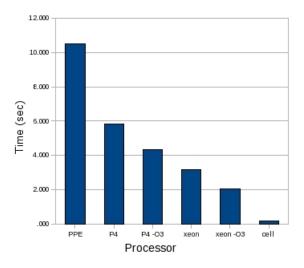

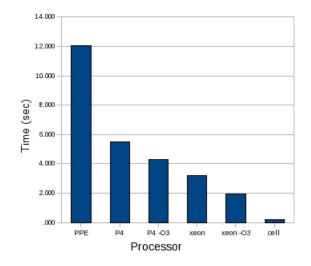

| 7.1<br>7.2<br>7.3<br>7.4<br>7.5                                                                                    | Performance impact of various optimizations for NC003062.fna.8Performance impact of various optimizations for NC004463.fna.8SPE statistics for the Glimmer.8Performance comparisons of the Glimmer for dataset NC003062.fna.8Performance comparisons of the Glimmer for dataset NC004463.fna.8                                                                                                                                                                                                                          |

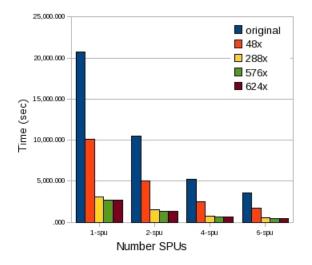

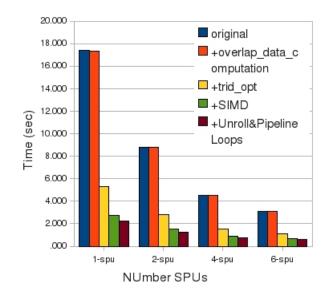

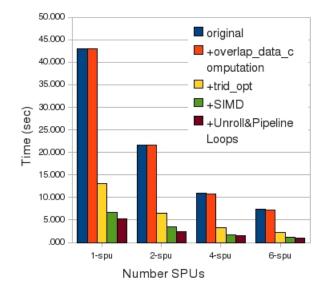

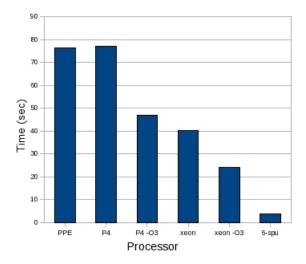

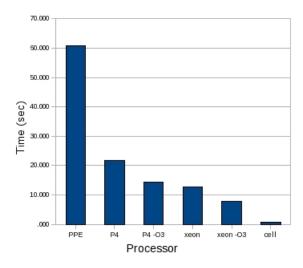

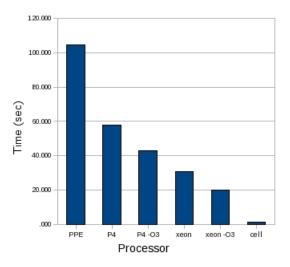

| 8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6<br>8.7                                                                      | Performance impact of various optimizations.8Performance impact of various optimizations.8Performance impact of various optimizations.8Performance impact of various optimizations.8Performance impact of various optimizations.9Performance impact of various optimizations.9Performance impact of various optimizations.9Performance impact of various optimizations.9Performance comparisons for 36 CNPE with NZ=128, NR=1005 and same trid.9Performance comparisons for 26 CNPE with NZ 256 NP. 500 and same trid.9 |

| 8.8                                                                                                                | Performance comparisons for 36 CNPE with NZ=256, NR=500 and same trid.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 8.9                                                                                                                | Performance comparisons for 36 CNPE with NZ=512, NR=1005 and same trid                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 8.10                                                                                                               | Performance comparisons for 360 CNPE with NZ=128, NR=1005<br>and same trid                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                    | Performance comparisons for 360 CNPE with NZ=256, NR=500 and same trid                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 8.12                                                                                                               | Performance comparisons for 360 CNPE with NZ=512, NR=1005<br>and same trid                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 8.13 | Performance comparisons for 36 CNPE with NZ=128, NR=1005 and      |     |

|------|-------------------------------------------------------------------|-----|

|      | different trid.                                                   | 97  |

| 8.14 | Performance comparisons for 36 CNPE with NZ=256, NR=500 and       |     |

|      | different trid.                                                   | 98  |

| 8.15 | Performance comparisons for 36 CNPE with NZ=512, NR=1005 and      |     |

|      | different trid.                                                   | 99  |

| 8.16 | Performance comparisons for 360 CNPE with NZ=128, NR=1005         |     |

|      | and different trid                                                | 100 |

| 8.17 | Performance comparisons for 360 CNPE with NZ=256, NR=500 and      |     |

|      | different trid                                                    | 100 |

| 8.18 | Performance comparisons for 360 CNPE with NZ=512, NR=1005         |     |

|      | and different trid                                                | 101 |

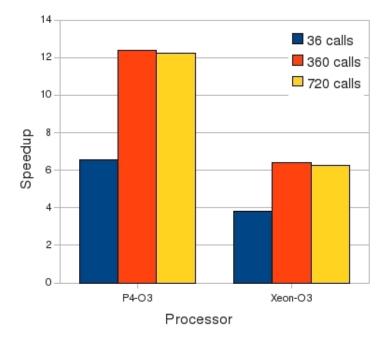

| 8.19 | Speedup over P4-O3 and xeon-O3 for NZ=512 and NR=1005 with $\sim$ |     |

|      | same trid                                                         | 102 |

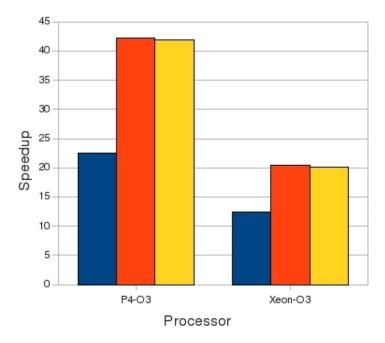

| 8.20 | Speedup over P4-O3 and xeon-O3 for NZ=512 and NR=1005 with $\sim$ |     |

|      | different trid                                                    | 103 |

# List of Tables

| 5.1  | Results of the profiling GLIMMER for Dataset CLASS A NC004061.fna         | 46  |

|------|---------------------------------------------------------------------------|-----|

| 5.2  | Function-wise breakout of Build-icm program                               | 46  |

| 5.3  | Results of the profiling GLIMMER for Dataset CLASS B NC003062.fna $$      | 46  |

| 5.4  | Function-wise breakout of Glimmer2 program                                | 47  |

| 5.5  | Results of the profiling GLIMMER for Dataset CLASS C NC004463.fna $$      | 47  |

| 5.6  | Function-wise breakout of Glimmer2 program                                | 47  |

| 5.7  | Total calls of the function get_prob_of_window1                           | 48  |

| 5.8  | The amount of data is needed by procedure for various datasets            | 50  |

| 5.9  | The new amount of data is needed by procedure for various datasets.       | 50  |

| 5.10 | The size of data is needed to store to Local Store                        | 50  |

| 5.11 | DMA Transfers                                                             | 62  |

| 6.1  | Results of the profiling CNPE for one call of the $CNPE$ function         | 66  |

| 6.2  | Function-wise breakout of CNPE program                                    | 66  |

| 6.3  | Results of the profiling CNPE for twelve call of the <i>CNPE</i> function | 66  |

| 6.4  | Function-wise breakout of CNPE program                                    | 67  |

| 6.5  | The amount of Local Store space needed.                                   | 70  |

| 6.6  | DMA Transfers.                                                            | 74  |

| 0.0  |                                                                           | • • |

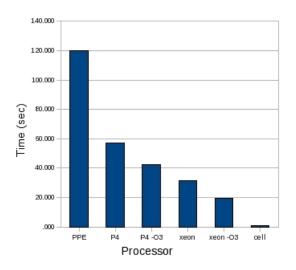

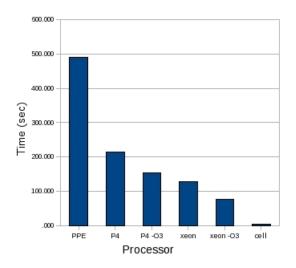

| 7.1  | Execution time of Glimmer for NC003062.fna                                | 80  |

| 7.2  | Execution time of Glimmer for NC004463.fna                                | 81  |

| 8.1  | Execution time of 36 CNPE for NZ=128 and NR=1005.                         | 86  |

| 8.2  | Execution time of 36 CNPE for NZ=256 and NR=500                           | 87  |

| 8.3  | Execution time of 36 CNPE for NZ=512 and NR=1005.                         | 87  |

| 8.4  | Execution time of 360 CNPE for NZ=128 and NR=1005                         | 88  |

| 8.5  | Execution time of 360 CNPE for NZ=256 and NR=500.                         | 89  |

| 8.6  | Execution time of 360 CNPE for NZ=512 and NR=1005                         | 90  |

| 8.7  | Execution time of 36 CNPE for NZ=128, NR=1005 and same trid.              | 92  |

| 8.8  | Execution time of 36 CNPE for NZ=256, NR=500 and same trid. $\therefore$  | 93  |

| 8.9  | Execution time of 36 CNPE for NZ= $512$ , NR= $1005$ and same trid.       | 93  |

| 0.0  |                                                                           | 00  |

8.10 Execution time of 360 CNPE for NZ=128, NR=1005 and same trid.

94

8.11 Execution time of 360 CNPE for NZ=256, NR=500 and same trid.

95

8.12 Execution time of 360 CNPE for NZ=512, NR=1005 and same trid.

96

8.13 Execution time of 36 CNPE for NZ=128, NR=1005 and different trid.

97

8.14 Execution time of 36 CNPE for NZ=256, NR=500 and different trid.

98

8.15 Execution time of 36 CNPE for NZ=512, NR=1005 and different trid.

98

8.16 Execution time of 360 CNPE for NZ=128, NR=1005 and different trid.

99

8.17 Execution time of 360 CNPE for NZ=256, NR=500 and different trid.

91

8.18 Execution time of 360 CNPE for NZ=256, NR=500 and different trid.

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

81

82

81

81

82

81

81

82

81

81

82

81

82

81

81

81

81

<l

# Chapter 1 Introduction

Over the past decade, high-performance computing has ridden the wave of commodity computing, building clusterbased parallel computers that leverage the tremendous growth in processor performance fueled by the commercial world. As this pace slows, processor designers face complex problems in their efforts to increase gate density, reduce power consumption, and design efficient memory hierarchies. Processor developers are looking for solutions that can keep up with the scientific and industrial communities' insatiable demand for computing capability and that also have a sustainable market outside science and industry.

A major trend in computer architecture is integrating system components onto the processor chip. This trend is driving the development of processors that can perform functions typically associated with entire systems. Building modular processors with multiple cores is far more cost-effective than building monolithic processors, which are prohibitively expensive to develop, have high power consumption, and give limited return on investment. Multicore system-on-chip (SoC) processors integrate several identical, independent processing units on the same die, together with network interfaces, acceleration units, and other specialized units.

Researchers have explored several design avenues in both academia and industry. Examples include MIT's Raw multiprocessor, the University of Texas's Trips multiprocessor, AMD's Opteron, IBM's Power5, Sun's Niagara, and Intel's Montecito, among many others.

In all multicore processors, a major technological challenge is designing the internal, on-chip communication network. To realize the unprecedented computational power of the many available processing units, the network must provide very high performance in latency and in bandwidth. It must also resolve contention under heavy loads, provide fairness, and hide the processing units' physical distribution as completely as possible.

As the era of pure CMOS frequency scaling ends, architects must again respond to massive technological changes by more efficiently exploiting density scaling. The Cell Broadband Engine (Cell BE) answers these challenges by providing the first implementation of a chip multiprocessor with a significant number of general-purpose programmable cores targeting a broad set of workloads, including intensive multimedia and scientific processing.

Jointly developed beginning in 2000 by IBM, Sony, and Toshiba (STI) for the PlayStation 3 as well as other data-processing-intensive environments, Cell's design goal was to improve performance an order of magnitude over that of desktop systems shipping in 2005 [et 05], [M. 06a], [M. 06b]. To meet that goal, designers had to optimize performance against area, power, volume, and cost in a manner not possible with legacy architectures. Thus, the design strategy was to exploit application parallelism through numerous cores that support established application models, thereby ensuring good programmability as well as programmer efficiency[A. 05].

The resulting Cell design is a heterogeneous, multicore chip capable of massive floating-point processing optimized for computation-intensive workloads and rich broadband media applications.

The rest of this thesis is organized as follows: **Chapter 2** introduces the Cell Broadband Engine processor and the Playstation 3 that was used in the implementation. **Chapter 3** outlines the gene identification problem, the Markov Chains and Interpolated Markov Models and the Glimmer algorithm. **Chapter 4** presents the Long-Range Noise Propagation and Helicopter Path Opti- mization for Noise Reduction algorithm. **Chapter 5 and Chapter 6** describe the development process that was followed for the implementations of the Glimmer and CNPE applications respectively. **Chapter 7 and Chapter 8** present the final results for the implementations of the Glimmer and CNPE application respectively. **Chapter 9** presents some conclusions from this work and proposes some ideas for future work.

# Chapter 2

# Platform

This chapter describes the platform that was used for the implementation. The Cell processor, its architecture as well as and the Playstation 3 game console are described in this chapter. The purpose of the chapter is to introduce the reader to the architecture of Cell and to the hardware that was used in the implementation.

## 2.1 Cell Broadband Engine

The Cell processor is the first implementation of the Cell Broadband Engine Architetcture (CBEA), which is a fully compatible extension of the 64-bit PowerPC Architecture. Its initial target is the PlayStation 3 game console, but its capabilities also make it well suited for other applications such as visualization, image and signal processing, and various scientific and technical workloads.

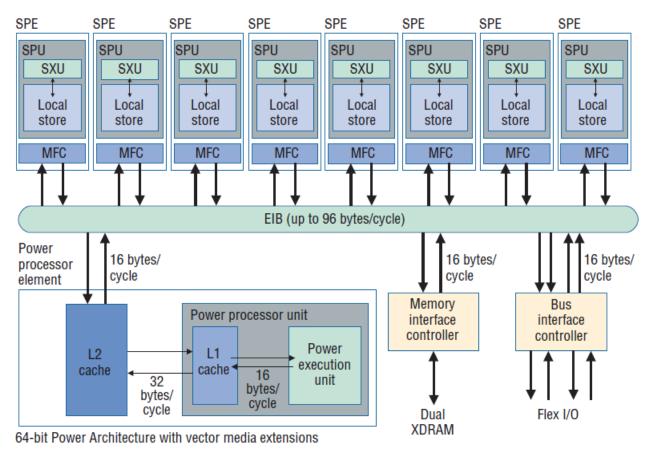

Figure 2.1 shows the Cell Broadband Engine, the first implementation of the CBEA. The processor is a heterogeneous, multicore chip capable of massive floatingpoint processing optimized for computation- intensive workloads and rich broadband media applications. It consists of one 64-bit power processor element (PPE), eight specialized coprocessors called synergistic processor elements (SPEs), a high-speed memory controller, and a high-bandwidth bus interface, all integrated on-chip. The PPE and SPEs communicate through an internal highspeed element interconnect bus (EIB).

With a clock speed of 3.2 GHz, the Cell processor has a theoretical peak performance of 204.8 Gflop/s (single precision) and 14.6 Gflop/s (double precision). The element interconnect bus supports a peak bandwidth of 204.8 Gbytes/s for intrachip data transfers, the memory interface controller provides a peak bandwidth of 25.6 Gbytes/s to main memory, and the I/O controller provides peak bandwidth of 25 Gbytes/s inbound and 35 Gbytes/s outbound[et 05].

#### 2.1.1 Power Processor Element

The Power processor element (PPE)[et 05],[IBM08b], [Sca09] consists of a 64- bit, multithreaded Power Architecture processor with two concurrent hardware threads. The PPE supports the Power Architecture vector multimedia extensions to accelerate multimedia applications using SIMD execution units.

Figure 2.1: Cell Broadband Engine Architecture

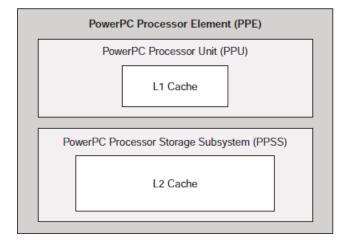

The PPE consists of two main units, the Power Processor Unit (PPU) and the Power Processor Storage Subsystem (PPSS), as shown in Figure 2.2. The PPE is responsible for overall control of the system. It runs the operating systems for all applications running on the Cell Broadband Engine. The PPU deals with instruction control and execution. It includes the full set of 64-bit PowerPC registers, 32 128-bit vector registers, a 32-KB level 1 (L1) instruction cache, a 32-KB level 1 (L1) data cache, an instruction-control unit, a load and store unit, a fixed-point integer unit, a floating point unit, a vector unit, a branch unit, and a virtual-memory management unit.

Figure 2.2: PPE Block Diagram

The PPU supports two simultaneous threads of execution and can be viewed as a 2-way multiprocessor with shared dataflow. This appears to software as two independent processing units. The state for each thread is duplicated, including all architected and special-purpose registers except those that deal with system-level resources, such as logical partitions, memory, and thread-control. Most nonarchitected resources, such as caches and queues, are shared by both threads, except in cases where the resource is small or offers a critical performance improvement to multithreaded applications.

The PPSS handles memory requests from the PPE and external requests to the PPE from other processors or I/O devices. It includes a unified 512-KB level 2 (L2) instruction and data cache, various queues, and a bus interface unit that handles bus arbitration and pacing on the EIB. Memory is seen as a linear array of bytes indexed from 0 to 264 - 1. Each byte is identified by its index, called an address, and each byte contains a value. One storage access occurs at a time, and all accesses appear to occur in program order.

The L2 cache and the address-translation caches use replacement-management tables that allow software to control use of the caches. This software control over cache resources is especially useful for real-time programming.

Although clocked at 3.2 GHz PPE looks like a quite potent processor, its main purpose is to serve as a controller and supervise the other cores on the chip. In a Cell based system the PPE will run the operating system (OS) and most of the applications but compute intensive parts of the OS and applications will be offloaded to the SPEs. Thanks to the PPE's compliance with the PowerPC architecture, existing applications can run on the Cell out of the box, and be gradually optimized for performance using the SPEs ,rather than written from scratch[et 05].

#### 2.1.2 Synergistic Processor Element

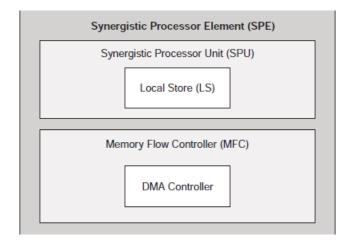

Each of the eight Synergistic Processor Elements (SPEs)[et 05],[MS07],[IBM08b], [Sca09] is a 128-bit RISC processor specialized for data-rich, compute-intensive SIMD applications. It consists of two main units, the Synergistic Processor Unit (SPU) and the Memory Flow Controller (MFC), as shown in Figure 2.3.

Figure 2.3: SPE Block Diagram

The SPU deals with instruction control and execution. It includes a single register file with 128 registers (each one 128 bits wide), a unified (instructions and data) 256-KB local store (LS), an instruction-control unit, a load and store unit, two fixed-point units, a floating-point unit, and a channel-and-DMA interface. The SPU implements a new SIMD instruction set, the SPU Instruction Set Architecture, that is specific to the Broadband Processor Architecture.

Each SPU is an independent processor with its own program counter and is optimized to run SPE threads spawned by the PPE. The SPU fetches instructions from its own LS, and it loads and stores data from and to its own LS. With respect to accesses by its SPU, the LS is unprotected and untranslated storage.

Most instructions operate in a SIMD fashion on 128 bits of data representing either two 64-bit doubleprecision floating-point numbers or longer integers, four 32-bit single-precision floating-point numbers or integers, eight 16-bit subwords, or sixteen 8-bit characters. The 128-bit operands are stored in a 128- entry unified register file. Instructions may take up to three operands and produce one result. The register file has a total of six read and two write ports.

The memory instructions also access 128 bits of data, with the additional constraint that the accessed data must reside at addresses that are multiples of 16 bytes. Thus, when addressing memory with vector load or store instructions, the lower four bits of the byte addresses are simply ignored. To facilitate the loading

#### 2.1. CELL BROADBAND ENGINE

and storing of individual values, such as a character or an integer, there is additional support to extract or merge an individual value from or into a 128-bit register.

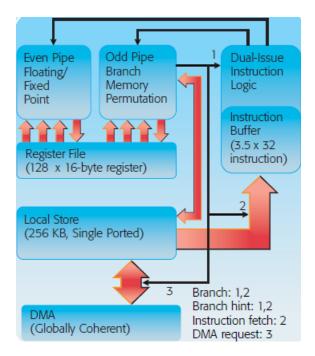

An SPE can dispatch up to two instructions per cycle to seven execution units that are organized into even and odd instruction pipes, as shown in Figure 2.4. Instructions are issued in order and routed to their corresponding even or odd pipe by the issue logic, that is, a component which examines the instructions and determines how they are to be executed, based on a number of constraints. Independent instructions are detected by the issue logic and are dual-issued (i.e., dispatched two per cycle) provided they satisfy the following condition: the first instruction must come from an even word address and use the even pipe, and the second instruction must come from an odd word address and use the odd pipe. When this condition is not satisfied, the two instructions are executed sequentially. The instruction latencies and their pipe assignments are shown in Figure 2.5.

Figure 2.4: Synergistic Processor Element architecture

The SPE's 256-KB local memory supports fully pipelined 16-byte accesses (for memory instructions) and 128-byte accesses (for instruction fetches and DMA transfers). Because the memory has a single port, instruction fetches, DMA, and memory instructions compete for the same port. Instruction fetches occur during idle memory cycles, and up to 3.5 fetches may be buffered in the instruction fetch buffer to better tolerate bursty peak memory usage. The maximum capacity of the buffer is thus 112 32- bit instructions. An explicit instruction can be used to initiate an

inline instruction fetch.

| Instruction                          | Pipe | Latency<br>(cycles) |

|--------------------------------------|------|---------------------|

| arithmetic, logical, compare, select | even | 2                   |

| byte sum/diff/average                | even | 4                   |

| shift/rotate                         | even | 4                   |

| float                                | even | 6                   |

| integer multiply-accumulate          | even | 7                   |

| shift/rotate, shuffle, estimate      | odd  | 4                   |

| load, store                          | odd  | 6                   |

| channel                              | odd  | 6                   |

| branch                               | odd  | 1-18                |

Figure 2.5: Latencies and pipe assignment for SPE

The SPE hardware assumes that branches are not taken, but the architecture allows for a "branch hint" instruction to override the default branch prediction policy. In addition, the branch hint instruction causes a prefetch of up to 32 instructions, starting from the branch target, so that a branch taken according to the correct branch hint incurs no penalty. One of the instruction fetch buffers is reserved for the branch-hint mechanism. In addition, there is extended support for eliminating short branches by using select instructions.

To access global data shared between threads executing on the PPE and other SPEs, each SPE includes an MFC, which performs data transfers between SPUlocal storage and system memory. The MFC provides the SPEs with access to system memory by supporting high-performance direct memory access (DMA) data transfer between the system memory and the local store. Data transfers can range in size from a single byte to 16-Kbyte blocks.

The MFC transfers copy between local store and system memory. An MFC transfer request specifies the local store location as the physical address in the local store. It specifies the system memory address as a Power Architecture virtual address, which the MFC's memory management logic translates to a physical address based on system-wide page tables that the Power Architecture specification provides.

Using the same virtual addresses to specify system memory locations independent of processor element type enables seamless data sharing between threads executing on both the PPE and SPE. An application executing on Cell can pass a PPE-generated pointer to code executing on the SPE and use it to specify the source or target in an MFC transfer request. Using full memory translation also ensures data protection between processes, as a thread can only access the system memory

#### 2.1. CELL BROADBAND ENGINE

mapped into the associated process's virtual memory space.

Finally, using virtual addressing makes traditional operating system services such as demand paging available to SPE threads. When an SPE thread references paged-out memory via its associated MFC, the MFC's memory management unit generates a page-fault exception and delivers it to the PPE. The PPE then services the page fault on behalf of the SPE. When the page fault service has completed, the PPE restarts the MFC transfer that caused the page fault.

#### 2.1.3 Element Interconnect Bus

The Element Interconnection Bus (EIB) [M. 06b], [et 05], [A. 05], [Sca09] is a communication bus internal to the Cell processor which connects the various on-chip system elements: the PPE processor, the memory controller (MIC), the eight SPE coprocessors, and two offchip I/O interfaces, for a total of 12 participants, as shown in Figure 2.6. The EIB has separate communication paths for commands (requests to transfer data to or from another element on the bus) and data. Each bus element is connected through a point-to-point link to the address concentrator, which receives and orders commands from bus elements, broadcasts the commands in order to all bus elements (for snooping), and then aggregates and broadcasts the command response. The command response is the signal to the appropriate bus elements to start the data transfer.

The EIB data network consists of four 16- byte-wide data rings: two running clockwise, and the other two counterclockwise. Each ring potentially allows up to three concurrent data transfers, as long as their paths don't overlap. To initiate a data transfer, bus elements must request data bus access. The EIB data bus arbiter processes these requests and decides which ring should handle each request. The arbiter always selects one of the two rings that travel in the direction of the shortest transfer, thus ensuring that the data won't need to travel more than halfway around the ring to its destination. The arbiter also schedules the transfer to ensure that it won't interfere with other in-flight transactions. To minimize stalling on reads, the arbiter gives priority to requests coming from the memory controller. It treats all others equally in round-robin fashion. Thus, certain communication patterns will be more efficient than others.

The EIB operates at half the processor-clock speed. Each EIB unit can simultaneously send and receive 16 bytes of data every bus cycle. The EIB's maximum data bandwidth is limited by the rate at which addresses are snooped across all units in the system, which is one address per bus cycle. Each snooped address request can potentially transfer up to 128 bytes, so in a 3.2GHz Cell processor, the theoretical peak data bandwidth on the EIB is 128 bytes  $\times$  1.6 GHz = 204.8 Gbytes/s.

The on-chip I/O interfaces allow two Cell processors to be connected using a coherent protocol called the broadband interface (BIF), which effectively extends the

Figure 2.6: Element interconnect bus (EIB)

multiprocessor network to connect both PPEs and all 16 SPEs in a single coherent network.

### 2.2 Playstation3

Currently the easiest and the cheapest way to gain access to a Cell processor is the Sony PlayStation 3 (PS3) [Son]. As mentioned before, Cell processor was originally designed for PS3 and the vision was to achieve 1,000 times the performance of PlayStation 2. Due to the need of access to the Cell's computational power a Linux based operating system designed to run on PS3. The need for real Cell hardware mainly derives from the fact that IBM's Cell simulator is very slow. Today anybody can have access to the Cell processor by just installing an OS on PS3 and using it as a normal PC with high capabilities. Although PS3 is an easy solution it may not be the best, PS3 has some limitations on the performance of Cell. The main limitations are the small memory, only 256 MB and the availability of only six SPEs out of eight. One of the eight SPEs is disabled at the hardware level due to yield reasons and another SPE is reserved for use by the PS3's operating system. Apart from these limitations PS3 remains a good choice for anybody who wants to have its own Cell processor.

## 2.2.1 Operating System

The PS3 is shipped with an operating system called Game OS but is capable of running Linux OS if installed on the console's hard drive. The Linux operating system runs on the PS3 on top of a virtualization layer, also called hypervisor, the Game OS. This means that all the hardware is accessible only through the hypervisor calls. The hardware signals the kernel through virtualized interrupts. The interrupts are used to implement callbacks for non-blocking system calls. The Game OS permanently occupies one of the SPEs and controls access to the hardware. A direct consequence of this is larger latency in accessible like the accelerated graphics card. At this point, there are numerous distributions that have official or unofficial support for PS3. The distributions that are currently known to work on PS3 (with varying levels of support and end-user experience) include:

- Fedora Core 7 [Red]

- YellowDog 6.0 [Ter]

- Gentoo PowerPC 64 edition [Gen]

- Debian [Deb]

All the distributions mentioned include Sony-contributed patches to the Linux kernel-2.6.16 to make it work on PS3 hardware and talk to the hypervisor. However, the Linux kernel version 2.6.20 has PS3 support already included in the source code without the need for external patches.

### 2.2.2 Memory System

The memory system is built of dual-channel Rambus Extreme Data Rate (XDR) memory. PS3 provides a modest amount of memory of 256 MB, out of which approximately 200 MB is accessible to Linux OS and applications. The memory is organized in 16 banks. Real addresses are interleaved across the 16 banks on a naturally aligned 128-byte (cache line) basis. Addresses 2 KB apart generate accesses to the same bank. For all practical purposes the memory can provide the bandwidth of 25.6 GB/s to the SPEs through the EIB, provided that accesses are distributed evenly across all the 16 banks.

#### 2.2.3 Network Card

The PS3 has a built-in GigaBit Ethernet network card. However, unlike standard PC's Ethernet controllers, it is not attached to the PCI bus. It is directly connected to a companion chip. The network card has a dedicated DMA unit, which allows making data transfer without PPE's intervention. One of many advantages of Gi-gaBit Ethernet is the possibility of increased frame size – so called Jumbo Frames. It can increase available bandwidth by 20% in some case and significantly decreases processor load when handling network traffic.

#### 2.2.4 Graphics Card

PS3 features special edition from NVIDIA and 256 MB of video RAM. Unfortunately, the virtualization layer does not allow access to these resources. At issue is not as much accelerated graphics for gaming as is off-loading of some of the computations to GPU and scientific visualization.

# Chapter 3

# Glimmer Algorithm

This chapter presents the Gene Locator and Interpolated Markov Modeler (Glimmer) algorithm that has been ported on the Cell processor. Glimmer was the primary microbial gene finder used at The Institute for Genomic Research (TIGR), where it was first developed, and has been used to annotate the complete genomes of over 100 bacterial species from TIGR and other labs. The methodology, the basic steps of algorithm as well as matters of algorithm input and output are introduced in this chapter.

### 3.1 An Introductory Background On Biology

One of the fundamental principles of biology is that within each cell, DNA that comprises the genes encodes RNA which in turn produces the proteins that regulate all of the biological processes within an organism.

DNA is a double chain of simpler molecules called nucleotides, tied together in a double helix helical structure. The nucleotides are distinguished by a nitrogen base that can be of four kinds: adenine (A), cytosine (C), guanine (G) and thymine (T). Adenine (A) always bonds to thymine (T) whereas cytosine (C) always bonds to guanine (G), forming base pairs. DNA can be specified uniquely by listing its sequence of nucleotides, or base pairs. Proteins are molecules that accomplish most of the functions of a living cell, determining its shape and structure. A protein is a linear sequence of molecules called amino acids. Twenty different amino acids are commonly found in proteins. Similar to DNA, proteins are conveniently represented as a string of letters expressing their sequence of amino acids. A gene is a contiguous stretch of genetic code along the DNA that encodes a protein. Not all parts of a DNA molecule encode genes; some segments, called introns, have no influence on protein synthesis[Dav05].

In molecular genetics, an open reading frame (ORF) is a portion of an organism's

genome which contains a sequence of bases that could potentially encode a protein. In a gene, ORFs are located between the start-code sequence (initiation codon) and the stop-code sequence (termination codon). ORFs are usually encountered when sifting through pieces of DNA while trying to locate a gene. Since there exist variations in the start-code sequence of organisms with altered genetic code, the ORF will be identified differently[The].

## 3.2 Gene Identification Problem

Accurate microbial gene identification is becoming ever more important with the increasing rate of whole genome sequencing projects. In the past year alone, eight new bacterial and archaeal genomes have appeared, and the pace continues to accelerate. Each new genome contains thousands of new genes, all of which are deposited into public databases. These genes then become the basis for much further research into the biology of these organisms, and their sequences are used for further biological study. For work such as microarray analysis, in which specific sequences are arrayed onto a substrate and used as probes to measure expression levels, the accuracy of gene predictions is critical. The same point can be made about knockout experiments, which are an important tool to use in determining the function of the large numbers of genes whose function is unknown at the time of publication. Such hypothetical proteins typically comprise 30–40% of the genes in a newly sequenced genome.

The sizes of biological sequence databases are usually very large. Not all the sequences are coding, namely are a template for a protein. For example, in the human genome only 3%-5% of the sequences are coding. Due to the size of the database, manual searching of genes who do code for proteins is not practical. Genefindings aim to provide computational methods to automatically identify genes that encode proteins[Ste99][Dav05].

### **3.3** Interpolated Markov Models and Markov Chains

Markov models are a well-known tool for analyzing biological sequence data, and the predominant model for microbial sequence analysis is a fixed-order Markov chain[BM93][BD95]. A fixed order Markov model predicts each base of a DNA sequence using a fixed number of preceding bases in the sequence. For example, a  $5^{th}$ -order model uses the five previous bases to predict the next base. However, learning such models accurately can be difficult when there is insufficient training data to accurately estimate the probability of each base occurring after every possible combination of five preceding bases. In general, a  $k^{th}$ -order Markov model for DNA sequences requires  $4^{k+1}$  probabilities to be estimated from the training data (e.g., 4096 probabilities for a  $5^{th}$ -order model). In order to estimate these probabilities, many occurrences of all possible kmers must be present in the data.

An IMM overcomes this problem by combining probabilities from contexts of varying lengths to make predictions, and by only using those contexts (oligomers) for which sufficient data are available. In a typical microbial genome some 5mers will occur too infrequently to give reliable estimates of the probability of the next base, while some 8mers may occur frequently enough to give very reliable estimates. In principle, using longer oligomers is always preferable to using shorter ones, but only if sufficient data is available to produce good probability estimates. An IMM uses a linear combination of probabilities obtained from several lengths of oligomers to make predictions, giving high weights to oligomers that occur frequently and low weights to those that do not. Thus an IMM uses a longer context to make a prediction whenever possible, taking advantage of the greater accuracy produced by higher-order Markov models. Where the statistics on longer oligomers are insufficient to produce good estimates, an IMM can fall back on shorter oligomers to make its predictions.

#### 3.3.1 Markov Chains

A Markov chain [Ste98] [Ste99] [Twe05] is a sequence of random variables  $X_i$ , where the probability distribution for each  $X_i$  depends only on the preceding k variables  $X_{i-1}, ..., X_{i-k}$ , for some constant k. For DNA sequence analysis, a Markov chain models the probability of a given base b as depending only on the k bases immediately prior to b in the sequence. We refer to these preceding k bases as the context of base b in the sequence. A first order Markov chain is a sequence of random variables where the probability that  $X_i$  takes a particular value only depends on the preceding variable  $X_{i-1}$ . Note that for DNA sequences a first-order Markov chain is specified completely by a matrix of 16 probabilities: p(a|a), p(a|c), ..., p(t|t). The most common type of Markov chain is a fixed-order chain, in which the entire k-base context is used at every position. For example, a fixed  $5^{th}$ -order Markov chain model of DNA sequences comprises  $4^5 = 1024$  probability distributions, one for each possible 5mer context. Such fixed  $5^{th}$ -order models have proven effective at gene prediction in bacterial genomes[BM93][BD95]. Ideally, larger values for k are always preferable. Unfortunately, because the training data available for building models is limited, we must limit k. In most collections of DNA coding sequences, however, there is substantial variability in the frequency of occurrence of different kmers.

The Glimmer algorithm uses seven submodels to find genes in microbial DNA. The algorithm builds six submodels one for each of the possible reading frames (three forward and three revers) and a seventh model for non-coding regions. Each model makes different predictions for the bases in the three codon positions. Even with a  $0^{th}$ -order model, the frequency of g in codon position 1 will be different from its frequency in another frame, so even this very weak model has some ability to identify the right reading frame for a gene.

Using the Markov models for each of the six possible frames plus a model of non-coding DNA, we can straightforwardly produce a simple algorithm for finding genes. Simply score every orf using all seven models, and choose the model with the highest score. The scores can be normalized so they represent the probability that a sequence is coding. If the model corresponding to the true coding region in the correct frame scores the highest, then the orf can be labeled as a gene.

#### 3.3.2 Interpolated Markov Models (IMMs)

An Interpolated Markov Model (IMM)[Ste98][Ste99] uses a combination of all the probabilities based on 0, 1, 2, ..., k previous bases, where k is a parameter given to the algorithm. In GLIMMER, we use k = 8. Thus for oligomers that occur frequently, the IMM can use an 8<sup>th</sup>-order model, while it might use a 5<sup>th</sup> or even lower-order model for rare oligomers. In order to 'smooth' its predictions, an IMM uses predictions from the lower-order models, where much more data is available, to adjust the predictions made from higher-order models.

During training, GLIMMER computes the probability of each base a, c, g, t, following all kmers for  $0 \le k \le 8$ . Then, for each kmer it computes a weight to use in combining the predictions of different order models. Details of the algorithm for computing these weights are given in the Algorithm and system design section. Once the weights are computed, GLIMMER evaluates new sequences by computing the probability that the model M generated the sequence S, P (S|M). This probability is computed as

$$P(S|M) = \sum_{x=1}^{n} \mathbf{IMM}_{\mathbf{8}}(S_x)$$

(3.1)

where  $S_x$  is the oligomer ending at position x, and n is the length of the sequence.  $IMM_8(S_x)$ , the 8<sup>t</sup>h-order interpolated Markov model score, is computed as

$$IMM_{k}(S_{x}) = \lambda_{k}(S_{x-1}) \cdot P_{k}(S_{x}) + [1 - \lambda_{k}(S_{x-1})] \cdot IMM_{k-1}(S_{x})$$

(3.2)

where  $\lambda_k(S_{x-1})$  is the numeric weight associated with the kmer ending at position x – 1 in the sequence S and  $P_k(S_x)$  is the estimate obtained from the training data of the probability of the base located at x in the  $k^{th}$ -order model. Thus, the  $8^{th}$ -order IMM score of an oligomer is a linear combination of the predictions made by the  $8^{th}$ ,  $7^{th}$  and lesser-order models all the way down to the  $0^{th}$ -order model, which is just the simple prior probabilities of a, c, g, t.

#### 3.3.3 Interpolated Context Models (ICMs)

Interpolated context models (ICMs)[Ste99] are a further extension of IMMs. For a given context  $C = b_1 b_2 \dots b_k$  of length k, the IMM in GLIMMER 1.0 computes a probability distribution for  $b_{k+1}$  using as many of the bases immediately preceding  $b_{k+1}$  as the training data set allows. The ICM is more flexible and can select any of the bases in C (not just those adjacent to  $b_{k+1}$ ) to determine the probability of  $b_{k+1}$ . In general, from a given context, the ICM will choose approximately the same number of bases as the IMM. In GLIMMER 2.0, the motivation for choosing bases other than those at the end of the context is the fact that in coding regions the significance of a given base depends strongly on its position in a codon.

The criterion employed by the ICM to select which bases of a context C to use is mutual information. The mutual information between a given pair of discrete random variables X and Y is defined to be:

$$I(X;Y) = \sum_{i} \sum_{j} P(x_{i}, y_{i}) log(\frac{P(x_{i})P(y_{i})}{P(x_{i}, y_{i})})$$

(3.3)

where  $x_i$  and  $y_j$  are the values taken by random variables X and Y respectively, and  $P(x_i, y_j)$  is the joint probability of  $x_i$  and  $y_j$  together.

To construct an ICM with context length k from a training set T of DNA sequences, we begin by considering all windows (i.e. oligomers) of length k+1 that occur in T. The algorithm lets random variable  $X_1$  be the distribution of bases in the first position of those windows;  $X_2$  be the distribution of bases in the second position; and so on through  $X_{k+1}$ . It then calculates the mutual information values  $I(X_1; X_{k+1}), I(X_2; X_{k+1}), \ldots, I(X_k; X_{k+1})$ , and choose the maximum. Suppose that maximum is  $I(X_j; X_{k+1})$ . It then partitions set of windows into four subsets based on the nucleotide that occurs in position j in the window.

The same procedure can now be performed again for each of the four sets of windows. Within each set, the position that has the highest mutual information with the base at position k+1 is chosen. The four nucleotide values at that position induce a further partitioning of the current set of windows into four subsets.

This process can be viewed as constructing a tree of positions within context strings. A sample portion of such a tree is shown in Figure 3.1. The construction is terminated when the tree depth reaches a predetermined limit, or when the size of a set of windows becomes too small to be useful to estimate the probability of the last base position.

Each node in the ICM decomposition tree represents a set of windows that provide a probability distribution for the final base position. The root node, which includes all possible windows, represents a  $0^{t}h$ -order Markov model. All other nodes give a probability distribution for the final base position, conditional on a specific

Figure 3.1: Sample ICM decomposition tree