## TECHNICAL UNIVERSITY OF CRETE

DIPLOMA THESIS

## A Full System Simulator for Disaggregated Computing Platforms and Cloud Data Centers

Konstantinos N. Kyriakidis

July 26, 2017

A thesis submitted in fulfillment of the undergraduate requirements in the: School of Electrical and Computer Engineering *Tripartite Committee:* Professor Dionisios Pnevmatikatos Professor Apostolos Dollas Faculty Researcher Dimitrios Theodoropoulos

## Abstract

Modern computing systems servers, whether low-power or high-end ones are created around a common design principle: the mainboard and its hardware components form a baseline, a monolithic building block that the rest of the hardware/software builds upon. The proportionality of the resources remains static throughout the machine lifetime, with known ramifications (1) in terms of low system resource utilization, costly upgrade cycles, and degraded energy proportionality.

As a result, a novel approach takes on the challenge of revolutionizing the lowpower computing market by breaking server boundaries through materializing the concept of disaggregation. Such an innovative approach needs good planning and a lot of preliminary work in order to reach the desired outcome.

Thus, a full system simulator platform is required, capable of modeling this kind of a data center environment in order to catch a glimpse of what it can deliver in terms of performance. This thesis is all about this idea and its implementation. Furthermore, it provides an introduction to the virtual platforms and their significance in hardware system evaluation before prototyping.

## Acknowledgements

I want to give sincere thanks to my parents that supported me all these years. Without their aid, I wouldn't be able to study at all and achieve my personal dreams and ambitions. So I want to dedicate this diploma thesis to both of them. I also want to thank my supervisor, Professor Dionisios Pnevmatikatos, who gave me the opportunity to be a member of his research team as an undergraduate student. He was the one that instructed to select my thesis subject and helped me ever since. Furthermore, I have to specifically mention the support that I had from my research coordinator and personal friend Dimitris Theodoropoulos. He was my guide and I thank him for that. This Thesis is associated with the dRedBox project and in my case, it has been supported by Imperas as regards to the simulation platform. Finally, I would like to name all those that actively helped me throughout my work. Duncan Graham and Jim Straus, two of the OVP forum administrators. Oscar Gonzales del Dios, Hugo Daniel Mayer and Alejandro Molina-Sanchez form B.S.C. Dimitrios Syrivelis from the University of Thessaly and also Iosif Koidis from the T.U.C. Lastly, a huge shoutout to my friends and studying partners Vasilis Amourianos and Kostas Malavazos. Thank you, guys!

# Contents

| 1 | Introduction |                                                                         |          |  |  |  |  |  |

|---|--------------|-------------------------------------------------------------------------|----------|--|--|--|--|--|

|   | 1.1          |                                                                         |          |  |  |  |  |  |

|   | 1.2          |                                                                         |          |  |  |  |  |  |

|   |              | 1.2.1 The embedded software evolution                                   | 8        |  |  |  |  |  |

|   |              | 1.2.2 Simulating this new design using virtual platforms                | 9        |  |  |  |  |  |

|   |              | 1.2.3 Why Imperas?                                                      | 9        |  |  |  |  |  |

| 2 | Rel          | elated Work 1                                                           |          |  |  |  |  |  |

|   | 2.1          | General data center improvement approaches                              |          |  |  |  |  |  |

|   | 2.2          | Related dRedBox work                                                    |          |  |  |  |  |  |

|   |              | 2.2.1 Ramulator: A Fast and Extensible DRAM Simulator                   |          |  |  |  |  |  |

|   |              | 2.2.2 Simulating DRAM controllers for future system architecture explo- |          |  |  |  |  |  |

|   |              | ration                                                                  | 12       |  |  |  |  |  |

|   |              | 2.2.3 Disaggregated Memory Architectures for Blade Servers              | 12       |  |  |  |  |  |

|   |              | 2.2.4 Related work inside the Technical University of Crete             | 13       |  |  |  |  |  |

| 3 | Pla          | tform design: Architecture and Subsystems                               | 14       |  |  |  |  |  |

| J | 3.1          | Server and Rack Level Architecture                                      | 15       |  |  |  |  |  |

|   | 3.2          | Electro-optical switched interconnect                                   | 15       |  |  |  |  |  |

|   | 3.3          | Memory Disaggregation                                                   | 16       |  |  |  |  |  |

|   | 3.4          | Operating system support for disaggregation                             | 17       |  |  |  |  |  |

|   | 3.5          | Resource allocation                                                     | 18       |  |  |  |  |  |

|   | 3.6          | And now what?                                                           | 19       |  |  |  |  |  |

|   |              |                                                                         |          |  |  |  |  |  |

| 4 |              | nulation platform implementation                                        |          |  |  |  |  |  |

|   | 4.1          | The Imperas platform                                                    | 20       |  |  |  |  |  |

|   |              | 4.1.1 Imperas Developer Platforms                                       | 21       |  |  |  |  |  |

|   |              | 4.1.2 The OVP                                                           | 24       |  |  |  |  |  |

|   | 4.0          | 4.1.3 The Imperas Simulation System                                     | 25       |  |  |  |  |  |

|   | 4.2          | The Implementation                                                      | 26       |  |  |  |  |  |

|   |              | <ul><li>4.2.1 Semihosting and the Code Morphing Simulator</li></ul>     | 27<br>28 |  |  |  |  |  |

|   |              | 4.2.3 Building the platform                                             | 20<br>30 |  |  |  |  |  |

|   |              | 4.2.4 External Kernel and the Device Tree                               | 30<br>32 |  |  |  |  |  |

|   |              | 4.2.5 The Custom rootfs image, 'RUN' Scripts and the Internet Access    | 34       |  |  |  |  |  |

|   |              | 4.2.6 Simulating the Network Delay using an Intercept Library           | 35       |  |  |  |  |  |

|   | 4.3          | Completing the Simulated Platform Emulation                             | 37       |  |  |  |  |  |

| _ | _            |                                                                         |          |  |  |  |  |  |

| 5 |              |                                                                         | 38       |  |  |  |  |  |

|   | 5.1          | Verbose outputs and other Simulator Feedback                            | 38       |  |  |  |  |  |

|   |              | 5.1.1 Verbose outputs                                                   | 38<br>40 |  |  |  |  |  |

|   | 5.9          | 5.1.2 Other Simulator Feedback                                          | 40<br>40 |  |  |  |  |  |

|   | 5.2          |                                                                         |          |  |  |  |  |  |

|   | 5.3          | Best effort                                                             | 42<br>43 |  |  |  |  |  |

|   | <b>0.4</b>   | 5.4 Splash-3 [Barnes]                                                   |          |  |  |  |  |  |

| 6 | Conclusions and Future work |                                   |    |  |  |

|---|-----------------------------|-----------------------------------|----|--|--|

|   | 6.1                         | Contributions and lessons learned | 46 |  |  |

|   | 6.2                         | Is it worth it?                   | 46 |  |  |

|   | 6.3                         | Plans for the future              | 47 |  |  |

## 1 Introduction

There is currently an immense need for high-performing, parallel, distributed and heterogeneous computing across industries of any kind. We see that all sorts of high-end embedded systems are being used for any kind of industrial applications and their variety of uses is seemingly endless. From FPGA-based video analysis, aerial transportation guidance systems and all kinds of everyday safety/security accommodations that we enjoy, to national security applications, parallel supercomputers for advanced industrial manufacturing and cutting-edge medical equipment. The majority of these industries have been traditionally employing embedded computing, primarily for achieving low power consumption, cost reduction - thanks to fit-for-purpose designs - and for abiding by stringent real-time constraints.

Embedded systems have always been one of the simplest and easiest solutions. However, as the complexity of the problems that emerged increased, it led to a significant ramp up of the computational power and integration plurality of such designs. One of the main advantages of this evolution is that it has enabled the reduction of component development and maintenance costs through re-purposing of software/hardware used on conventional systems. In terms of modern data centers, the later in conjunction with the explosion of the penetration of mobile into the consumer and enterprise market is constantly pushing for higher performance low power systems-on-a-chip(SoC). High-end embedded computing systems, from small form factor boards to multi-chassis systems, exhibit superior features compared to conventional high-end server designs (i.e. dual or quad socket SMPs), across key performance indicators (KPIs) such as compute density, granularity of resource allocation, power consumption and virtual machine migration times.

These KPIs challenge the way we need to design the next generation computing systems to guarantee environmental, societal and business sustainability. Both technological trends are based on a common design axiom: the mainboard and its hardware components from the baseline, a monolithic building block that the rest of the system software, middleware and application stack build upon. The dRedBox [KSP+16] design proposes a customizable low-power data center architecture, moving from the paradigm of mainboard-as-a-unit to a flexible, software-defined block-as-a-unit. This approach allows an optimization of both performance and energy consumption. The baseline disaggregated building blocks to enable the on-demand hardware are, a) microprocessor SoC module, b) high-performance RAM module and c) accelerator (FPGA/SoC) module. Disaggregating components at that level significantly improves efficiency, increases resource utilization and has the potential to revolutionize the way the data centers are being built.

All of this sound very new, very promising and even thrilling. The question is this: is it worth it? The only way to answer that kind of questions is by testing it. There is no better way for us engineers to experiment with a new platform design to find out if it really is as good as it seems. This is why this Thesis is focused on my attempt to building a simulator platform in order to model a part of the original idea of the dRedBox server design. This job was not an easy task and it took a lot of hard work and countless trials and errors to get to a stable and easy to work simulator platform design. But finally, I think that I can say that I developed a sufficient and well-working simulator platform that can help us test the capabilities of the new idea of the dRedBox disaggregated server platform. The entire task of building this simulator platform from scratch can be found on chapter 4 but in the meantime let's say a few more things about the advantages of disaggregation, embedded systems and what lead us to experiment with those new ideas.

## 1.1 Motivation

Let us talk a little about how we decided to take up the task of trying to emulate the dRedBox platform. It all starts with all those weaknesses and disadvantages about data centers that I mentioned before. There are three inevitable limitations that are side-effects of the way data centers are being built today.

**First of all**, as we mentioned, the resource proportionality of the entire system follows the proportionality of the basic building block (mainboard), both at production and during upgrades. For instance, if at some point we decide to double the memory capacity in an operational system, we have extra costs because this action carries with it the obligation of adding all the additional but not necessary components throughout the server in order to follow the mainboard design.

In addition, the allocation of resources to processes or virtual machines is upper bounded by the resources available within the boundary of the mainboard, leading to spare resource fragmentation and inefficiencies. A great example to view what I am talking about is to take a look at an application that uses 100% of the CPU and only 40% of the server memory. This automatically means that we can't run any other workload not even memorybound and thus this 60% of free memory is unusable until the CPU-bound procedure is finished.

**Furthermore**, If we decide to upgrade any of the server boards this upgrade needs to be carried out to all other boards as well for reasons that we talked earlier. An upgrade can be as simple as changing to a later model of processor.

All of the above create the urgency of a radical solution. Many tries are already in action and some of them I am going to mention in chapter 2 (Related Work). Our approach for the disaggregated dRedBox system is described in the following subsection.

## 1.2 Disaggregation and the dRedBox approach

All those limitations that I described earlier have been adequately addressed in modern data centers at the peripheral level e.g. by Network Attached Storage (NAS) for persistent storage and PCIe off-board switches for network media. The introduction of the dRedBox aims to deliver a platform with memory disaggregation at the hardware integration level by interfacing the CPU chip memory controller with remote memory modules that can be located on the same or a remote mainboard tray. For example, this kind of memory disaggregation means that the memory resources can be allocated in a significantly more efficient way than traditionally. The connection is going to happen via a novel optical network interconnection technology capable of delivering performance up to 1800million transfers per second, and latencies close to 10ns when using state of the art DDR-to-DIMM interconnection. As for the approach, the hardware-level disaggregation and the software-defined wiring of the resources undertaken by dRedBox will be matched with a novel, required innovation on the system-software side.

In particular:

- Delivering novel hypervisor distributed support to share resources that will allow the disaggregated architecture to bootstrap (15) a full-fledged Type-1 hypervisor and execute commodity virtual machines. That way, by using the Type-1 hypervisor device driver techniques, the disaggregated memory support shall be further used for peripheral disaggregation with proper forwarding of Direct Memory Access (DMA) interrupts.

- Employing deep software-defined control of all resources at the hardware programmability level, including allocation of memory resources to micro-servers and softwaredefined network control. This hardware-orchestration software, running out off the

data-path resources, is to be interfaced via appropriate Application Programming Interfaces (APIs) with higher-level resource provisioning, management and scheduling systems, notably cloud management (e.g. OpenStack) and cluster management systems (e.g. Apache Mesos).

• Finally, reducing the power consumption, which is a key parameter for dReDBox and will be attacked at all layers. When designing the platform, the power consumption of hardware components will play a major role in their selection. The optical network will utilize key technologies that significantly reduce power consumption and improve latency. The hardware platform will provide a per component IPMIv2 interface that will allow the hypervisor and the orchestration tools to extensively control component mode of operation and also completely switch them off when not used. The later is due to the dRedBox central reservation system which will fully control the component interconnect, so in any given point in time it knows which components are in use. In this context, novel online myopic policies will be designed that can take instant decisions to migrate VMs and switch off resources. The target is to improve the power consumption by 10x compared to state-of-the-art platforms.

All of the above can give you a good idea of the course that the dRedBox platform idea is headed. It is an innovative approach to the major database resource allocation and power consumption problems. But it needs testing, and here is where my work comes into play. In this Thesis, I was given the task of creating a platform that can simulate this new environment. Based on the original dRedBox platform idea, that will be described in chapter 3, I started working on creating a working MPSoC emulator. By introducing the MPSoC emulation I am basically making the introduction to my thesis main work and I think that this is the best moment to do so. It is worth noting that all this work started by having only the initial dRedBox paper at hand and by having no idea what simulating program to use. The first step was to find a simulator platform/program, capable of simulating the architecture that we had in mind. But first, let me explain why we chose this approach in the first place.

## 1.2.1 The embedded software evolution

The embedded software contained in modern electronic products used by the majority of the population on a daily basis has evolved dramatically in recent years. This evolution came primarily in three dimensions:

- Scale: As the cost of the IC hardware production and products increases, the use of embedded software operating on standardized hardware platforms has become increasingly common. This lead to a tremendous growth of code required for each project and with it the effort to produce it.

- **Complexity**: Multi-core processor architectures are continuously improving, providing the necessary performance and capability to meet modern product requirements. However, as the hardware advances, coding these new processors has become exponentially more complex than previous generations.

- Quality: Modern electronic product functionality and quality requirements are more strict and higher than ever, suggesting a zero tolerance for post-production bugs. Another common thing these days is that embedded software has become harder to change as a product moves into production.

In the past, embedded software development and verification were typically performed by executing the codes on a prototype hardware platform for the design. The tests were performed until the product research team satisfied with a result. This approach was timeconsuming, highly impractical for all next generation high-end designs and also unreliable in terms of quality and use. Similar issues can be found not only in embedded software development but also in hardware verification procedures. A new solution has to be found. The answer to this is the use of virtual platforms.

## 1.2.2 Simulating this new design using virtual platforms

Virtual platforms are an alternative to hardware prototypes. Software models of the key components in a processor platform are combined to form an executable system. This kind of models have enough functionality to execute the code correctly and do all the verification procedures and testing. Nevertheless, they retain a certain level of abstraction that provides the performance necessary for rigorous testing.

Typically, all virtual platforms make use of Instruction Accurate (IA) processor models. They also contain a large variety of abstract memory blocks and key peripherals making it possible to create all kinds of different virtual platform designs. The virtual platform needs to be accurate enough so that the software can't tell the difference between running on an actual platform or not, and also production binaries of the embedded software should be able to run unmodified.

The main advantages of using virtual platforms are:

- Early development potential: A virtual platform model can be available far quicker than any prototype hardware equivalent, thus creating the potential for much earlier software development and testing than before, saving off time for a product's time-to-market.

- Visibility and Controllability: Many hardware prototypes make it difficult to view internal registers and signals and also offer no opportunity to change or control hardware and software execution. Within a well-constructed virtual platform, the tester can view all nodes and apply a range of controls. This is essential for effective verification.

- Performance and Accessibility: Prototype hardware platforms often have limited availability in their early production stages. This means a restriction on the amount of testing that can be performed. One of the key aspects of using virtual platforms is that they can be replicated on all available compute platforms, allowing concurrent use by individual members across large teams, or many test platforms operating in parallel. Also with good planning, correct and careful construction and some abstract but correct limitations, they can execute faster than the actual final hardware, allowing for extended testing cycles.

But the question remains: What development environment to use? The construction of a virtual platform can vary greatly according to each new designs needs and can have a significant impact on their performance. In our case, after testing other development platforms as well, Imperas was the choice to go, because it has the right technology and expertise to provide fast and effective development environments based on virtual platforms.

## 1.2.3 Why Imperas?

After testing other platforms as well e.g. the GEM5, Imperas gave us the package that we were looking for. Imperas develops and markets state-of-the-art virtual platforms and tools to enable the most comprehensive embedded software development, debug and test solutions available today. It combines advanced simulation algorithms, modeling excellence, and a broad range of tools to produce a system that offers:

- Very fast execution performance: Imperas leading JIT code-morphing simulation technology allows models of processors, such as the ARM® Cortex<sup>TM</sup> A-72, to execute at a peak speed of almost 5,000 Million Instructions per Second (MIPS), and booting multi-core Linux in under 4 seconds, on an average desktop PC, as they proclaim.

- Extensive Library of Accurate Models: The Imperas OVP model library includes a full range of processors from ARM, Imagination MIPS, PowerPC, Open-Cores, Renesas, Synopsys ARC, Altera Nios II, and Xilinx Microblaze. The models are fully featured, e.g. ARM's TrustZone® and Virtualization technology are supported. Example platforms and peripherals are also available that run for example Linux, Android, Nucleus, FreeRTOS, uClinux, eCos. Models operate with SystemC TLM2 and other standards, making it easier for a novice user like me to get familiar with this tool.

- Advanced Development Tools: Powerful verification, analysis, and profiling tools plus a multi-core debugger use ToolMorphing<sup>TM</sup> to merge them into the simulator, to operate with minimal performance degradation or execution alteration. Tools operate from bare metal instructions to CPU and OS-Aware abstract models and can be customized for platform and scenario specific operations.

This environment has been used by Imperas customers to find bugs in previously fully tested production code. Furthermore, in 2008, Imperas founded Open Virtual Platforms (OVP), an industry consortium dedicated to providing open-source models and infrastructure to create virtual platform models as easily as possible making it a very friendly but also a very strong entry and advanced level embedded development tool. OVP provides an easy entry point into the world of virtual platforms with a today's community of over 10,000 members from many leading electronics companies and academic institutions. OVP models operate with other standards, including SystemC and TLM2, while building on the Imperas simulation technology to enable high-performance, high-capability models for any environment. From all of the above, you can see why this was the way we chose this program to work with.

# 2 Related Work

On the road to developing a better and more efficient data center capable of meeting all the new technological, economical and performance requirements, we are not alone. Other research team and institutes have produced their own alternative ideas/works as a solution to this matter. Furthermore, I was not the only one working on the dRedBox project. There is already a lot of work done in our lab and also others like B.S.C. and there is still a lot of work in progress. In this chapter, I am going to mention some of the more recent and related work that has been done or is currently being developed, regarding the data center evolution and also the disaggregated dRedBox approach on this matter.

## 2.1 General data center improvement approaches

Starting off I would like to mention some distinct approaches regarding the evolution of data centers today. These are not all the works that are done or currently under development but are a good indication of where projects other than the dRedBox are headed and why do we think that these solutions are not perfect.

- The RAMCloud: As I mentioned before, trending data-intensive workloads most of the time require resources disproportional to the fixed proportionality of the mainboard. In this spirit, the RAMCloud project outlines that strategic use of (permanent) DRAM instead of storage significantly improves the execution time of specific, widely used, cloud applications. To achieve this it aggregates memory modules that are located on different traditional mainboards, using a fast network and appropriate software, wasting this way a significant amount of processor resources and power. Also, integrated CPU/memory/storage mainboard architectures can inherently create resource inefficiencies, both in terms of upgrades and workload-proportional system utilization. This creates the requirement of whole mainboard upgrades and also server bound resource allocation that guarantees a suboptimal investment of capitalization and operational expenses.

- Dynamic CPU, memory, and accelerator scaling: Many research teams have tried to integrate the idea of dynamic CPU, memory, and accelerator scaling at runtime in response to dynamically changing service and application needs. This is suboptimal, due to the fact that it is bounded by what is available in the mainboard tray. If more memory or CPU resources are required, VM migration to another tray is undertaken and that means an incurring overhead and performance degradation.

## 2.2 Related dRedBox work

Enough with the different approaches. Let us talk about our line of work. A lot of dRedBox related projects are either completed or are currently under development. So at this point I think is the best place to overview the work of other Institutes and Universities and closing with the research that takes place at the Technical University of Crete by prof. D.Pevmatikatos's research team.

## 2.2.1 Ramulator: A Fast and Extensible DRAM Simulator

[KYM16] Due to that both industry and academia have proposed many different roadmaps for the future of DRAM this project targets the growing need for an extensible DRAM simulator. They focus on a project that can be easily modified to judge the merits of today's DRAM standards as well as those of tomorrow. A fast and cycle-accurate DRAM simulator that is built from the ground up for extensibility. Unlike existing simulators, Ramulator is based on a generalized template for modeling a DRAM system, which is only later infused with the specific details of a DRAM standard. Thanks to such a decoupled and modular design, Ramulator is able to provide out-of-the-box support for a wide array of DRAM standards: DDR3/4, LPDDR3/4, GDDR5, WIO1/2, HBM, as well as some academic proposals (SALP, AL-DRAM, TLDRAM, RowClone, and SARP). Importantly, Ramulator does not sacrifice simulation speed to gain extensibility: According to their evaluations, Ramulator is 2.5× faster than the next fastest simulator. Also, notice that the Ramulator project is released under the permissive BSD license.

## 2.2.2 Simulating DRAM controllers for future system architecture exploration

[HAK<sup>+</sup>14] Compute requirements are increasing rapidly in systems ranging from mobile devices to servers and these often massively parallel architectures, put increasing requirements on memory bandwidth and latency. The memory system greatly impacts both system performance and power usage so it is key to capture the complex behavior of the DRAM controller when evaluating CPU and GPU performance. By using full-system simulation, the interactions between the system components is captured. However, traditional DRAM controller models focus on modeling interactions between the controller and the DRAM rather than the interactions with the system. Moreover, the DRAM interactions are modeled on a cycle-by-cycle basis, leading to inflexibility and poor simulation performance. This work presents a high-level memory controller model, specifically designed for full-system exploration of future system architectures. This event-based model is tailored to match a contemporary controller architecture, and captures the most important DRAM timing constraints for current and emerging DRAM interfaces, e.g. DDR3, LPDDR3 and WideIO. This shows how the controller leverages the open-source gem5 simulation framework and a comparison with a state-of-the-art DRAM controller simulator. The results show that their model is 7x faster on average while maintaining the fidelity of the simulation. To highlight the capabilities of their model, they show that it can be used to evaluate a multi-processor memory system.

## 2.2.3 Disaggregated Memory Architectures for Blade Servers

[Lim10] Current trends in memory capacity and power in servers indicate the need for memory system redesign. Per-server memory demands are increasing due to large memory applications, virtual machine consolidation, and bigger operating system footprints. This large amount of memory required for these applications is leading to memory power being a substantial and growing portion of server power budgets. As these capacity and power trends continue, a new memory architecture is needed that provides increased capacity and maximize resource efficiency. This thesis presents the design of a disaggregated memory architecture for blade servers that provides expanded memory capacity as well as dynamic capacity sharing across multiple servers. Unlike traditional architectures that co-locate compute and memory resources, the proposed design disaggregates a portion of the servers' memory, which is then assembled in separate memory blades optimized for both capacity and power usage. The servers access memory blades through a redesigned memory hierarchy that is extended to include a remote level that augments local memory. Through the shared interconnect of blade enclosures, multiple compute blades can connect to a single memory blade and dynamically share its capacity. This sharing increases resource efficiency by taking advantage of the differing memory utilization patterns of the compute blades. In this thesis, two system architectures are evaluated that provide operating system-transparent access to the memory blade; one uses virtualization and a commodity-based interconnect, and the other uses minor hardware additions and a high speed interconnect. Both are able to offer up to ten times higher performance over memory-constrained environments. Finally, by extending the principles of disaggregation to both compute and memory resources, new server architectures are proposed that provide substantial performance-per-cost benefits for large-scale data centers over traditional servers.

## 2.2.4 Related work inside the Technical University of Crete

Our institute already has experience in this field of work. This work was the first one about building a **Full System Simulator**, but it was not the first one about testing disaggregated data centers. Two thesis projects have already been presented in our School and I will roughly describe them here. Note that these two were not so different from each other.

• Andreas Andronikakis. Memory System Evaluation for Disaggregated Cloud Data Centers. Chania 2017.

The existing architecture of Cloud Data Centers is characterized by high energy consumption and a great waste of resources. This thesis refers to estimating the memory of cloud data centers with disaggregated (or disintegrated) servers, ie servers whose components and/or resources are in separate sub-assemblies, regarding their physical location. This Disaggregated Architecture System aims to change the traditional way of organizing a Data Center by proposing a more flexible and software-modulated integration around blocks, the Pooled Disaggregated Resources, as opposed to traditional unification around from the mainboard. The purpose of this diploma thesis is to study and develop a unified (modular) memory simulation tool of the above architecture, driven by the execution of an application, on the previously described DiMEM Simulator (Disaggregated Memory System Simulator). He studied the Dynamic Binary Instrumentation, the understanding of Cache levels and their simulation methods, the implementation of the Disaggregated Architecture Memory simulation, and experimentation with various parameters. The results approximately present the overall behavior of a Memory System of a Disaggregated Cloud Data Center.

## • Orion Papadakis. Memory System Evaluation of Disaggregated High-Performance Parallel Systems. Chania 2017.

Nowadays research about Disaggregated Architecture Systems aims to change the traditional mainboard-organized Data Center structure by proposing a more flexible and software-controlled one, organized around Pooled Disaggregated Resources. This thesis is part of the DiMEM Simulator, a modular execution-driven Disaggregated Memory Simulation tool study, and implementation. That tool approximately tries to depict the Disaggregated Memory System behavior using HPC workload. The DiMEM Simulator couples the Intel PIN framework with DRAMSim2 Memory Simulator, where that thesis also focuses. The main study object is the DRAMs, the Memory Simulation methods, the Disaggregated Memory Simulation implementation, as well as the parameters experimentation. This work's results show the approximated Disaggregated Memory System Behavior.

# 3 Platform design: Architecture and Subsystems

In this chapter, we are going to focus on the revolutionizing data center design as envisioned by the dRedBox project. I am going to present to you a detailed architecture and subsystems overview of the server platform that we want to create and also it's key modules, general specifications, and functionality.

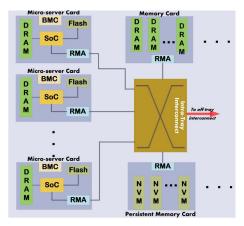

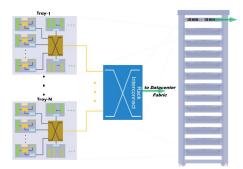

DRedBox adopts a vertical architecture(2) to address the disaggregated challenges. At the lowest level, the optical interconnect architecture is used for remote memory communication, with latencies in the tenths of nanoseconds. The interface facilitating remote memory communication will be decoupled from the processor unit, and appropriately integrated into the system interconnect. Forwarding operations will be software controlled to provide the necessary support to other dReDBox components. The dRedBox data center will also adopt the Virtual Machine (VM) as the execution container and several challenges will be addressed at the hypervisor and orchestration tools level, like the implementation of RDMA-like support for peripheral communications using standard DMA programming as well as power consumption control support. In figures 1 and 2, I depict the high-level block diagrams of a target's server(blade) and rack-level architecture.

Figure 1: Block Diagram of one type of dReDBox server[tray-mainboard]

Figure 2: Block Diagram of high-level dReDBox Rack-scale architecture

## 3.1 Server and Rack Level Architecture

dRedBox aims to deliver at least two types of hardware component blocks and one type of mainboard tray. Both blocks will be interfaced via Remote Memory Adapters (RMA) to the dRedBox mainboard. More specifically, a compute block, as featured in Figure 1, will have a high-performance SoC integrated with a local RMA, local memory, flash memory and an Ethernet-based Board Management Controller (BMC). Figure 1 also depicts 2 memory blocks, featuring DRAM and NVM module. They are both interfaced to the rest of the mainboard chassis via their local RMA and can also serve as an accelerator module. These memory blocks will be interfaced with a much higher bandwidth interface (40G/100G) in order to support the large scale network monitoring used for the dRedBox accelerator framework.

The generic dRedBox is aimed to feature a series of memory slots, appropriately interconnected in order to provide:

- 1. power,

- 2. a serial electrical interface to the electro-optical crossbar chip,

- 3. also, a PCIe interface, so that selected DIMM( dual in-line memory module) slots provide connectivity to a PCIe switch, and

- 4. a per component IPMIv2 (3) interface that enables intelligent IPMIv2-based management from the orchestration tools.

Two or more mainboards are aimed to be featured inside a tray and get interconnected with each other via the optical network. In Figure 2, I depict a set of dRedBox mainboards interconnected to a rack-level interconnect, forming the desired disaggregated Rack-Scale architecture.

The dRedBox also aims at delivering a fully-functional PCB prototype of the described platforms in several copies to be used for the integration of the rest of the subsystems and use case demonstrations. More specifically, the mainboard will be a small factor prototype appropriate for a data-center-in-a-box type configuration.

## 3.2 Electro-optical switched interconnect

A disaggregated rack-scale data center with high density, poses a series of challenges to the system interconnect. Scaling of the network along with controlling end-to-end latency and power consumption requires the addition of switches, links, and hierarchy levels to support the resource pooling. Each switch that is added to the network must be connected to both a higher and lower hierarchy level and has upfront implications to the switch radix and network topology selected. One of the challenges is to decide the number of interfaces to be used for the various layers of the interconnection hierarchy(in-tray, off-tray, off-rack), as driven by workload requirements specification and technology density/cost. In any configuration, the design goal is to minimize the number of layers used since more layers imply more switches and thus higher cost as well as power consumption and latency.

Fully non-blocking networks (logical full mesh topology) typically employ a Clos (17) topology [Clo53], [ZGY10]. In our case, the Clos network is the most efficient topology and it is possible to implement when meeting these two conditions:

- 1. The node has enough interfaces to connect to all switches and

- 2. The switch has enough interfaces to connect to all nodes and switches symmetrically.

The limiting factor here, is the number of available ports on the switching device and since this number is limited, Clos network used are more than a single stage. 3- or 5-stages are common in large data centers.

Moving on, increasing the chip I/O bandwidth is not a simple task since the packaging technology is quickly reaching its limit. With more and more SerDes(4) added to the package, the trace breakout into the PCB becomes a limiting factor since - at high line rate - traces cannot be brought close to each other without special design. The complexity associated with trace breakout implies that the SerDescan be placed only on the perimeter of the package. Their number is thus constrained by the package size and the number of BGA pins that may be used on the perimeter. Currently, the state of the art is roughly 150 SerDes/package and this number is not expected to exceed 250 with very complicated and power-hungry large package design.

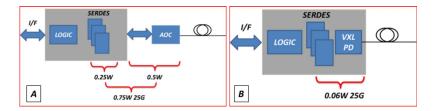

As a solution to this problem, the dRedBox introduces the addition of optical I/O to the switching device. More information can be found in references described in [Has14] and [HBG<sup>+</sup>14]. Integrating a large, two-dimensional optical interconnect directly on an ASIC has the benefit that low power SerDes can be used, as they need to drive only a fiber link compared to driving an approximate 30" metal trace on a board. The power saving is by a factor of 10x and is shown for the two cases in Figure 3.

Figure 3: Power consumption of an electrical I/O (A) and an optical I/O (B); the logic block is assumed to be the same in both cases

Parallel optical interconnect directly to the SoC ASIC allows an increase in both the switch radix and the bandwidth of the device. Since data flow to and from the ASIC is routed via the optical interface, the number of SerDes used for I/O is the number of optical lanes utilized. The logic to be implemented is L2 forwarding with full crossbar functionality. A fiber matrix is assembled above the optoelectronic matrices to enable card-to-card and tray-to-tray connectivity. It is worth noting that some of the I/O can be still routed through conventional electrical SERDES, thus, the overall I/O bandwidth of the device is the combination of both optical and electrical I/O.

And now some numbers. With the optical interconnect integrated directly into the SoC ASIC, we expect a network size of 1.5Pb/s to be attainable in a single-stage fully non-blocking topology with about textbf10% of the number of devices needed with other technologies. Thus the power saving and latency gains from this technology and design are evident. Furthermore, scaling of the data center network is enabled using this integrated electro-optical switch. Lastly, since the chip radix is in the 15Tb/s range, the size of the network that may be obtained in a single-stage Clos topology is larger than any network using conventional SerDes technology.

## 3.3 Memory Disaggregation

Memory disaggregation will require appropriate support starting from the lowest level which is the memory interconnect architecture. In Non-Uniform Memory Access (NUMA) architectures today, the Dual In-line Memory Modules(DIMM) are typically the slowest but also the largest elements in the high-performance memory access loop. It is worth mentioning that **the cache architecture is interleaved between processor and memory**  chips to improve performance. In dRedBox, we aim to disaggregate memory by placing modules on a dedicated memory card and interface them via the system interconnect to the RMA of each micro-server. One of the biggest challenges, is to develop the appropriate memory interface and logic for the transmission over the optical network. dReDBox aims to integrate existing SoC architectures and aims to design and develop a "Virtual Memory DIMM" component that can be directly interfaced to a commodity DDR controller. This component will be configured via memory-mapped I/O using a special address range and it will be capable of moving memory data to/from the optical network. Moreover, a local DIMM module will be appropriately mapped and used for system software bootstrapping support. Virtual DIMM software-defined configuration will associate memory address ranges with optical network forwarding information so that remote DIMMs can be reached. Also, on the memory card pool, a different version of the virtual DIMM will be directly interfaced and will be able to access physical modules on the memory card.

Another important challenge that I have to mention is that the dRedBox hardware memory interface design aims to address the distribution of DMA transfer interrupts. In the dReDBox platform, the DMA chipsets that are integrated into microserver SoCs will be used. Each time a DMA transfer is programmed, a list of processor interrupt recipients will be configured at the remote Virtual DIMM. When the transfer is complete, interrupts are to be delivered to the remote processor(s) accordingly. The described inter-tray interrupt mechanism will provide valuable support to the virtualization software and aims to enable integration of peripherals which will be driven by dedicated microservers.

## 3.4 Operating system support for disaggregation

For applications, dRedBox aims to provide a commodity virtual machine execution, without compromising performance. But, in order to run the currently available virtual machines unmodified on the disaggregated platform, there are some important challenges that should be addressed at the OS and hypervisor layer.

The dRedBox hypervisor will be based on KVM(5), a kernel module that enables a standard Linux Operating System to execute one or more virtual machines. Evidently, an instance of KVM will need to run on each microserver platform taking advantage of the locally available memory. Unlike the current server architecture case, the host system on each dReDBox microserver may not be able to detect all available platform components using the BIOS. In fact, the BIOS on each microserver may only provide locally attached component information. Therefore, it is crucial that during bootstrap, the host system should communicate with the orchestration tools to get information.

Immediately prior to a virtual machine deployment, the hypervisor will interact with the dReDBox orchestration tools, asking to reserve resources and set up the appropriate network state for reachability among the pooled resources involved. We will also explore advanced OS and virtualization techniques for dynamic disaggregated memory allocation at OS level. Beyond memory modules, other peripherals are intended to be disaggregated and physically attached to dedicated dReDBox microservers. Such dedicated machines will be connected to peripherals through a given PCIe switch. According to this approach, peripherals are aimed to be made available to virtual machines through direct assignment, or remote para-virtualization (6). The former is aimed to be available for VMs running on the same server where peripherals are interconnected and will leverage the current support from the KVM Hypervisor (16).

## 3.5 Resource allocation

The dRedBox disaggregated platform needs orchestration support that is currently unavailable by state-of-the-art data center resource management tools. The new challenges that this architecture introduces and are not yet addressed by any other platform are:

- a switching network that requires forwarding information that is capable of interconnecting any combinations of the platform's components,

- the need for distribution of the globally accessible physical memory address space located throughout the data center, and

- a novel per component IPMIv2 (3) control.

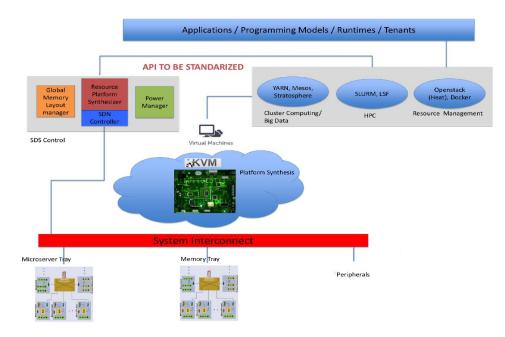

In other words, the dRedBox project approach aims to develop a new orchestration tool layer that aims to:

- implement dynamic platform synthesis by analyzing the physical hardware resources and software performance requirement in order to allocate components and set appropriate forwarding information to interconnect them,

- maintain a consistent distribution of physical memory address space and accordingly provide support to running hypervisors for memory segmentation and ballooning (7), and

- taking advantage of the component level usage information and IPMIv2 control to significantly decrease the required power budget.

This resource allocation and orchestration layer is to be integrated via a standardized API with resource management tools like OpenStack. That way, virtual machine deployment steps will be extended to include a resource scheduling and a platform synthesis step, which aims to reserve the required hardware and configure the platform interconnect in a power-budget conscious manner. The following Figure 5 depicts the target dReDBox platform, featuring orchestration tools and relevant component interactions.

Figure 4: Resource Allocation and Orchestration in dReDBox

## 3.6 And now what?

We can see now that the dReDBox project and architecture vision is to disaggregate computing resources at the lowest possible level, which would result in a datacenter box that is fully configurable and can adapt to any targeted applications profile. For example, if applications are highly parallel and CPU intensive, more cores can be accommodated rather than memory, whereas when applications are I/O intensive, cores can be traded off for memory, disks and network media. As we said before dReDBox will also deliver a vertically integrated working prototype, featuring integration of hardware, system software derivatives and pilot applications porting on the embodiment of the dReDBox architecture.

So as the working prototypes are under construction it is my job to do the preliminary work and that is to find a platform capable of emulating and hosting at least a microservercard of the envisioned dRedBox database. In the next chapter, I will provide all the steps that I followed to accomplish this task as well as all the drawbacks, stepbacks and obstacles that I have encountered along the way. But, as I mentioned in the introduction, the fastest way to test hardware is through virtual platform testing. So this is where my role in the development of the dRedBox project comes into play and I hope that it will come in handy after its completion.

## 4 Emulation platform implementation

As I said in the introduction, the best way to test a new embedded hardware architecture before having an initial prototype platform is by using virtual platforms and for that, we decided that the Imperas platform was the way to go. The reasons for this decision can be found in the appropriate sections of the Introduction 1.2.2 and 1.2.3. However, the work that followed this decision will be described thoroughly in the following sections. But first, let us talk about the idea and how we envisioned this virtual platform emulation design.

My work began as the quest of finding the best emulation platform to better suit our needs. This came up due to a number of reasons apart from the benefits provided by Imperas. I mentioned earlier that the use of virtual platforms is the way to go as regards of system design and evaluation. We needed to come up with an idea of how to implement our vision into reality and for that we needed a good platform to work on. After quite some research and thinking ahead, we decided what we needed to 'create' in order to make the first ever design of our platform.

For starters, we needed a baseline. So, we thought that the best way to start was to create, with the minimum compromises, a platform that consists of a Microserver Card (SoC,local Memory Module, Ethernet device, Virtio Block device e.t.c.), an Interconnect(possibly not optical but with configurable timings) and a version of the Universal Remote Memory DRAM module. Those modules are roughly described in Chapter 3 and more definitions can be found in the dRedBox paper and the references. This initial platform meant to be as close as it could to the original architecture design of the dRedBox Server when it is using only one microserver card. The platform had to be capable of running basic bare metal tests provided by the Imperas platforms to see if it actually runs. It also had to be extremely configurable especially in terms of testing all sorts of interconnection delays, memory sizes(local and remote) and also different versions of processors-SoCs.

The real challenge for us is that at some point we should be able to run advanced data center benchmarks and for that, we settled that we had to make this platform capable of loading an OS. This idea also came as a result of the vision of the dRedBox where apparently every microserver-card will eventually have an instance of a VM running on it. Thus, the idea of the "Simulatorception", as we called it, came to life. It is basically the idea of simulating a working OS on the already simulated platform and run benchmarks on it. It might sound crazy but from our point of view, this was the best and also the most interesting way to address this matter.

In the following sections, I am going to describe everything that went through in the process of creating this platform and provide all the information regarding the decisions I made as well as some of the drawbacks, breakthroughs, successes, and compromises along the way. It is worth noting, that I am going to also add some code samples and many figures in order to help you better dive into the world of the virtual platform emulation and especially this Imperas simulator platform. And for that matter, I think that you will be able to see clearly what my work was all about and that I made a good start. And this is what my thesis was meant for in the first place!

## 4.1 The Imperas platform

Now that we have selected the simulator that we are going to use, it is time to decide a version. Imperas offers a variety of simulator platforms for everyone's needs. We were given the opportunity by Imperas to choose which version we saw fit and provided us with the appropriate academic license as part of their politics about research University teams. In our case, we went all out and acquired the Imperas Multicore Software Development Kit(M\*SDK) (8) which is the top version of the Imperas simulator. The licensing procedure was as simple as sending a request email and from there, my supervisor filled in the necessary verification documents and voila. The procedure of setting up the license server in order to use the simulator will be addressed later, but for now, let us talk about the M\*SDK.

Although we might not need all the capabilities of the M\*SDK we thought that it was better to have the full version than to find later on that we lack some needed features. We did that to play safe because at the time I had little knowledge of the Imperas platform and also we didn't know how far we needed to escalate the simulated dRedBox platform design and testing.

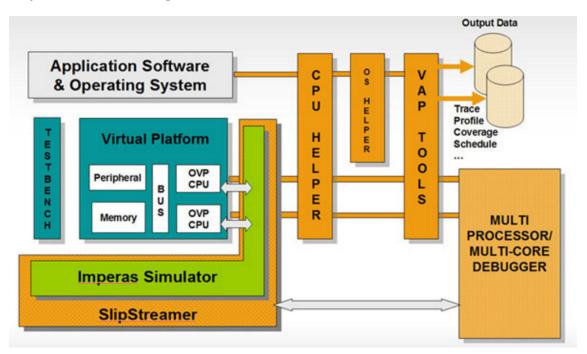

The Imperas Multicore Software Development Kit (M\*SDK) is a complete embedded software development environment that operates using virtual platforms and is specifically designed to handle complex multicore related issues. M\*SDK contains all the capabilities of the M\*DEV (9) product, together with a comprehensive verification, analysis, and profiling (VAP) (8) toolset, plus an advanced 3-dimensional (temporal, spatial and abstraction) debug solution, named 3Debug<sup>TM</sup> (8), for heterogeneous multicore processor, peripheral, and embedded software debug. You can view the general idea of the M\*SDK in Figure 5 and all the information about the VAP tools and the 3Debug can be found in the appropriate references, although, I am not going to say anything more about them here. That is because, besides the fact that we had the M\*SDK platform, I only made use of the M\*DEV features as part of my work. I made only a little use of them because I personally wanted to see what they have to offer. However, I haven't dug deep enough to fully understand their capabilities so I will not address them at all in this thesis review.

Figure 5: The M\*SDK platform concept. More information can be found in reference (8)

#### 4.1.1 Imperas Developer Platforms

M\*SDK is a superset of the M\*DEV platform, which is one of the three developer products of Imperas(C\*DEV, S\*DEV, M\*DEV)(9) and has all its features. Specific details for it can be found in (9) but I am also going to say a few things on that matter, here.

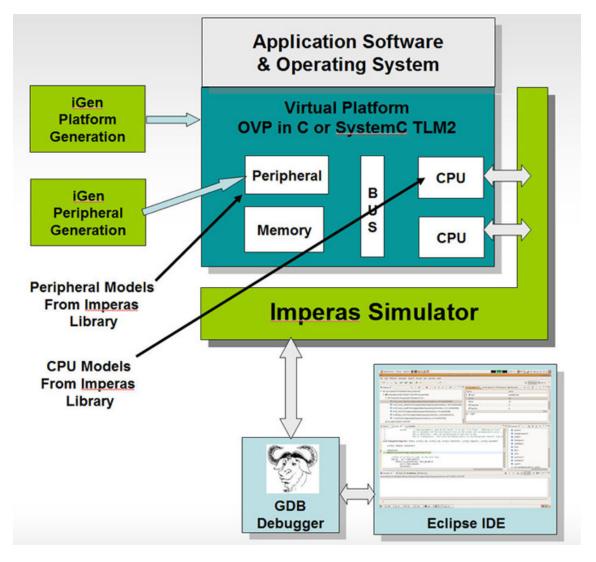

The Imperas Developer products consist of tools, models and infrastructure components critical for the high quality, rapid development, and verification of embedded software, by utilizing virtual platforms. They provide the necessary capabilities to develop platforms, including software simulation capability to execute embedded code on the platforms. In Figure 6 you can view the concept of the M\*DEV platform. Terms like iGen and OVP will be explained later in detail.

Figure 6: The M\*DEV platform concept. More information can be found in reference (9)

To enable the rapid creation of accurate and efficient virtual platforms, all the Developer products contain these 3 key features:

- 1. The Imperas model library which is composed of a wide range of processors, platforms, and peripheral models.

- 2. The iGen Model Generator, which automates the creation of a code framework for new models, and simplifies the laborious and error-prone initial phase of model generation. These models are built on the platform development infrastructure of Open Virtual (OVP).

- 3. The targeted simulation solution for the execution of embedded code, dependent on the processor capability requirements. The simulator can operate with GDB and the Eclipse IDE, as well as the Imperas Multicore Software Design Kit but we are not going to deal with them here.

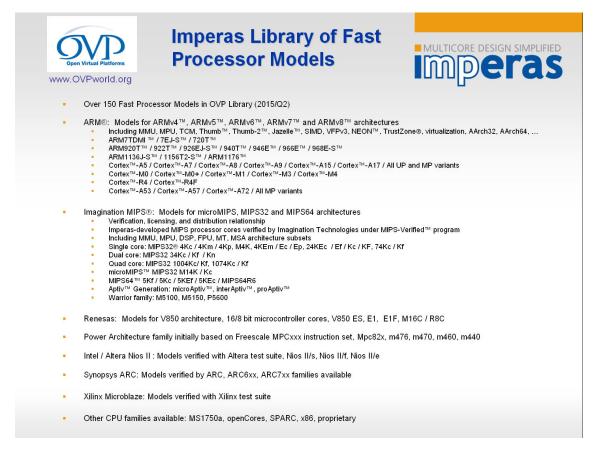

Imperas has developed an extensive model library of processors, peripherals and reference platforms for use in Virtual Platforms. The model library contains more than 160 models of CPU devices and most of them can be viewed in the following Figure 7. I used only

### Figure 7: Imperas model library

processors from the Cortex-A ARMv8 family and more specifically A53, A57 and A72. Almost one hundred common peripheral models may also be downloaded from the library. In addition to the processor and peripheral models, many reference platforms are also included inside this library and they represent well-known industry examples, such as the MIPS Malta. All the models are written in C and all use the OVP APIs thus, enabling execution on OVP compliant simulators such as the Imperas simulator. All models may be downloaded directly from the OVPworld.org website. More information about the Imperas models can be found in (9) and (10).

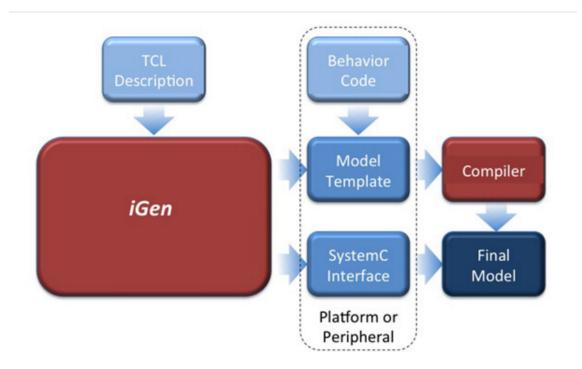

**iGen Model Framework Generator** is a tool to aid in model creation. It takes as input a simple TCL specification that includes device internals such as registers and memories, port information, component descriptors, and other elements. iGen builds three sets of model items, C code model files, user editable templates, and XML descriptions. These include model frameworks with registers, function calls, memory map, and other items, including matching XML information. It ensures that all component parts of the model are well-structured using best practices, and are consistent throughout the files, thus eliminating a common source of errors. In general, iGen presents to the developer a set of function calls and model elements that simply need to be filled in with required behavior, thereby reducing the setup overhead of a new model significantly. It also creates code in the model to provide very efficient runtime tracing and diagnostics. An idea of how it works is shown in the following Figure.

Figure 8: iGEN Model Framework Generator

## 4.1.2 The OVP

It is now time to talk to you about the OVP (10) that I am referring to in all those previous sections. But what is OVP? It is a simulation to develop software on!

As I mentioned earlier, Imperas developed top of the line virtual platforms and modeling technology to enable simulating embedded systems running real application code. These simulations run at speeds of 100s to 1000s of MIPS on typical desktop PCs, are **completely Instruction Accurate** and model the whole system. Imperas decided to open up this technology and OVP is the vehicle to make it public. With OVP you can put together a simulation model of a platform, compile it to an executable, and run bare metal applications, test programs or connect it to your debugger to provide a very efficient fast embedded software development environment.

As I said Imperas has the OVP as a vehicle to open the open virtual platforms technology to the public, and so it has to keep it up to date and also state-of-the-art. A big improvement came in March 2016 when Imperas added six more advanced capabilities to the technologies available to OVP users. I think it is crucial to add them to this thesis as they outline the work that will be described later and also it will help you understand how and why we use OVP.

- The first addition is the **Open Platforms (OP) API** that enables virtual platforms to be defined and controlled with a very powerful C API that allows the modeling of hierarchical systems. It also facilitates the creation of test benches and harnesses to precisely control these hierarchical, often many processor systems.

- The second, that we talked about in the previous section, is the introduction of iGen.

- Third and Fourth are the **eGui** and **iGui** which are graphical debug interfaces to allow GUI-based source code debug of virtual platforms and embedded software. iGui is a very easy to use, very efficient GUI that encapsulates GDB and provides

easy access to embedded software debug. eGui is an advanced debugger based on the very popular Eclipse IDE.

• Last but not least we have the two things that give this platform its great advantage. All OVP (and of course Imperas platform) downloads now include the Instruction Set Simulator (ISS) and Harness. ISS is a program that allows you to run compiled binary embedded software 'elf' files on specific embedded processor variants without the need to develop a virtual platform. ISS comes with the choice of over 170 embedded processor cores. The Harness program enables simulation of virtual platforms without the need to create a test harness or test bench. The Harness is the one that I capitalized on the most and has been a great asset in my working procedure. I used it mostly on all my bare metal tests and builds and also on the final platform where I needed it to set up the OS booting on the simulated platform.

It is worth noting that the OVP initiative is very successful with many users of the technology from hobbyists, universities, commercial companies, and advanced research facilities. One of the best features of Imperas products and of course OVP is that the modeling standards allow for functionality to be included quickly while maintaining model performance and ease of use, reducing a typical multi-month model development project down to just a few weeks. I said before that OVP models can be used in platforms written in C or in platforms written in SystemC TLM2.0. On top of that, I will extend what I said earlier by including that the processor and peripheral models are delivered with a C bus transactional interface that is used in C based OVP platforms, and this interface is used to provide a high-speed TLM 2.0 interface layer allowing the model to be used in a SystemC TLM 2.0 environment with the fastest possible simulation performance.

As always, more information can be found in (10) and also on all Imperas and OVP websites and forums. The specific reference to learning more about the OVP technology is (11). However, for now, it is time to be a little more specific as to how the Imperas-OVP simulator actually works and in the following sections I am going to describe how I "fine-tuned" it to work for me.

#### 4.1.3 The Imperas Simulation System

At the core of all Imperas solutions is a fully functional simulation system that operates at the highest performance of any virtual platform simulator that is available today. The simulator is designed to allow embedded software to be executed on a modeled virtual platform for verification, analysis, debug, profiling and all sorts of other testing purposes. Its purpose within the Developer products is to execute the various models, interface the models to the appropriate selected tools, run software on the processor models, and enable the tasks of OS and driver bring-up, or initial embedded software development.

Imperas achieved something completely innovative in terms of the technology and performance combination. Its models and simulator enable high-performance simulation of systems running embedded software using the production unmodified binaries of the embedded software. The embedded software running cannot tell that it is not running on physical hardware but it is running on a simulated virtual platform model of the actual physical hardware.

I mentioned earlier that all models of the processor and other components are created in C using the OVP APIs. A full range of single, homogeneous multicore and heterogeneous multicore processors are supported by the simulation engine, based on the respective Developer product utilized. The simulator also supports any style of bus topology and can be used in C or C++/SystemC environments. All models in the Imperas-OVP model library can be in used in C or SystemC platforms, and the models are provided with native SystemC TLM2 interfaces.

The simulator utilizes Just-In-Time code morphing to enable particularly highperformance execution speed on standard x86 desktop computers and it also worked extremely well on my 32bit Ubuntu16.04 machine. I will explain the 32bit OS choice in one of the following sections along with all other OS compatibilities. By generating execution code on the fly, and combining this with other Imperas proprietary optimization schemes, the simulation performance that is achieved allows embedded code to be executed, often, faster than real time. Very large numbers of tests may be executed on embedded code within reasonable timescales, allowing product quality to be increased. Furthermore, an extension of this mechanism, the Imperas ToolMorphing (12) technology, allows for a highly streamlined integration of the Imperas software development kit, minimizing the traditional performance overhead and enabling tool usage without impact on software execution accuracy.

In short, **Imperas' breakthrough ToolMorphing technology extends the above mechanism to generate tool and model code together**. ToolMorphing allows users to easily build the models of their hardware platforms and to integrate existing, industrially proven processor models that include tool and simulation capabilities, adding advanced, unique software development features operating at a high-performance level. The entire tool suite is in use at a number of leading customers on real systems, and the embedded software industry has just started to realize the potential benefits and capabilities of virtual platforms! As always, for more extensive information, you can visit the Imperas and OVP websites and specifically reference (12).

## 4.2 The Implementation

A complete introduction has been made about the envisioned dRedBox platform design, the related works and the Imperas-OVP virtual platforms. This introduction provides a better understanding of the steps followed to complete this thesis work. The idea, the motivation, the vision, the breakthroughs and all the new capabilities and possibilities that this project has to offer have all been addressed in the previous chapters and sections. This section is all about the implementation of the idea.

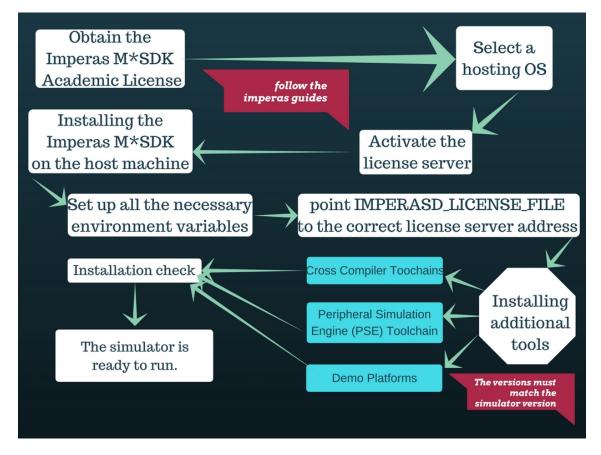

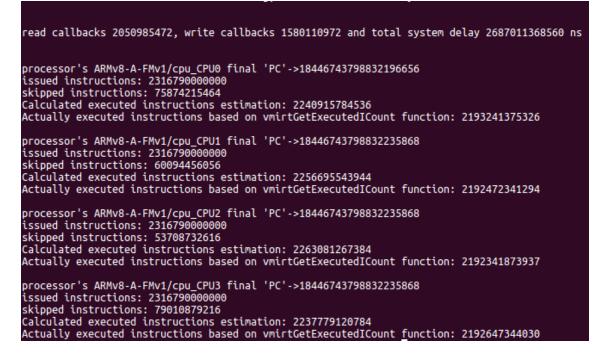

This work was about modeling at least a blade(one microserver card with local and remote memory) of the dRedBox server, combined with all the the necessary components so that it would be capable of both bare metal application testing and also loading a fully functional Operating System. Then, the idea was that we would be able to run all the desired benchmarks on the simulated platform using the simulated OS interface. But, before that, a series of preliminary steps had to be completed in order for this idea to become a reality. These steps will be briefly discussed here. More information can be found in Appendix B appB and in the Imperas installation guides.

This work begun by getting access to an Imperas M\*SDK academic license, provided by the Imperas administrators. After acquiring this license, a license server has to be set up in order to host it. Note that running the Imperas license server within a virtual machine is not permitted. For this work, a floating license was used, described in the Imperas installation guide. On the host side it is crucial that the IMPERASD\_LICENSE\_FILE environment variable should be set to point to the license server.

With the license server up and running, the installation process can be initiated by executing the Imperas M\*SDK self-extracting executable file provided by the Imperas model library. Imperas products are developed to work on x86 hardware, 32-bit or 64-bit. Also, GCC compilers versions on all available OS versions are used by Imperas for generation of host code. After successfully installing Imperas M\*SDK, the Linux Environment variables have to be set accordingly, as instructed by the installation guides appB.

Before we are able to run anything on the simulator, some basic features need to be installed.**It is crucial that the installed tools are for the exact version of the installed simulator that we are using**. First, the platforms require the Cross Compiler Toolchains. These allow a user to quickly start generating application binary code that can be executed on OVP processor models. For each processor that is being used in a platform, the respective cross compiler toolchain is required.Next stop, is installing the Peripheral Simulation Engine (PSE) Toolchain. This is the simulation engine that is used to provide peripheral models in a virtual platform simulation. The installation of the appropriate Cross Compiler Toolchains and Peripheral Simulation Engine (PSE) Toolchain comes first, followed by other packages, for testing and evaluation, that can be used as a guide or as a baseline for many new designs. To verify the installation after an OVPsim or an Imperas install one of the Demos that are downloaded in both installations can be executed.

Figure 9: Preliminary Steps Flowchart

## 4.2.1 Semihosting and the Code Morphing Simulator

In the case of Imperas-OVP simulations, the term **Semihosting** refers to specific behavior that is provided by the Host system rather than the simulation platform or an operating system running on the simulation platform. This is very important because it takes all the unnecessary workload off the simulated platform and executes it on the host machine. **This extra work is moved to the host because it is irrelevant to the simulation and does not affect the simulation results**. So, it removes the complexity of the software and the platform that is not required if we simply wanted to cross-compile and run a bare metal C application on a specific processor variant. This is just the general idea. For mode detailed information visit the Imperas or OVP websites. A **Code Morphing Simulator** operates in two phases to provide the behavior of a target processor executing a sequence of instructions.

- 1. Morphing cross compiled target instructions (for example ARM Cortex-A9, MIPS 1074Kc, V850) to a sequence of native host instructions.

- 2. Executing the sequence of native host instructions to provide the behavior expected of the target.

In 1 we are executing in 'morph time' using the translations specified by the OVP processor model. The code morpher will continue reading instructions and morphing code until it has constructed an entire code block. Once a code block is created, the block is executed. In 2 (run time), for each target instruction behavior, a) the instruction is reread from memory - but this time as a real transaction that will have an effect on the system that the fetch would normally have and b) the native code is executed to create the behavior.

Another part of the Code Morphing Simulator is the SystemC Interface Transaction Types. In SystemC TLM2 interface code is generated for each OVP fast processor model. The component VLNV source library is found at IMPERAS\_HOME/ImperasLib/source, and all the relevant details can be found in both the Imperas-OVP guides and also on their websites. Just note that it is crucial for the SystemC virtual platform to provide both debug and real interface connections.

### 4.2.2 The ARMv8 Foundation Model

In this section, we are going to talk about the use of the ARMv8 Foundation Model (13) as described in the ARM document DUI 0677C. We are going to discuss why I chose this platform as a baseline for my design and what modifications I made along the way. Also, I will mention how I found about this design and how its simplicity and features made me use it.

First of all, I needed a general idea in order to implement a portion of the dRedBox server design on my simulator. As I said before, my main focus was to implement at least one microserver blade, meaning a SoC with some local modules(microserver card), at least one module of local memory, external memory and a configurable interconnect. My approach was made in line with the need that this system must resemble, as close as possible, a dRedBox server blade. Furthermore, it must have all the features so that it can load a fully functional Operating System like for example a Linux OS and also have the ability to interconnect with the host in order to get internet access.

As I searched through the OVP library, I had already tried a whole bunch of demoss and tests and at that point, I had a very good idea of how the simulator actually works. But, I needed a baseline and this came as a boon to me that Imperas-OVP had already made a demo platform that had the basic implementation of an ARMv8 Foundation platform. I needed to do a lot of modifications and also understand all the extra modules and their functionality, but at least I had a starting point! So now I am going to demonstrate the ARMv8 Foundation platform architecture and how its modules are written and implemented inside the Imperas-OVP simulator.

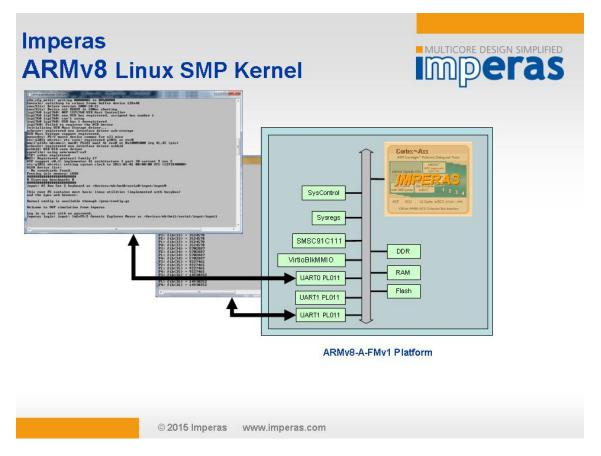

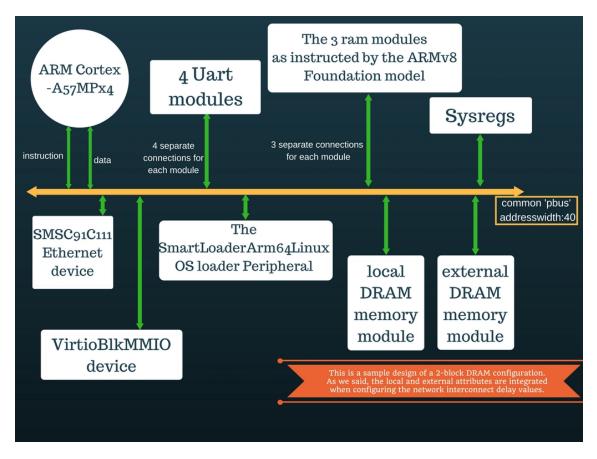

This Demo has the name **ARMv8-A-FMv1** and it can be installed directly from the OVP library. This specific demo has many useful guide files located inside its own folder. These are the **Armv8LinuxNotes.txt** and **README.txt** and they are extremely help-ful for understanding the platform functionality. The key modules of this platform are:

• ARM Cortex-A57MPx4 processor. Imperas also provides the chance that we can use other Cortex-A armv8 processors if we have already installed the aarch64 toolchain that I mentioned in a previous section. For our tests, we used ARM

Cortex-A57MPx4, Cortex-A53MPx4, and Cortex-A72MPx4 with all possible options x1, x2, x3, and x4.

- GIC v2 or v3 (implemented in the processor model). ARM's GIC (General Interrupt Controller) architecture provides an efficient and standardized approach for handling interrupts in multi-core ARM-based systems (21).

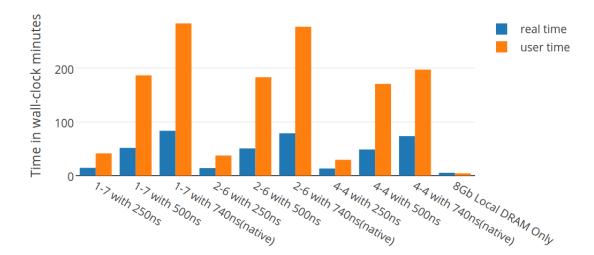

- 8GB DRAM memory. At this point, I need to address that I have decided to allocate only 2 GB of DRAM locally. Inside the design and also by modifying the device tree, I have been able to allocate 6 GB (in other tests 8-16 GB) of **remote memory**, in order to simulate the memory disaggregation. I did that by applying a certain delay on the remote memory interconnect. The delay values of the remote access represent the estimated delay for the actual hardware and have been given to us by our associates!

- We also have some System Registers.

- SMSC LAN91C111. This is the dedicated Ethernet module of my platform. I capitalized on it in order to gain internet access on my final platform but I did all that via the OS not by adding anything to the existing model structure or configuration.

- Four UARTs. I am not going to use all four. To be exact, I only used the UART0 as my operating system's console. Through that, I was able to monitor the boot process of the OS and also use it as my gateway to interact with it.

- Of course, we also have a Virtio block device, which roughly is an I/O virtualization framework for Linux (22). I used this module to load the Ubuntu Linux OS rootfs image on my platform.

- The platform also includes a 'SmartLoaderArm64Linux' pseudo-peripheral that loads the device tree and initrd and inserts a small bit of boot code to initialize GIC and System registers and then jumps to the Linux entry with the proper values in GPR registers r0-r3. This can be used in lieu of having a boot loader such as 'uboot' in your simulation platform.

- All of the above, are interconnected by a 40bit address bus module, that is also implemented inside the common module.op.tcl that the whole platform is created with. The modules are all 'called' from the ImperasLib source model 'pool' but the module.op.tcl file is where they are called and configured!!!

There is a document that describes the details of the platform and its configuration options, memory map, and components in the file:  $MPERAS_HOME/ImperasLib/source/arm.ovpworld.org/module/ARMv8-A-FMv1/1.0/doc/$

Imperas\_Platform\_User\_Guide\_ARMv8-A-FMv1.pdf.