### TECHNICAL UNIVERSITY OF CRETE

DIPLOMA THESIS

# Design and Implementation of an FPGA-Based Convolutional Neural Network Accelerator

Author: Antonios Georgios Pitsis Thesis Committee: Prof. Apostolos Dollas Prof. Dionisios Pnevmatikatos Dr. Christos Kozanitis

A thesis submitted in fulfillment of the requirements for the DIPLOMA of Electrical and Computer Engineering

in the

School of Electrical and Computer Engineering Microprocessor and Hardware Lab

October 10, 2018

### TECHNICAL UNIVERSITY OF CRETE

### Abstract

#### School of Electrical and Computer Engineering

#### DIPLOMA THESIS

### Design and Implementation of an FPGA-Based Convolutional Neural Network Accelerator

by Antonios Georgios Pitsis

In recent years Convolutional Neural Networks (CNNs) have shown extremely growth due to their effectiveness at complex image recognition problems. They are currently adopted to solve an ever greater number of problems, ranging from speech recognition to image segmentation and classification. The continuing increasing amount of processing required by CNNs creates the field for hardware support methods. Moreover, CNN workloads have a streaming nature, well suited to reconfigurable hardware architectures such as FPGAs. The amount of research on the Machine Learning and especially on CNN (implemented on FPGA platforms) within the last 4 years demonstrates the tremendous industrial and academic interest. This study presents a CNN inference accelerator over FPGAs. The network we aim to accelerate was developed by Dr. Tsagatakis in the context of DEDALE project (Horizon 2020 [33]) for astrophysics subject. After carrying out Sensitivity Analysis computational workloads and memory accesses are analyzed, as well as compression methods and algorithmic optimizations to exploit FPGA parallelism. At the level of neurons, optimizations of the convolutional and fully connected layers are explained and compared. At the network level, approximate computing optimization methods are examined limited by not reducing the accuracy of the network. The platforms were used are ZCU102 and QFDB(a custom 4-FPGA platform developed at FORTH). The implemented accelerator was managed to achieve 20x latency speedup, 2.17x throughput speedup and 11.9x energy efficient over GPU NVIDIA-Quadro-K2200 in terms of EuroExa [19] project.

This work is partially supported by the European Union Horizon 2020 program through the EuroExa project.

### Acknowledgements

First of all, I would like to thank my supervisor, Prof. Apostolos Dollas for his trust in my abilities and his valuable guidance during the procedure of this thesis, as well as for the chance he gave me to broaden my horizons beyond my current field of expertise in the domain of Artificial Intelligence.

Furthermore, I would like to thank my co-partner of this project Giannis Kalomoiris, for the collaboration on the successful completion of this project. Moreover, I would like to deeply thank Dr. Gregory Tsagatakis (FORTH), for the excellent collaboration and the confidence he showed us to continue his own work, as well as for his valuable advice and guidance on technical difficulties and especially on Deep Learning. I would also like to express my deepest gratitude to Dr. Christos Kozanitis (FORTH) for his significant contribution and for the excellent cooperation during the course of this thesis. In addition, I would like to thank Angelos Ioannou for his valuable contribution as far as technical issues are concerned with the QFDB.

I would also to thank all the MHL lab. More specifically Dr Anonis Nikitakis for our conversations and valuable knowledge about Machine Learning, Dr Kostas Georgopoulos and Dimitris Theodoropoulos for the time he spent on me to solve technical problems. In particular PHD Candidate Pavlos Malagonakis and Msc Student Vasilis Amourgianos for his valuable input on Vivado Tools and for the time they devoted to me to complete this project. Moreover I would like to thank Petros Toupas for the valuable support and the countless discussions we had for our projects.

Last but not least i would like to express my deepest gratitude to my family and friends for the support during this thesis and especially my friends Argirw Tsilia and Alexia Faidherbe for his valuable support in image design.

> Antonios Georgios Pitsis, Chania 2018

## Contents

| A                | bstra | nct     | i                                      | ii       |

|------------------|-------|---------|----------------------------------------|----------|

| Acknowledgements |       |         |                                        |          |

| Li               | st of | Figur   | es                                     | xi       |

| Li               | st of | Table   | s xi                                   | ii       |

| Li               | st of | Algor   | ithms x                                | v        |

| Li               | st of | Abbro   | eviations xv                           | ii       |

| 1                | Intr  | oduct   | ion                                    | 1        |

|                  | 1.1   | Motiv   | ation                                  | 1        |

|                  | 1.2   | Scient  | ific Contributions                     | 2        |

|                  | 1.3   | Thesis  | o Outline                              | 3        |

| <b>2</b>         | The   | eoretic | al Background                          | <b>5</b> |

|                  | 2.1   | Machi   | ne Learning                            | 6        |

|                  | 2.2   | Convo   | lutional Neural Network                | 6        |

|                  | 2.3   | Struct  | ure of Convolutional Neural Network    | 8        |

|                  |       | 2.3.1   | Convolution Layer                      | 8        |

|                  |       | 2.3.2   | Pooling                                | 9        |

|                  |       | 2.3.3   | Activation Function                    | 9        |

|                  | 2.4   | Typic   | al Architecture of a 1-Dimensional CNN | 4        |

|                  |       | 2.4.1   | Convolutional Layer                    | 4        |

|                  |       | 2.4.2   | Fully-Connected Layer                  | 15       |

|                  |       | 2.4.3   | Final Classification                   | 15       |

|                  |       | 2.4.4   | Pooling Layer                          | 15       |

| 3                | Rel   | ated V  | Vork 1                                 | 7        |

|                  | 3.1   | Googl   | e Brain Project                        | 17       |

|                  |       | 3.1.1   | DistBelief                             | 17       |

|                  |       | 3.1.2   | TensorFlow 1                           | 17       |

|   |      | 3.1.3   | Tensor Processing Unit (TPU)                                 | .8 |

|---|------|---------|--------------------------------------------------------------|----|

|   | 3.2  | GPU a   | approach $\ldots$ $\ldots$ $1$                               | 8  |

|   | 3.3  | The F   | PGA perspective                                              | 9  |

|   |      | 3.3.1   | Training                                                     | 20 |

|   |      | 3.3.2   | Weight Reduction                                             | 20 |

|   |      |         | Computional Reduction                                        | 21 |

|   |      | 3.3.3   | Inference                                                    | 21 |

|   |      |         | Weight Reduction                                             | 21 |

|   |      |         | Re-training approaches                                       | 22 |

|   | 3.4  | Convo   | lutional Neural Networks for Spectroscopic Red-shift Estima- |    |

|   |      | tion or | n Euclid Data                                                | 22 |

|   |      |         | Training and Evaluation                                      | 23 |

|   | 3.5  | Thesis  | Approach                                                     | 24 |

| 4 | Rob  | ustnes  | as analysis of CNN 2                                         | 5  |

|   | 4.1  | MATL    | AB vs TensorFlow                                             | 25 |

|   |      | 4.1.1   | Data types                                                   | 28 |

|   | 4.2  | Memo    | ry Footprint                                                 | 29 |

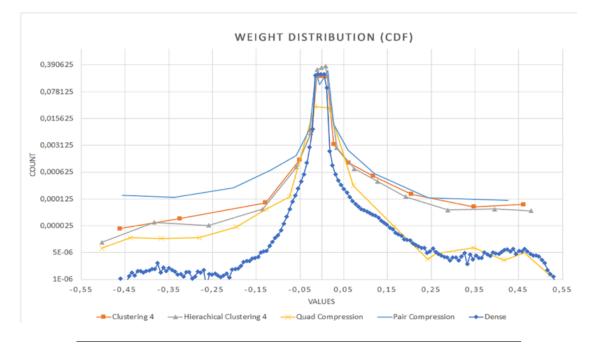

|   | 4.3  | Weight  | t Distribution                                               | 80 |

|   | 4.4  | Prunir  | ng                                                           | 33 |

|   |      | 4.4.1   |                                                              | 84 |

|   |      | 4.4.2   |                                                              | 85 |

|   | 4.5  | Evalua  |                                                              | 86 |

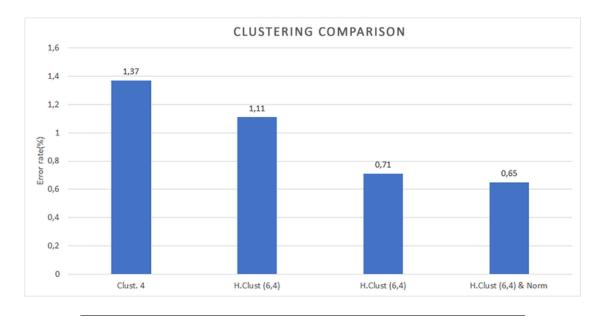

|   | 4.6  | Cluste  | ring                                                         | 86 |

|   |      | 4.6.1   |                                                              | 86 |

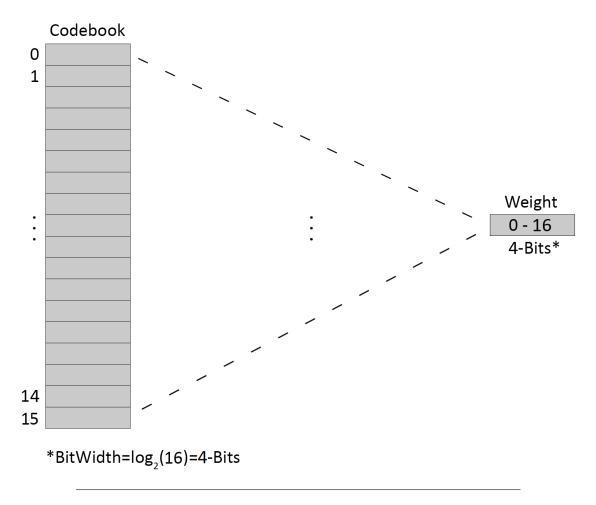

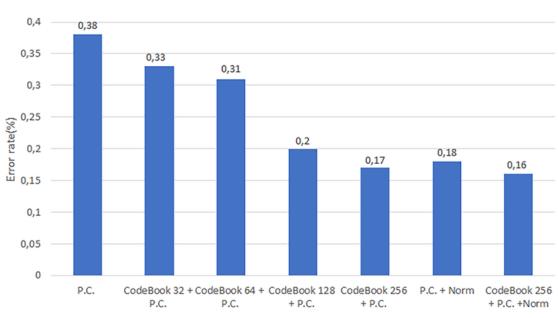

|   |      | 4.6.2   | Quantization with Codebook                                   | 87 |

|   |      | 4.6.3   | Comparison of different Codebooks                            | 88 |

|   |      |         | Stohasting Clustering                                        | 39 |

|   |      | 4.6.4   | Proposed methods for quantization with Codebook 4            | 10 |

|   | 4.7  | Pair-C  | Compression                                                  | 2  |

|   |      | 4.7.1   | Proposed Methods and Pair-Compression                        | 13 |

|   | 4.8  | Quad-   | Compression                                                  | 4  |

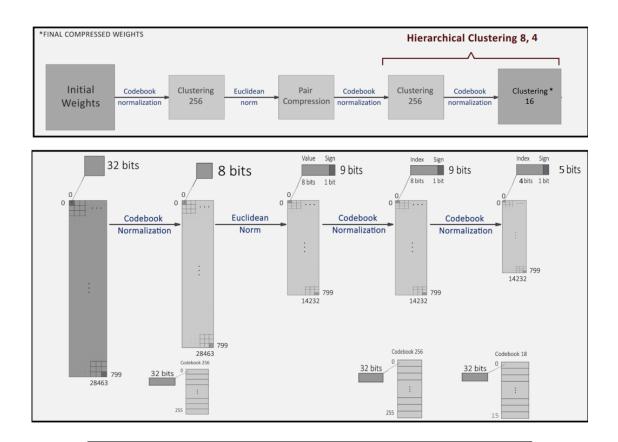

|   | 4.9  | Pair C  | Compression and Hierarchical Clustering                      | 15 |

|   | 4.10 | Second  | d Level Codebook (SLC)                                       | 18 |

|   |      |         |                                                              | 19 |

|   |      |         |                                                              | 50 |

|   |      |         |                                                              | 50 |

|   |      |         | Golden Ratio                                                 | 51 |

|   |      |         | Lossless Method                                                | 52 |

|---|------|---------|----------------------------------------------------------------|----|

|   | 4.11 | SLC c   | comparison with Huffman                                        | 55 |

|   | 4.12 | SLC, I  | Hierarchical Clustering and Pair Compression                   | 57 |

|   | 4.13 | Propo   | sed methods comparison with Binarized Approach $\ldots$ .      | 59 |

| 5 | FP(  | FA Im   | plementation                                                   | 61 |

| 0 | 5.1  |         | Used                                                           | 61 |

|   | 0.1  | 5.1.1   | Vivado HLS                                                     | 61 |

|   |      | 0.1.1   | Synthesis Report in Vivado HLS                                 |    |

|   |      |         | Optimizations in Vivado HLS                                    | 62 |

|   |      | 5.1.2   | Vivado IDE                                                     | 63 |

|   |      | 5.1.3   | Vivado SDK                                                     | 64 |

|   | 5.2  | FPGA    | A platforms                                                    | 64 |

|   |      | 5.2.1   | Xilinx Zynq UltraScale+ MPSoC ZCU102                           | 64 |

|   |      | 5.2.2   | QFDB                                                           | 65 |

|   | 5.3  | Botto   | m-up Strategy                                                  | 65 |

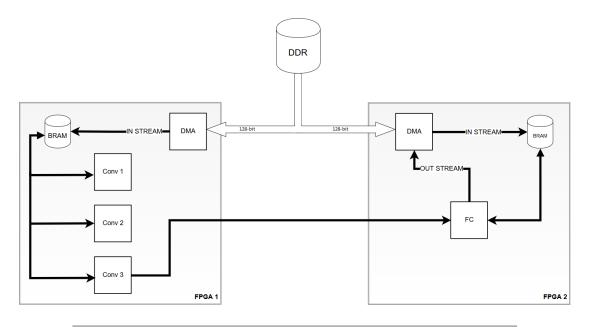

|   |      | 5.3.1   | Two Stage Architecture                                         | 66 |

|   | 5.4  | First A | Approach                                                       | 66 |

|   |      | 5.4.1   | Memory and $I/0$                                               | 66 |

|   |      | 5.4.2   | Transference to HLS                                            | 67 |

|   |      | 5.4.3   | Convolution (1-D) $\ldots$                                     | 67 |

|   |      |         | Array Partitioning                                             | 68 |

|   |      |         | Pipeline                                                       | 68 |

|   |      | 5.4.4   | Convolution (2-D)                                              | 69 |

|   |      |         | Array Partitioning                                             | 69 |

|   |      |         | Pipeline                                                       | 69 |

|   |      | 5.4.5   | Fully Connected                                                | 70 |

|   |      |         | Pipeline                                                       | 70 |

|   | 5.5  | A bett  | ter Approach                                                   | 71 |

|   |      | 5.5.1   | Larger Streaming Buses                                         | 71 |

|   |      | 5.5.2   | Multiple DMAs                                                  | 72 |

|   |      |         | DDR Bandwidth                                                  | 72 |

|   |      | 5.5.3   | Convolution (1-D) and Convolution (2-D) $\ldots \ldots \ldots$ | 73 |

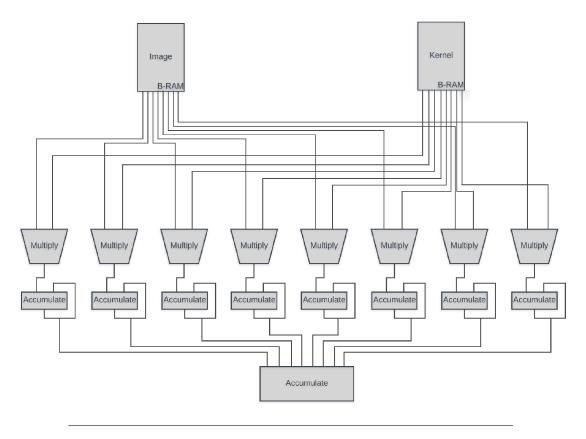

|   |      | 5.5.4   | Fully Connected                                                | 73 |

|   | 5.6  | Archit  | secture v1.0                                                   | 76 |

|   |      | 5.6.1   | Embedding Compressed Weights                                   | 77 |

|   |      | 5.6.2   | Pipelining Convolution Module                                  | 77 |

|   |      |         | Shifted FIFO                                                   | 78 |

|   |       | Task Level Parallelism78               |

|---|-------|----------------------------------------|

|   |       | 5.6.3 Pipelining two Modules           |

|   |       | Convolution Transformations            |

|   |       | Fully Connected Transformations        |

|   |       | 5.6.4 Resource Optimizations           |

|   | 5.7   | Architecture v2.0                      |

|   | 5.8   | Resource Optimizations                 |

|   |       | 5.8.1 Batching                         |

|   | 5.9   | Porting to QFDB                        |

| 6 | Res   | ilts 85                                |

|   | 6.1   | Specification of Compared Platforms 85 |

|   |       | 6.1.1 Intel i7 7700HQ                  |

|   |       | 6.1.2 NVIDIA Quadro K2200              |

|   | 6.2   | Power Consumption                      |

|   | 6.3   | Energy Consumption                     |

|   | 6.4   | Throughput and Latency Speedup         |

|   | 6.5   | Architecture v1.0                      |

|   |       | 6.5.1 ZCU-102                          |

|   |       | 6.5.2 QFDB                             |

|   | 6.6   | Architecture v2.0                      |

|   |       | 6.6.1 ZCU-102                          |

|   |       | 6.6.2 QFDB                             |

|   | 6.7   | Final Performance                      |

| 7 | Cor   | clusions and Future Work 97            |

|   | 7.1   | Conclusions                            |

|   | 7.2   | Future Work                            |

| R | efere | nces 99                                |

# List of Figures

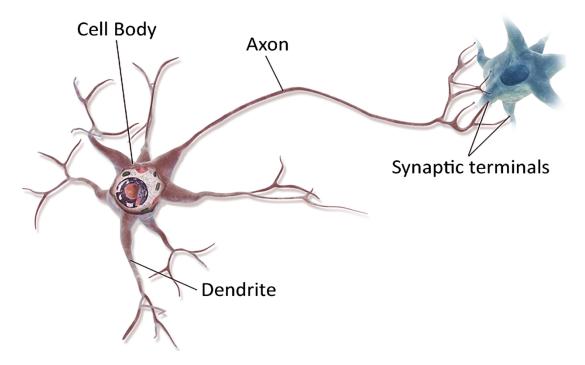

| 2.1  | Standard Structure of Real Neural Network                                                                |

|------|----------------------------------------------------------------------------------------------------------|

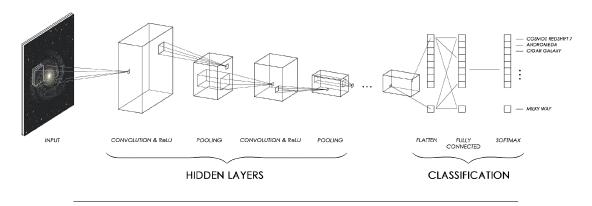

| 2.2  | Architecture of CNN         8                                                                            |

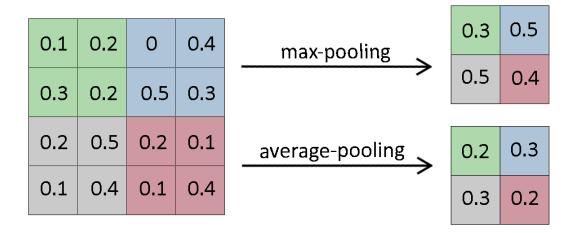

| 2.3  | Pooling Comparison                                                                                       |

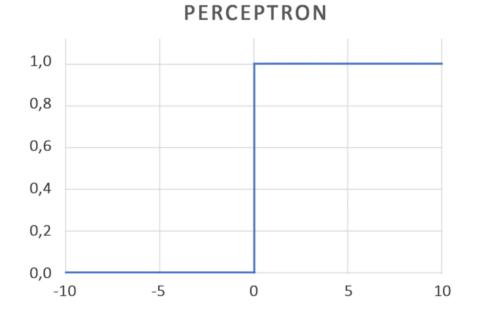

| 2.4  | Perceptron                                                                                               |

| 2.5  | Sigmoid Function                                                                                         |

| 2.6  | tanh(x)                                                                                                  |

| 2.7  | ReLU                                                                                                     |

| 2.8  | Simple 1-Dimensional CNN 16                                                                              |

| 3.1  | Accuracy of Euclede                                                                                      |

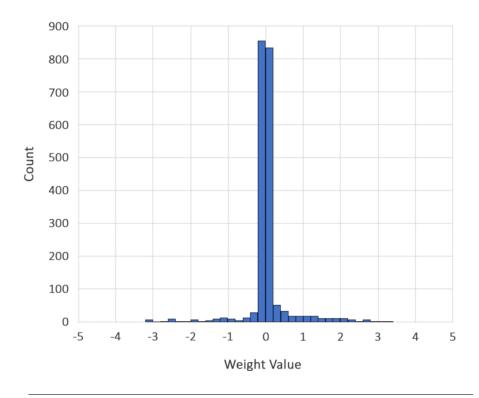

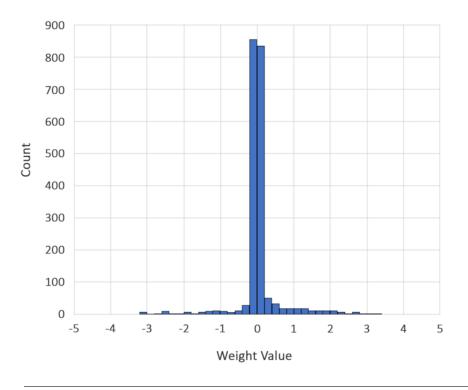

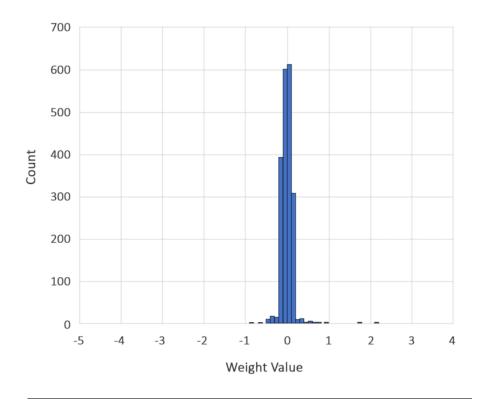

| 4.1  | Weight Distribution of conv1                                                                             |

| 4.2  | Weight Distribution of conv2                                                                             |

| 4.3  | Weight Distribution of conv3 32                                                                          |

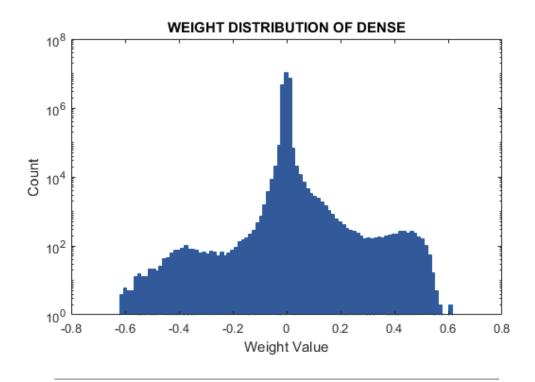

| 4.4  | Weight Distribution of dense                                                                             |

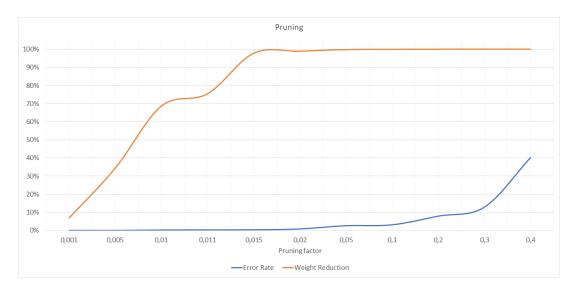

| 4.5  | Pruning Comparison                                                                                       |

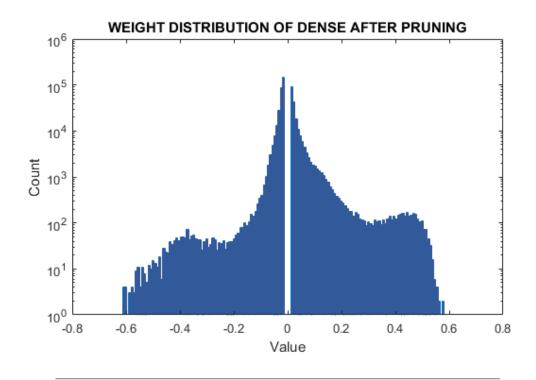

| 4.6  | Weight Distribution after Pruning                                                                        |

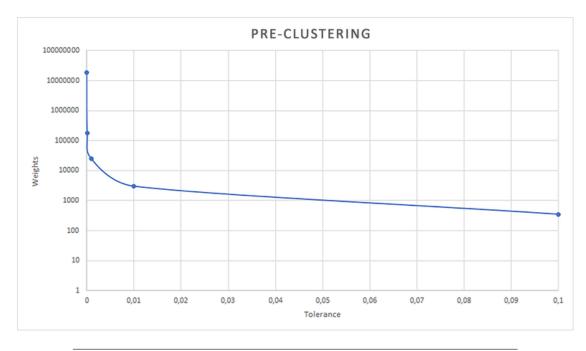

| 4.7  | Pre-Clustering Compression                                                                               |

| 4.8  | Clustering sample                                                                                        |

| 4.9  | Clustering-16 example                                                                                    |

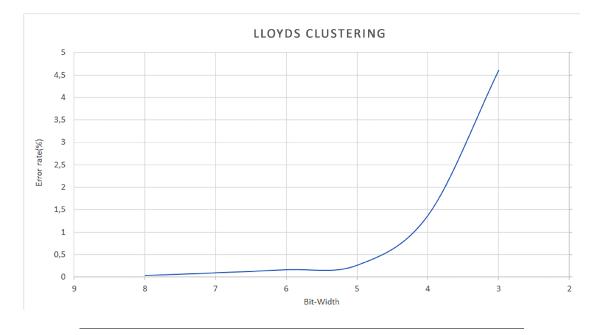

| 4.10 | Lloyds Clustering                                                                                        |

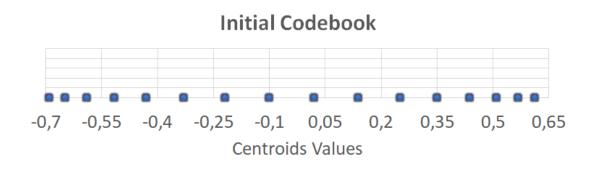

| 4.11 | Inverse Density $\ldots \ldots 41$ |

| 4.12 | Clustering 16                                                                                            |

| 4.13 | Pair Compression example                                                                                 |

| 4.14 | Pair Compression                                                                                         |

| 4.15 | Quad Compression example $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 45$             |

| 4.16 | Comparison of Weight Distribution CDF v.2 $\ldots \ldots \ldots \ldots 46$                               |

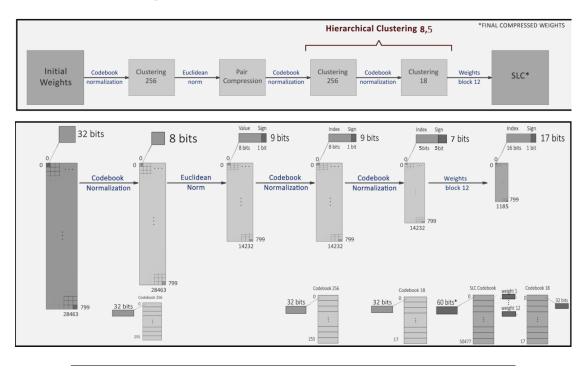

| 4.17 | Hierarchical Clustering And Pair Compression Procedure 46                                                |

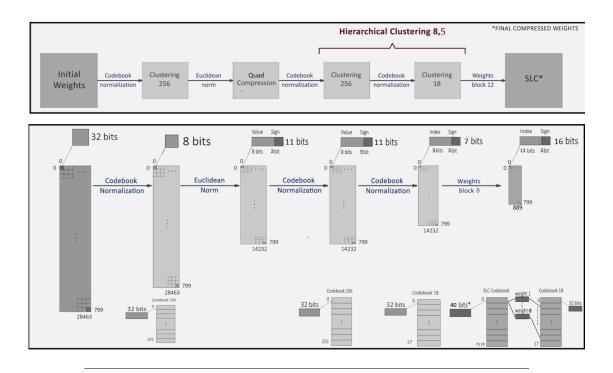

| 4.18 | Hierarchical Clustering And Quad Compression Procedure 47                                                |

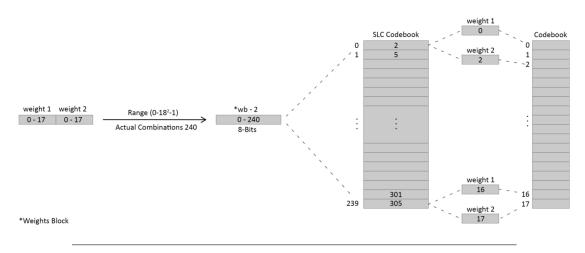

| 4.19 | SLC compression example 49                                                                               |

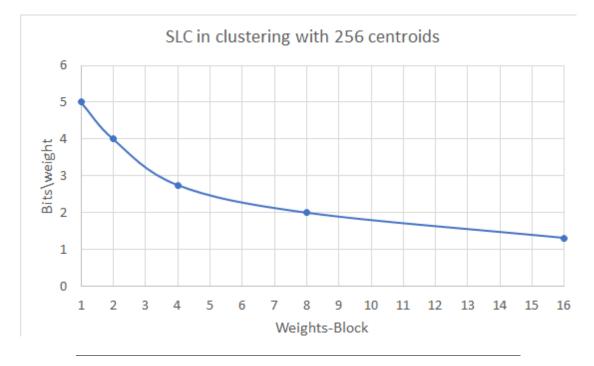

| 4.20 | SLC in Clustering with 256 centroids $\ldots \ldots \ldots \ldots \ldots \ldots \ldots 51$               |

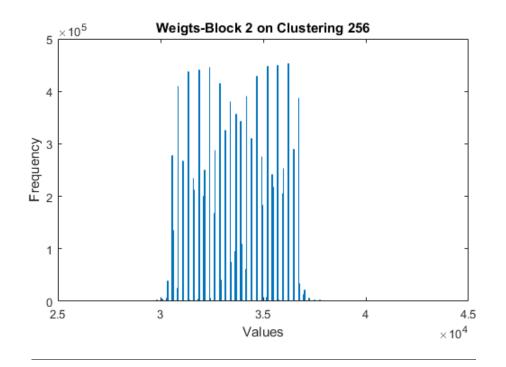

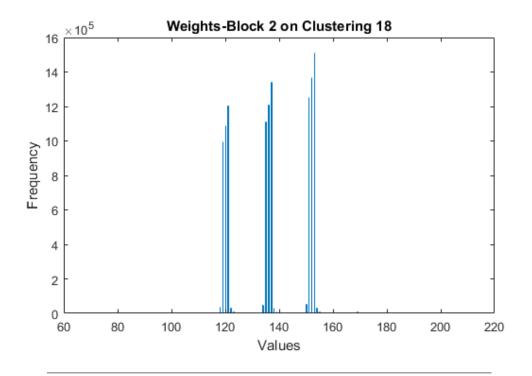

| 4.21 | Weights-Block-2 on Clustering with 256 centroids                                                         |

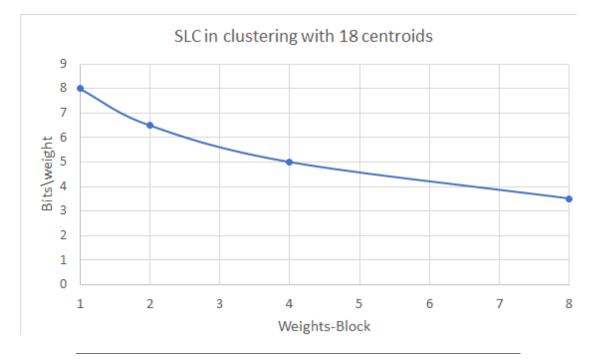

| 4.22 | SLC in Clustering with 18 centroids                             | 53 |

|------|-----------------------------------------------------------------|----|

| 4.23 | Weights-Block-2 on Clustering with 18 centroids                 | 53 |

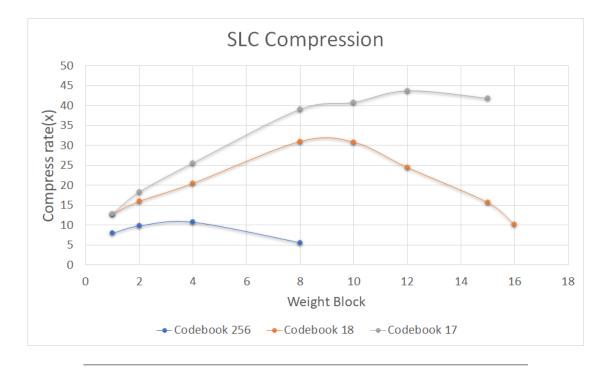

| 4.24 | SLC Performance                                                 | 54 |

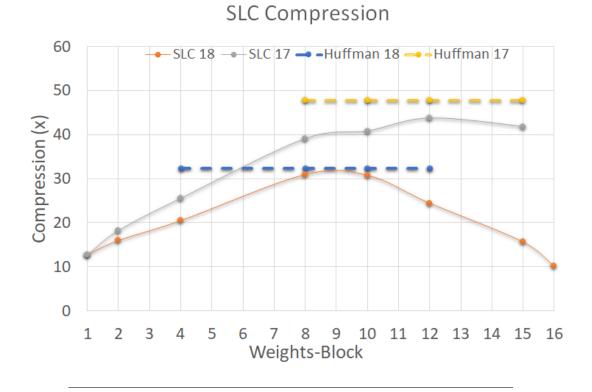

| 4.25 | Comparison of SLC compression on Codebook 18 and 17 versus      |    |

|      | Huffman Coding                                                  | 56 |

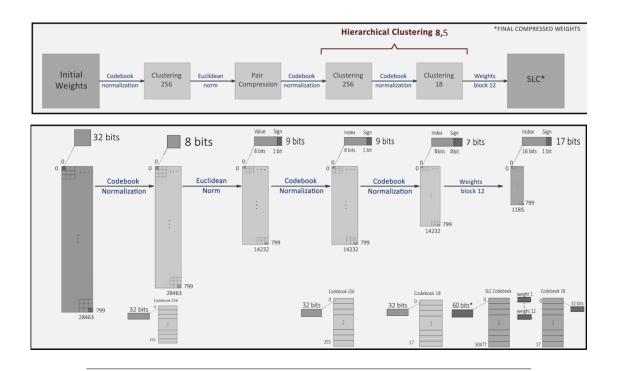

| 4.26 | Compression Flow using Pair Compression and SLC                 | 56 |

| 4.27 | Compression Flow using Pair Compression and SLC                 | 57 |

| 4.28 | Compression Flow using Quad Compression and SLC $\ldots \ldots$ | 58 |

| 5.1  | Datapath of Two-Stage Architecture                              | 66 |

| 5.2  | Datapath of Convolution(1-D)                                    | 68 |

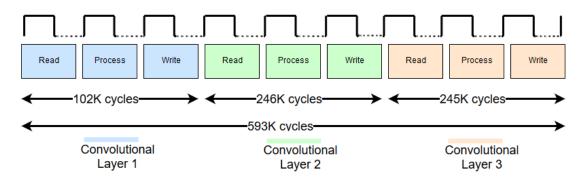

| 5.3  | Convolutional Layers Time-Chart (FA)                            | 69 |

| 5.4  | Fully Connected Module                                          | 70 |

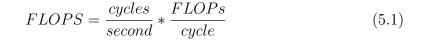

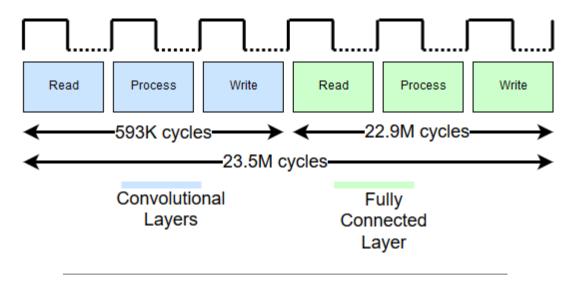

| 5.5  | CNN Time-Chart (FA)                                             | 71 |

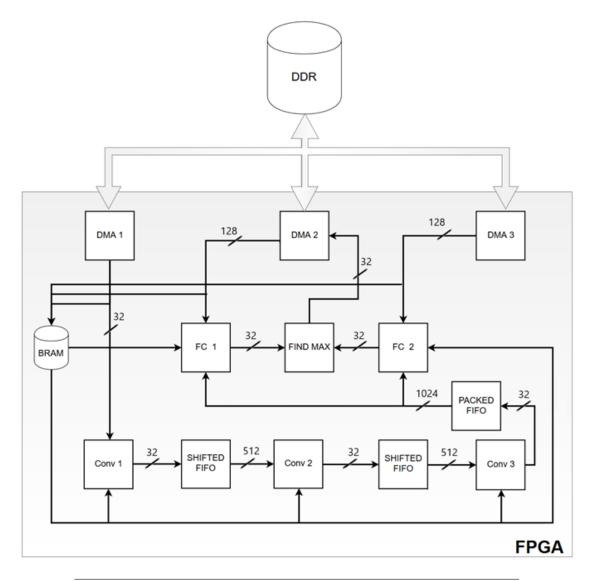

| 5.6  | Datapath of the Architecture v1.0                               | 76 |

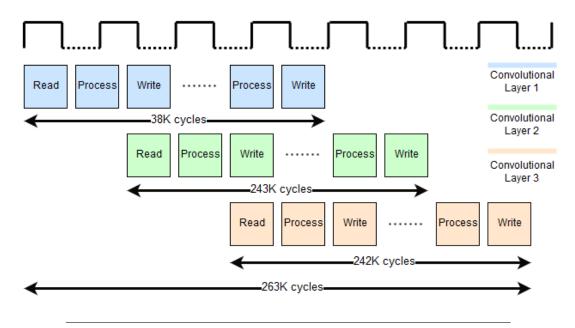

| 5.7  | Convolutional Layers Time-Chart (Arch1.)                        | 77 |

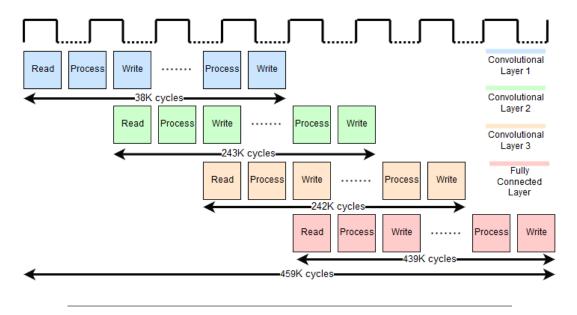

| 5.8  | CNN Time-Chart (Arch1)                                          | 80 |

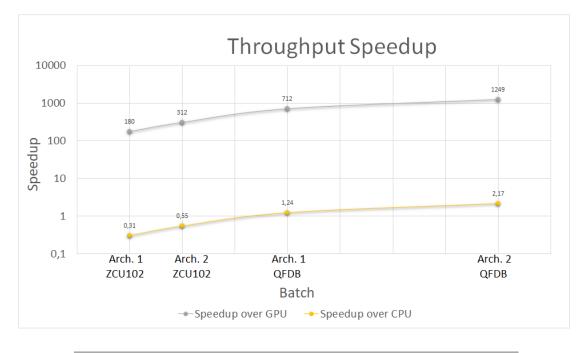

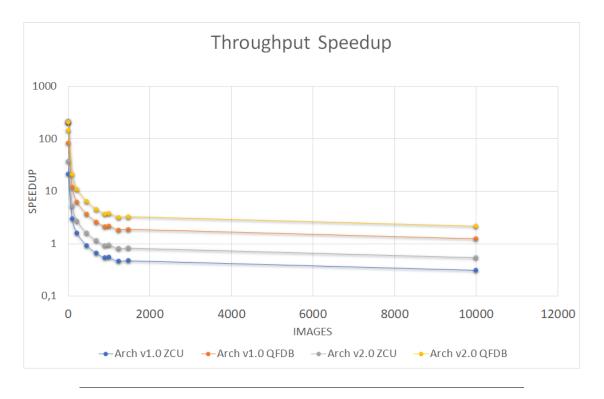

| 6.1  | Throughput Speedup for different batches                        | 93 |

| 6.2  | Throughput Speedup for different Number of Images               | 94 |

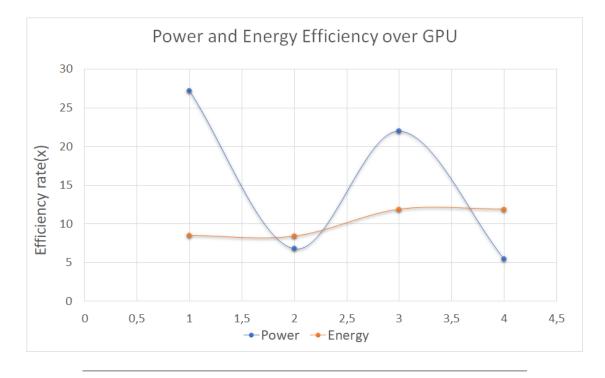

| 6.3  | Power and Energy Efficiency over GPU                            | 94 |

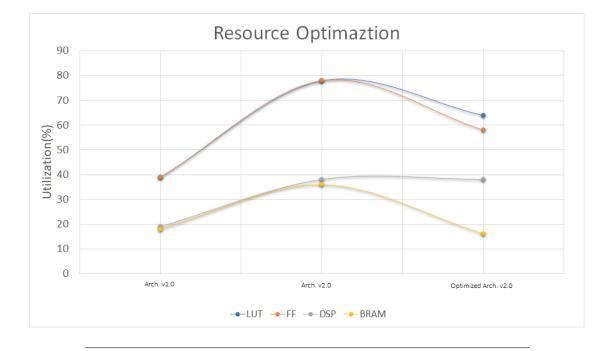

| 6.4  | Utilization after the use of Resource Optimizations             | 95 |

|      |                                                                 |    |

## List of Tables

| 3.1  | Comparison of CPU and GPU training running time                        | 24 |

|------|------------------------------------------------------------------------|----|

| 4.1  | Error rate                                                             | 29 |

| 4.2  | Weights Memory Footprint                                               | 29 |

| 4.3  | Data Stages Memory Footprint                                           | 29 |

| 4.4  | Fixed point formats                                                    | 35 |

| 4.5  | Dynamic Fixed Point                                                    | 35 |

| 4.6  | Pre-Clustering Compression Error                                       | 37 |

| 4.7  | Lloyds Clustering                                                      | 40 |

| 4.8  | Compression Methods                                                    | 45 |

| 4.9  | SLC compression on Codebook 256 for different Weights Block            | 50 |

| 4.10 | SLC compression on Codebook 18 for different Weights Block $\ . \ .$ . | 51 |

| 4.11 | SLC compression on Codebook 17 for different Weights Block $\ . \ .$ . | 54 |

| 4.12 | Comparison of SLC compression on Codebook 18 and 17 with Huff-         |    |

|      | man Coding                                                             | 55 |

| 4.13 | Final Compression Methods                                              | 59 |

| 4.14 | Proposed methods comparison with Binarized Approach $\ldots \ldots$    | 59 |

| 5.1  | ZCU102 Specifications                                                  | 65 |

| 5.2  | First Approach Performance                                             | 71 |

| 5.3  | Memory Bandwidth                                                       | 73 |

| 5.4  | Second Approach Performance                                            | 75 |

| 5.5  | Pipeline Convolutional Layers                                          | 78 |

| 5.6  | Pipeline Convolutional with Fully Connected Layer                      | 82 |

| 5.7  | Architecture v1.0 Performance                                          | 82 |

| 5.8  | Architecture v2.0 Performance                                          | 83 |

| 5.9  | Pipeline Convolutional Layers                                          | 84 |

| 6.1  | Intel i7 7700HQ Specifications                                         | 85 |

| 6.2  | NVIDIA Quadro K2200 Specifications                                     | 86 |

| 6.3  | Architecture v1.0                                                      | 88 |

| 6.4  | Architecture v1.0 comparison with CPU and GPU                          | 88 |

| 6.5  | Speedup over GPU and CPU                                               | 88 |

| 6.6 | 5 Energy and Power Efficiency over GPU and CPU   | 89 |

|-----|--------------------------------------------------|----|

| 6.7 | 7 Architecture v1.0 comparison with CPU and GPU  | 89 |

| 6.8 | 8 Speedup over GPU and CPU                       | 89 |

| 6.9 | D Energy and Power Efficiency over GPU and CPU   | 90 |

| 6.1 | 10 Architecture v2.0                             | 90 |

| 6.1 | 11 Architecture v2.0 comparison with CPU and GPU | 91 |

| 6.1 | 12 Speedup over GPU and CPU                      | 91 |

| 6.1 | 13 Energy and Power Efficiency over GPU and CPU  | 91 |

| 6.1 | 14 Architecture v2.0 comparison with CPU and GPU | 92 |

| 6.1 | 15 Speedup over GPU and CPU                      | 92 |

| 6.1 | 16 Energy and Power Efficiency over GPU and CPU  | 92 |

|     |                                                  |    |

# List of Algorithms

| 1 | Convolution (1-D) $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 26$ |

|---|----------------------------------------------------------------------------------------------|

| 2 | Convolution (2-D) $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 27$        |

| 3 | Fully Connected                                                                              |

| 4 | ReLU                                                                                         |

| 5 | SoftMax                                                                                      |

| 6 | Matrix Multiplication                                                                        |

| 7 | Matrix Multiplication (Opt)                                                                  |

| 8 | Sequential Parallel with MUTEX                                                               |

| 9 | Matrix Multiplication (Opt) 81                                                               |

## List of Abbreviations

| CNN                   | Convolutional Neural Network                                                                                     |

|-----------------------|------------------------------------------------------------------------------------------------------------------|

| $\mathbf{FC}$         | Fully Connected                                                                                                  |

| DNN                   | $\mathbf{D}$ eep $\mathbf{N}$ eural $\mathbf{N}$ etwork                                                          |

| ANN                   | $\mathbf{A}$ rtificial $\mathbf{N}$ eural $\mathbf{N}$ etwork                                                    |

| DP                    | $\mathbf{D}$ eep $\mathbf{L}$ earning                                                                            |

| AI                    | Artificial Intelligence                                                                                          |

| FPGA                  | Field Programmable Gate Array                                                                                    |

| CPU                   | Central Processor Unit                                                                                           |

| $\mathbf{GPU}$        | $\mathbf{G} \mathrm{raphic} \ \mathbf{P} \mathrm{rocessor} \ \mathbf{U} \mathrm{nit}$                            |

| TPU                   | Tensor Processor Unit                                                                                            |

| $\mathbf{ML}$         | $\mathbf{M} achine \ \mathbf{L} earning$                                                                         |

| QFDB                  | $\mathbf{Q}$ uad $\mathbf{F}$ PGA $\mathbf{D}$ aughter $\mathbf{B}$ oard                                         |

| $\operatorname{ReLU}$ | $\mathbf{Re}$ ctified Linear Unit                                                                                |

| HLS                   | $\mathbf{H} igh \ \mathbf{L} evel \ \mathbf{S} ynthesis$                                                         |

| SDK                   | Software Development Kit                                                                                         |

| SLC                   | $\mathbf{S}$ econd $\mathbf{L}$ evel $\mathbf{C}$ odebook                                                        |

| RAM                   | $\mathbf{R} \mathrm{andom}\ \mathbf{A} \mathrm{ccess}\ \mathbf{M} \mathrm{emory}$                                |

| D-RAM                 | $\mathbf{D} \mathrm{ynamic} \ \mathbf{R} \mathrm{andom} \ \mathbf{A} \mathrm{ccess} \ \mathbf{M} \mathrm{emory}$ |

| <b>B-RAM</b>          | Block Random Access Memory                                                                                       |

| DSP                   | $\mathbf{D}$ igital $\mathbf{S}$ ignal $\mathbf{P}$ rocessor                                                     |

| $\mathbf{FF}$         | $\mathbf{F}$ lip $\mathbf{F}$ lops                                                                               |

| LUT                   | $\mathbf{L}ook \ \mathbf{U}p \ \mathbf{T}able$                                                                   |

Dedicated to my family and friends...

### Chapter 1

### Introduction

The exponential growth of data during the last years is increasing, leading to the need for proper management. We always knew it was big in 2010 cracking the zettabyte barrier. Extracting and analyzing these amounts of information makes it difficult or even impossible using conventional software tools and technologies. Digital information, sizes and dimensions, is growing at astonishing rates. For example in 2013, according to the National Security Agency, the Internet is processing 1.8 Petabytes of data per day ("National Security Agency", 2013) [1]. During 2006-2011, digital data has grown 9 times in volume [24]. Moreover, its amount in the world will be estimated to reach 35 trillion gigabytes [25]. More specifically, according to Forbes ([48]) we produce every day globally is 2.5 ExaBytes (quintillion of bytes) according to our current pace. This rapid explosion of digital data brings big opportunities for innovative methods and creates the field to explore ways to extract a high-level understanding of the low-level information given by raw data such as images, video and speech sequences. Among the proposed methods, Convolutional Neural Networks (CNNs) [81] have become the driving force by achieving accuracy even better than humans in many applications related to machine vision (e.g detection [26], classification [38], segmentation [82]) and speech recognition [58].

### 1.1 Motivation

State-of-the-art accuracy results in image , speech , language and many other tasks are being achieved via using convolutional neural networks (CNNs) (e.g. [9], [12], [42], [54], [55], [13]). This outstanding performance comes at the price of a huge computational cost. CNNs require up to 40 GOP/s to classify efficiently a single image [70]. As a result, dedicated hardware is required to accelerate their execution. Graphics Processing Units (GPUs), have been the most widely used platform to implement CNNs as they present the best performance in terms of pure computational throughput, reaching up to 11 TFLOP/s [22]. Nevertheless, in

terms of power consumption, Field-Programmable Gate Array (FPGA) solutions are known to be more energy efficient (vs GPUs).

CNN training is highly compute-intensive, requiring hours, days or even weeks to achieve high accuracy using high-end graphics processing units (GPUs). Hardware acceleration is particularly suitable for inference, as training is typically done once off-line, whereas inference with a is applied repeatedly. As a result, plethora of FPGA-Based CNN accelerators have been proposed mostly for inference. They targeting both High-Performance Computing (HPC) i.e. data-centers [61] and embedded (low-power) applications [4]. Moreover, there is increased emphasis on performing CNN inference embedded-computing context (e.g. mobile applications, aerospace, etc), where low-power and low latency are the most important metrics.

### **1.2** Scientific Contributions

The scientific contribution of this work is focused on two aspects. Firstly several methods have been performed to scale down the memory footprint and computation complexity by reducing the redundancy of CNN models. These methods include pruning, lower floating point, static and dynamic fixed point, clustering algorithms Memory Layout Transformation etc was based on sensitivity analysis implemented in MATLAB. The results of this analysis show us the limitations of how aggressive we can be in each technique, having as a limiting factor to keep low error rate of the network. In typical neural networks, there are millions of parameters which define the model and requires a large amount of data to store them. This problem is especially intense in implementations over FPGA where we have limitations in memory. B-RAM is immensely fast but its size is too small (few MB), on the other hand, D-RAM has significantly bigger size (tens of GB) but limited bandwidth. In our network we have 22.776.272 (64-bit, double precision floating point) weights, meaning 173.77 MB, thus it is essential to reduce its size efficiently to accelerate the network. More specifically the hardware of choice is GPU as they present the best performance in terms of pure computational throughput, using a runtime such as TensorFlow. TensorFlow provides high-level of abstraction features as a general purpose solution suitable for GPUs and CPUs. According to a Google, there was a fear that if the over a billion Android users began to use Google's voice search for just three minutes a day it would require Google to double its number of data centers (using CPUs and GPUs leads to high energy and power demands) [27]. For this reason Google deployed **TPU** [57] targeting its data centers to accelerate the inference phase of neural networks (NNs) having lower power and energy consumption comparing to GPU and CPU solutions.

As a result, dedicated hardware is required to accelerate the execution of CNN applications efficiently leading to high throughput/Watt (or energy) results.

We managed to use FPGAs as CNN accelerators using some of the techniques mentioned above and exploit its parallelism. A pipeline was originally created at each layer separately and then it was expanded between the layers. In order to achieve this, we have to transform the order in which the layers export their results so that the next layers are able to start their process before the previous finish their own. Another challenge was to limit I/O transactions which are the main bottleneck in every FPGA implementation. Several architectures are examined but in order to split efficiently workload in each FPGA, eventually we managed to fit entire CNN in a single FPGA applied significant resource optimization in order to achieve this. Finally, We propose two architectures for a single FPGA (ZCU-102) and for QFDB (Quad FPGA Daughter Board) [19]. The implemented accelerator was managed to achieve 2.5x speedup and 10x energy efficient over GPU NVIDIA-Quadro-K2200. Both results are important when we are targeting satellite-based applications (Euclid satellite).

### 1.3 Thesis Outline

In this section we outline the organization of this thesis.

- Chapter 2: We describe in detail the theoretical background of Machine Learning and especially for CNN.

- Chapter 3: We describe in detail the related work in the field of CNN and more specifically for hardware implementations.

- Chapter 4: We present our Sensitivity Analysis of the given CNN 2.8 in MATLAB. Moreover, several techniques have been performed to limit the memory footprint and computation complexity by reducing the redundancy of the network based on our robustness analysis.

- Chapter 5: We develop two architectures for a single FPGA (ZCU-102) and for QFDB (Quad FPGA).

- Chapter 6: We present and compare both Architectures results in throughput, latency power and energy consumption with GPU (NVIDIA-Quadro-K2200) and CPU(i-7 7700HQ).

• Chapter 7: We conclude this thesis, and we provide directions for future work and possible extensions to our work.

In chapter 3,4 the CNN that we analyze was developed by FORTH researchers (Dr. Tsagatakis and his team). The corresponding section has been obtained from the paper of Dr. Tsagatakis (currently is on submission stage) with his permission (private communication).

### Chapter 2

### **Theoretical Background**

In deep learning, the algorithms we use now are versions of the algorithms we were developing in the 1980s, the 1990s. People were very optimistic about them, but it turns out they didn't work too well."

Geoffrey Hinton

In this Chapter, we describe in detail the theoretical background of Machine Learning and especially for CNN.

The human and several animals have very complex visual recognition systems. We are able to distinguish and classify objects independently. The structure neural network is imitated from the biological brain structure. Each neuron in the network is connected to other neurons through synapses. When a neuron is "fired", sends to the next layer of neurons a chemical substance to change the potential "state" of these neurons. If the potential of a neuron exceeds a threshold, it is activate. Otherwise, it will not be activated. One of the most common research fields in computer science is image recognition. Convolutional Neural Networks (CNNs) neural networks aims to solve problems such as image recognition, by using significant process, such as Gradient Descent [14] and Backpropagation [37]. One of the earliest neural network was inspired in 1943. McCulloch and Pitts (MCP) [77] hve raised an artificial neural model, which was aimed to simulate the process of human neuron response using a computer. It simplifies neurons into two basic processes: linearization of the input signal, and non-linear activation (threshold method). The first use of MCP for machine learning was the perceptron algorithm invented by Rosenblatt in 1958 [65] constituting the foundations of further development in ML.

### 2.1 Machine Learning

Machine learning is a sub-field of computer science that uses techniques with statistical nature to develop in computer systems the ability to progressively learn (gradually improve performance on a specific task) with data, without being programmed in a predetermined manner [41].

The name "machine learning" first was given by Arthur Samuel in 1959 [66]. Machine Learning is the sub-field of Artificial Intelligence that explores and study the construction of algorithms that can "learn" from data and make predictions on them [64]. Firstly was developed and evolved from the fields of computational "learning" theory and pattern recognition in artificial intelligence. Machine learning is employed in a wide range of tasks related to computer. Designing and programming algorithms with these characteristics with high performance are difficult or even impossible. Machine learning promises to approach tasks such as include email filtering, network filtering or various insiders, learning to classify, and computer vision is problems that.

Machine learning is closely related to (and often overlaps with) computational statistics, which also focuses on prediction-making through the use of computers. It has strong ties to mathematical optimization, which delivers methods, theory and application domains to the field. Machine learning is sometimes conflated with data mining [46], where the latter sub-field focuses more on exploratory data analysis and is known as unsupervised learning [8]. Machine learning can also be unsupervised [31] and be used to learn and establish baseline behavior for various tasks and entities and then used to find meaningful disorders.

In data analytics, machine learning is a method used to manage complex models and algorithms that focus to prediction. Many applications in commercial use, known as predictive analytics. These analytical models allow engineers, researchers, and analysts to be able to produce reliable decisions and high-accuracy results and uncover hidden information and structures through learning from historical relationships and trends in the data [45].

### 2.2 Convolutional Neural Network

In machine learning, a convolutional neural network (CNN) is a sub-class of deep, feed-forward artificial neural networks, most commonly applied to analyze visual data.

CNNs use a variation of multi-layer perceptrons designed to require a minimum amount of preprocessing. Convolutional Neural Networks were inspired by biological processes. Thus the connectivity patterns between neurons relied on the study of the organization of the animal visual cortex. Individual cortical neurons respond to stimuli only in a restricted region of the visual field known as the receptive field. The receptive fields of different neurons partially overlap such that they cover the entire visual field.

FIGURE 2.1: Standard Structure of Real Neural Network: URL

Convolutional Neural Networks are very similar to ordinary Neural Networks. They are made up of neurons that have learnable weights and biases. Each neuron receives some inputs, performs a dot product and optionally follows it with a nonlinearity. The whole network still expresses a single differentiable score function: from the raw image pixels on one end to class scores at the other. And they still have a loss function (e.g. SVM/Softmax) on the last (fully-connected) layer.

DNNs can replace a Machine Learnign expert on Feauture Extraction using relatively little pre-processing compared to other image classification algorithms. This means that the network learns the filters that in traditional algorithms were hand-engineered. This independence from prior knowledge and human effort in feature design is a major advantage. They have applications in image and video recognition and natural language processing [13].

### 2.3 Structure of Convolutional Neural Network

A typical Convolutional Neural Network Figure 2.2 consists of millions of neurons where they are organized in several layers. The beginning layer is Convolution layer and the last few layers,1-5 depending on the application, are Fully Connected. The las Fully Connected Layer also named as Classifier. The layers between them are called hidden layers. The main purpose of the convolution layer is to extract image features, then drive them into the hidden layers of computing, and extract the results through the output layer. Layers among hidden layers usually, such as pooling layers (max, average etc), are sub-sampling layers, are partially connected, while the output layers are fully connected. Between hidden layers often there are activation functions that help to keep valuable information for next layers.

FIGURE 2.2: Architecture of CNN

### 2.3.1 Convolution Layer

Convolutional layers apply a convolution operation to the input, passing the result to the next layer. Therefore convolution emulates the response of an individual neuron to visual stimuli [32]. It can be implemented in a variety of ways. There are some hyper-parameters that are used to configure a convolution layer:

- There are some hyper-parameters that are used to compute a convolution

- **Kernel size**(K): Size of filter

- **Stride**(S): How many pixels the kernel window will slide (on each dimension). Normally 1, in conv layers, and 2 in pooling layers.

- **Zero Padding**(pad): Convolution operation can be performed with or without zero padding in three different ways :

- valid returns only those parts of the convolution that are computed without zero-padded edges.

- same returns the same size of the input with appropriate zero padding.

- full returns the full convolution with full zero-padded edges.

- Number of filters(F): Number of patterns and structures, known as "feature maps", that the conv layer will look for.

### 2.3.2 Pooling

A pooling layer is another building block of a CNN. They are used to progressively reduce the size of the representation, but not depth. By having less spatial information you gain computation performance. Also, less spatial information means fewer parameters, so less chance to over-fit the network. Convolutional networks may include local or global pooling layers combining the output of neurons from the previous layer into a single neuron to the next layer [56],[10] The most common approach used in pooling 2.3 is max pooling uses the maximum value of the output of neurons. Another differention of pooling is average , which uses the average value of each neuron at the prior layer and outputs the pooled neuron [11].

FIGURE 2.3: Pooling Comparison

### 2.3.3 Activation Function

In artificial neural networks, the activation function of a node defines the output of that node given an input or set of inputs. A standard computer chip circuit can be seen as a digital network of activation functions that can be "ON" (1) or "OFF" (0), depending on input. This is similar to the behavior of the linear perceptron in neural networks. However, only nonlinear activation functions allow such networks to compute nontrivial problems using only a small number of nodes. In artificial neural networks, this function is also called the transfer function.

Activation functions are used to determine the firing of neurons in a neural network. Given a linear combination of inputs and weights from the previous layer, the activation function controls how we'll process and pass that information on to the next layer.

An ideal activation function is both nonlinear and differentiable. The nonlinear behavior of an activation function allows our neural network to learn nonlinear relationships in the data. Differentiability is important because it allows us to backpropagate the model's error when training to optimize the weights.

#### Perceptron

While 2.1 is the original activation first developed when neural networks were invented, it is no longer used in neural network architectures because it's incompatible with backpropagation. Backpropagation allows us to find the optimal weights for our model using a version of (mainly stochastic) gradient descent. Unfortunately, the derivative of a perceptron activation function cannot be used to update the weights. The step function is not "convex" and thus you cannot find a local min using Gradient Descent[67].

$$f(x) = \begin{cases} 0, & x < 0\\ 1, & x \ge 0 \end{cases}$$

(2.1)

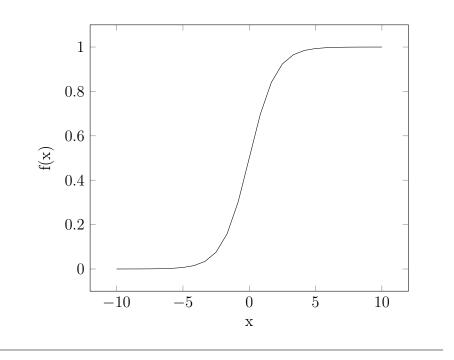

The sigmoid 2.2 function is commonly used when training CNNs, however, it has fallen out of practice to use this activation function in real-world neural networks due to a problem known as the vanishing gradient.

Most commonly sigmoid used is  $2.2\ 2.5$ . There are several sigmoid such as tanh  $2.3.3\ 2.6$  and arctan .

Recall that we included the derivative of the activation function in calculating the "error" term for each layer in the backpropagation algorithm. The maximum value of the derivative for the sigmoid function is 0.25, thus, and you progress backwards each layer in backpropagation you're reducing the size of your "error" by at least 75 at each layer. This ends up limiting our ability to change the weights in layers close to the input layer for deep networks because so many of terms multiplied together in the derivative chain are less than or equal to 0.25.

$$f(x) = \frac{1}{1 + e^{-x}} \tag{2.2}$$

FIGURE 2.4: Perceptron

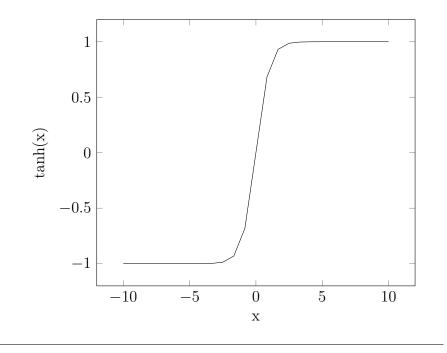

$$anh(\mathrm{x}) = rac{e^x - e^{-x}}{e^x + e^{-x}}$$

(2.3)

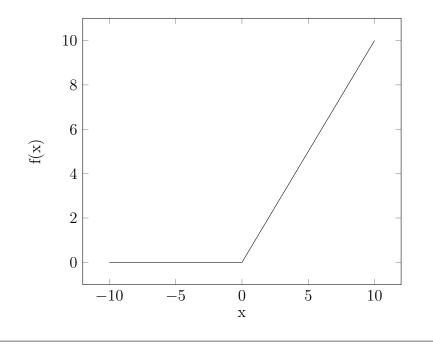

### ReLU (rectified linear unit)

This is 2.4 one of the most popularly used activation functions of 2018. Due to its popularity, a number of variants have been proposed that provide an incremental benefit over standard ReLUs.

$$f(x) = \begin{cases} 0, & x < 0\\ x, & x \ge 0 \end{cases}$$

(2.4)

#### Softmax

The softmax function 4.2 is commonly used as the output activation function for

FIGURE 2.5: Sigmoid Function

multi-class classification because it scales the preceding inputs from a range between 0 and 1 and normalizes the output layer so that the sum of all output neurons is equal to one. As a result, we can consider the softmax function as a categorical probability distribution. This allows you to communicate a degree of confidence in your class predictions.

$$f_i(x) = \frac{e^{x_i}}{\sum_{j=1}^J}$$

(2.5)

FIGURE 2.6: tanh(x)

FIGURE 2.7: ReLU

### 2.4 Typical Architecture of a 1-Dimensional CNN

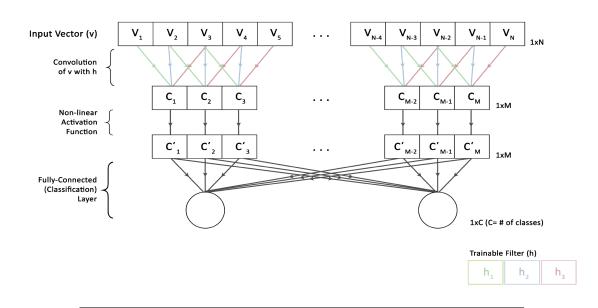

In this section, we analyze the Convolution Neural Network on which we'll study and worked on. The structure, informations, and the document below have been obtained after approval by K. Tsagtakakis. A typical 1-D CNN 2.8 is structured in a sequential manner, layer by layer, using a variety of different layer types. The foundational layer of a CNN is the Convolutional Layer. Given as an input vector of size  $(1 \times N)$  and a trainable filter  $(1 \times K)$ , the convolution operation of the two entities will result in a new output vector with a size  $(1 \times M)$ , where M = N - K + 1. The value of M may vary based on the stride of the operation of convolution, with bigger strides leading to smaller outputs. In the entirety of this thesis, we assume the generic case of a stride value equal to 1. The trainable parameters of the network (incorporated in the filter), are initialized randomly [6] and, therefore, are totally unreliable, but as the training of the network advances, through the process of back-propagation [15], they are essentially optimized and are able to capture interesting features from the given inputs. The parameters (i.e. weights) of a certain kernel are considered to be shared [43], in the aspect that the same weights can be used throughout the convolution of the entirety of the input. This can consequently lead to a drastic decrease in the number of weights, enhancing the ability of the network to generalize and adding to its total robustness against overfitting. To ensure that all different features can be captured in the process, more than one filters can be actually used. More specifically to be able to compose high level features we need to extract more than one feature from each input "pixel".

### 2.4.1 Convolutional Layer

In more difficult problems, using one Convolutional Layer is insufficient, if we want to construct a reliable and more complex solution. A deeper architecture, able to derive more detailed characteristics from the training examples, is a necessity. To cope with this issue, a non-linear function can be interjected between adjacent Convolutional Layers, enabling the network to act as a universal function approximator [34]. Typical choices for the non-linear function (known as activation function) include the logistic (sigmoid) function, the hyperbolic tangent (tanh) and the Rectified Linear Unit (ReLU). The most common choice in CNNs is ReLU (f(x) = max(0,x)) and its variations [30]. Compared to the cases of the sigmoid and hyperbolic tangent functions, the rectifier possesses the advantage that it is easier to compute (as well as its gradient) and is resistant to saturation conditions [56], rendering the training process much faster and less likely to suffer from the problem of vanishing gradients [65].

#### 2.4.2 Fully-Connected Layer

Finally, one or more Fully-Connected Layers are typically introduced as the final layers of the CNN, committed to the task of the supervised classification. A Fully-Connected Layer is a typical layer met in Multilayer Perceptron and as the name implies, all its neuronal nodes are connected with all the neurons of the previous layer leading to a very dense connectivity. Given the fact that the output neurons of the CNN correspond to the unique classes of the selected problem, each of these neurons must have a complete view of the highest-order features extracted by the deepest Convolutional Layer, meaning that they must be necessarily associated with each of these features.

#### 2.4.3 Final Classification

The final classification step is performed using the multiclass generalization of Logistic Regression known as Softmax Regression. Softmax Regression is based on the exploitation of the probabilistic characteristics of the normalized exponential (softmax) function below where x is the input of the Fully-Connected Layer,  $\theta_j$  are the parameters that correspond to a certain class  $w_j$  and W is the total number of the distinct classes related to the problem at hand. It is fairly obvious that the softmax function reflects an estimation of the normalized probability of each class  $w_j$ , to be predicted as the correct class. As deduced from the previous equation, each of these probabilities can take values in the range of [0,1] and obviously, they all add up to the value of 1. This probabilistic approach composes a good reason for the transformation of the examined problem to a classification task, rendering possible to quantify the level of confidence for each estimation and providing a clearer view on what has been misconstrued in the case of mis-classification.

### 2.4.4 Pooling Layer

The use of Pooling Layers has been excluded from the pipeline, given the fact that pooling is considered, among others, a great method of rendering the network invariant to small changes of the initial input. This is a very important property in image classification, but in our case, these translations of the original rest-frame SEDs, almost define the different redshifted states. By using pooling, we suppress these transformations, "crippling" the network's ability to identify each different redshift.

FIGURE 2.8: Simple 1-Dimensional CNN: The input vector v is convolved with a trainable filter h (with a stride equal to 1), resulting in an output vector of size M = N - 2. Subsequently, a non-linear transfer function (typically ReLU) is applied element-wise on the output vector preserving its original size. Finally, a fully-connected, supervised layer is used for the task of classification. The number of the output neurons(C) is equal to the number of the distinct classes

of the formulated problem (800 classes in our case).

# Chapter 3

# **Related Work**

## 3.1 Google Brain Project

TensorFlow is an open-source software library for data-flow programming across a range of tasks. It is an extended math library, developed specifically for machine learning applications such as Deep Neural Networks.[49] It is developed and used for both production and research at Google Labs, often extended its closed-source predecessor, DistBelief. TensorFlow was initially inspired and developed by the Google Brain team for internal Google use. It was released under the Apache 2.0 open source license on November 9, 2015, [73].

### 3.1.1 DistBelief

During 2011, Google Brain built DistBelief as a machine learning system based on Deep Learning neural networks. It has shown rapid growth across different Alphabet companies in both commercial and research applications. Google hired multiple computer scientists, including Jeff Dean, to simplify and reconstruct the base of DistBelief into a faster, more reliable and robust application library, which became TensorFlow. In 2009, Google Brain team, led by Geoffrey Hinton, had developed generalized back-propagation and other important improvements which allowed generation of neural networks to grow and achieve higher performance i.e. a significant 25% reduction in the error rate in speech recognition.

#### 3.1.2 TensorFlow

TensorFlow [75] was originally a major project developed by researchers and engineers working on the Google Brain Team. They collaborate with Google's Machine Intelligence research organization for the purpose of conducting machine learning and deep neural networks research. The results of this project was applicable to a number of other domains, as well, says Google. TensorFlow is Google Brain's second-generation system. Version 1.0.0 was released on 2017 [74], while the reference implementation is able to run on single devices. Moreover, TensorFlow can run on multiple CPUs and GPUs (with optional CUDA extensions for generalpurpose computing on graphics processing units). Its flexible architecture allows deployment of computation across a variety of systems (CPUs, GPUs, TPUs). TensorFlow computations could be expressed as stateful data flow graphs. The name TensorFlow derives from the operations that such neural networks perform on multidimensional data arrays. These arrays are referred to as "tensors". In June 2016, Dean stated that 1,500 repositories on GitHub mentioned TensorFlow, of which only 5 were from Google.

### 3.1.3 Tensor Processing Unit (TPU)

In May 2016, Google announced its Tensor processing unit (TPU), an applicationspecific integrated circuit (ASIC) developed specifically for machine learning and optimized for the use of TensorFlow. TPU is a programmable AI accelerator designed to provide high throughput of low-precision arithmetic (e.g., 8-bit), and oriented toward inference or running models rather than training them. Google announced, that they had been running TPUs inside their data centers for more than a year leading to 30x-80x higher TOPS/Watt compared to contemporary CPU and GPU [57]. Afterwards, it mentioned that they were able to deliver an order of magnitude better "optimized" performance per watt for machine learning.[39]

In May 2017, Google announced the evolution of the first generation, as well as the availability of the TPUs in Google Compute Engine [36]. The secondgeneration TPUs deliver up to 180 teraflops of performance, and when organized into clusters of 64 TPUs, provide up to 11.5 petaflops. In February 2018, Google announced that they were developed TPUs to be available in beta on the Google Cloud Platform.

### 3.2 GPU approach

Deep learning frameworks allow researchers to develop and explore Convolutional Neural Networks (CNNs) and other Deep Neural Networks (DNNs), while delivering high throughput for both research and industrial deployment. The NVIDIA Deep Learning SDK accelerates deep learning frameworks such as Caffe, Tensor-Flow, Theano and Torch as well as many other machine learning applications. Neural Network applications run faster on GPUs and scale across multiple GPUs within a single node. To use the frameworks with GPUs for Convolutional Neural Network training and inference processes, NVIDIA provides toolbox and libraries such as, cuDNN and TensorRT respectively. cuDNN and TensorRT provide highly tuned implementations for standard operations in Deep Learning such as convolution, pooling, normalization, and activation functions.

## 3.3 The FPGA perspective

In recent years, modern Convolutional Neural Networks were being over-developed, but the biggest challenge was getting them to work efficiently. That meant that accuracy, speed during training and energy efficiency were the top priorities. Community mainly focuses on reducing the operands on training and inference. Orthogonal and complementary techniques for reducing redundancies like weight compression, pruning techniques [71] and compact architectures [51] are impressively efficient and they were proposed in the past years.

Until recently, the use of low-precision networks from fixed-point, lower floating points format to binary, in the extreme case, was believed to be highly destructive to the network performance [53] during training and inference procedure. Contrary by showing that good accuracy performance could be achieved (in training) even if a network was binarized to +-1 [16]. This was implemented using Expectation Back Propagation (EBP), a variational Bayesian approach, which infers networks with bi-Binarized Neural Networks: Training Neural Networks with Weights and Activations. Constrained to +-1 binary weights and neurons by updating the posterior distributions over the weights. These distributions are updated by differentiating their parameters (e.g., mean values, average values etc.) through the back propagation (BP) procedure. Implemented a fully binary network at runtime using a very similar approach to EBP, showing significant results in energy efficiency [72]. The drawback of EBP is that the binarized parameters were only used during the inference procedure.

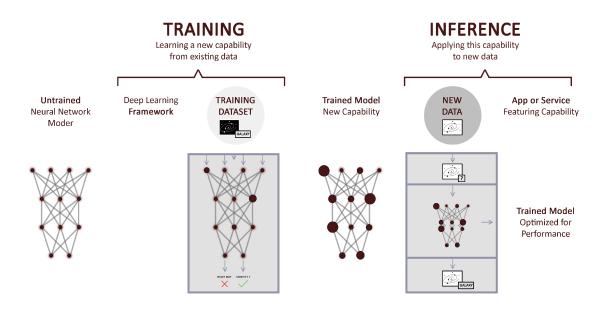

Both procedures are very important and they started hierarchical separated. The first is a prerequisite for the second to start operating. The trend in recent years is to run together.

### **DEEP LEARNING**

### 3.3.1 Training

Training as a process is computationally intensive and requires a lot of resources in hardware implementations. On the other hand, it is an one-time procedure (not always), but it requires a lot of time to get a high-performance behavior (accuracy).

### 3.3.2 Weight Reduction

During the past years methods were proposed to train DNNs with binary weights (BC) and activations (BNN) successively [52] [51]. Initially they add noises to weights and activations as a input of regularization but gradients are calculated with real-valued variables, suggesting that high precision data-types formats accumulation is likely required for Stochastic Gradient Descent optimization. Many researchers have also explored training neural networks directly with fixed-point weights. In 1990 proposed a hardware architecture for on-chip learning with fixedpoint operations. More recently, in [51], the authors train neural networks with 3 different data types (floating-point, fixed-point and dynamic fixed-point formats) demonstrating and compare its results. [23] demonstrate a Convolutional Neural Network training using 16-bit fixed-point weights rounded with stochastic scheme. XNOR-Net [56] has proposed a filter-wise scaling factor for weights trying to improve the performance of fixed point. XNOR-Net implements efficiently convolution operations using XNOR logical units and bit-count operations. However, these high-precision factors are calculated simultaneously during training, which generally aggravates the training effort. In TWN [20] and [68] were proposed two

symmetric thresholds to retain the weights to be ternary-valued: -1,0,+1. They came up with a trade-off between model expressive ability and complexity of the network.

#### **Computional Reduction**

DoReFa-Net [69] quantizes gradients to low-bitwidth floating-point formats with static discrete states in the backward pass. Another quantization of gradient updates to ternary values proposed in [78] to reduce the overhead of gradient synchronization in distributed training. Nevertheless, in DoReFa-Net and TernGrad the weights were stored and updated with single-precision float during training like formal works. Besides, the quantization of batch normalization and its derivative were ignored. Thus, the overall computation graph for the training process is still presented with float(32 bit-width) and more complex with external quantization. Generally, it is impossible to apply DoReFa-Net training in an integer-based hardware directly. Therefore, it could lead to a potential opportunity to explore high-dimensional discrete spaces with discrete gradient descent.

#### 3.3.3 Inference

As far as the part of the inference is concerned, which is a continuous procedure, while the training has been preceded. It is important to be able to achieve high performance (low error-rate), and throughput. Furthermore, an important factor in Hardware implementations is the energy efficiency.

#### Weight Reduction

The data type precision of weights and activations plays a major role in determining the speed accuracy and energy efficiency of any CNN implementations in hardware or software. Plethora of research focuses on how to efficiently replace the 32-bit floating-point data with reduced precision data for CNN inference. Several data-types have been proposed such as [28] representing both weights and activations using low-bit floating point, i.e., single or half. However, it is well known that the fixed-point arithmetic is much efficient than floating-point arithmetic. This state direct most research focuses on fixed-point quantization. Many papers present the impacts of different fixed-point rounding formats on the accuracy of various benchmark network [44]. Thereinafter researchers demonstrate that targeting the minimum required data precision not only varies across different networks but also across different layers of the same network [59]. [17] propose a fixed-point quantization technique to approaching the optimal data precision (range, resolution) for all layers of a network. [60] present a framework Ristretto for fixed-point quantization and re-training of CNN based on [80].

#### **Re-training approaches**

Many other approaches for memory compression of neural networks have been explored. [9] propose a combination of network pruning, weight quantization during training and compression based on Huffman coding to reduce the VGG-16 network size by 49X. In [84], store both 8-bit quantized floating-point weights and 32-bit full precision weights. At runtime, compressed weights or floating point weights are randomly fetched in order to reduce memory bandwidth. The continuous research effort to reduce the memory footprint has led to many interesting demonstrations reaching up to 2-bit weights [23] and even binary weights/activations [53]. [69] demonstrate AlexNet training with 1-bit weights, 2-bit activations and 6-bit gradients. These techniques require additional re-training of the network and can result in sub-optimal accuracy.

# 3.4 Convolutional Neural Networks for Spectroscopic Red-shift Estimation on Euclid Data

The Convolutional Neural Network was developed by FORTH researchers (Dr. Tsagatakis and his team). The following section has been taken from the paper of Dr. Tsagatakis (This is on submission stage) with his permission. [63] Modern astrophysical cosmological researches seek answers to questions like "what is the distribution of dark energy and dark matter in the Universe?" [7], [18]. In this paper, there was an extended study of performing accurate redshift estimation using realistic spectroscopic observations, modeled after Euclid. Redshift estimation is considered to be a regression task, given the fact that a galaxy redshift (z)can be measured as a non-negative real-valued number (with zero corresponding to the rest-frame). Given the specific characteristics of Euclid, we can focus our study on the redshift range of detectable galaxies. Subsequently, we can restrict the precision of our estimations to match the resolution of the spectroscopic instrument, meaning that split the chosen into evenly sized slots equal to Euclid's required resolution. Hence, we can transform the problem at a regression task to a classification task using a set of ordinal classes, with each class corresponding to a different slot, and accordingly, we can utilize a classification model (Convolutional Neural Networks in our case) instead of a regression algorithm.

### Training and Evaluation

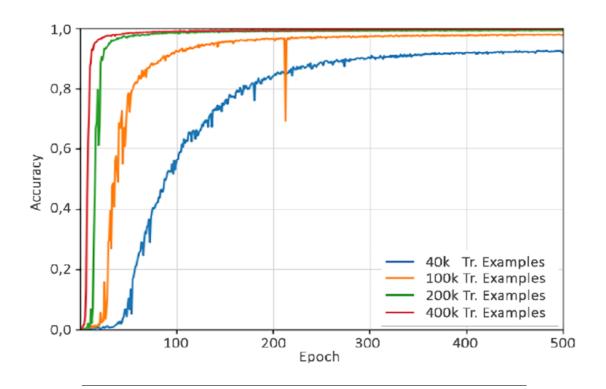

The simulated dataset that was used is modeled after the upcoming Euclid satellite galaxy survey [62]. The training of the network was implemented in the GPU using TensorFlow tools. As far as the Inference part is concerned, there is space for other dedicated hardware like FPGA because energy efficiency is much more important than throughput in aerospace applications. Below are the results of the training 3.1 and the performance 4.16 of the network.

FIGURE 3.1: Accuracy of Euclede: Validation performance of a 3layered network, using larger and more limited in size datasets. In all cases the training accuracy (not depicted here) can asymptotically reach near to 100% accuracy, after enough epochs. Copyrights from []

| Experiment $\#$ | CPU Time (per epoch) | GPU Time (per epoch) |

|-----------------|----------------------|----------------------|

| 14              | 75 sec.              | 11 sec.              |

| 2  4            | 735 sec.             | 107 sec.             |

| 3               | 158 sec. 4           | 20 sec.              |

TABLE 3.1: Comparison of CPU and GPU training running time

Comparison of CPU and GPU training running time, in 3 different benchmark experiments. In the 1st and the 2nd experiments, we utilize 40,000 and 400,000 training observations, of the idealistic case, in a CNN with 1 Convolutional Layer. In the 3rd case, we deploy 40,000 realistic training examples for the training of a CNN with 3 Convolutional Layers.

# 3.5 Thesis Approach

In contrast to prior works, [2], [40], [9] and [21] this thesis comes to develop and propose new ways of compressing information into a specific CNN 3.4 implementation. For the proper use and implementation of clustering algorithms, we highlighted the characteristic problems when implemented on CNN applications and propose techniques to limit them. We also propose new compression methods (Pair compression, Hierarchical Clustering) combining it with existing ones, resulting in a large compression rate(36x) with high accuracy performance (0.7%).

# Chapter 4

# Robustness analysis of CNN

The key to artificial intelligence has always been the representation."

Jeff Hawkins

In this chapter, we intend to analyze the structure of the given Convolution Neural Network [63] 3.4. Afterwards, we aim to model the network in MATLAB [50] and evaluate the results with TensorFlow. The initial CNN has been built and pre-trained in TensorFlow. Therefore starts the inference procedure, where images are fed into the network and this predicts their (target) classes. We built our ToolBox in MATLAB, functions were created for each operation of the network, from importing and formatting image and the filters to the SoftMax layer for the final classification. Thereinafter, we are going to perform a Sensitivity Analysis to explore opportunities for hardware implementation. Finally, several compress and algorithmic optimizations have been studied and tested in order to reduce memory footprint and accelerate the network. Methods, relies on previous studies, such as pruning, different data-types( single floating point, half floating point, fixed point, dynamic-fixed point) and clustering algorithms have been implemented. Finally, we propose new techniques and methods that approach better the problems of already state-of-the-art optimizations.

### 4.1 MATLAB vs TensorFlow

TensorFlow uses high-level of abstraction, hence we manage to transform to MAT-LAB code for lower-level understanding of the network. Next step was to extract and compare the results between MATLAB and TensorFlow. This procedure will show us whether a TensorFlow's Convolutional Neural Network (CNN) can be implemented in MATLAB with our toolbox. In our experiments with TensorFlow, we used double-precision floating point (IEEE standard) and single-precision floating point (IEEE standard) for MATLAB implementation. After running inference procedure for both implementations for 10000 images, the main dataset, and comparing the results we had fully matched top-1 classification.

Below we present the main building blocks of a typical 1-D Convolution Neural Network.

In Algorithm1 we perform an 1-D Convolution with stride 1. This is the first layer of our network. As inputs, it gets a one-dimensional vector( image from the dataset), the kernel which are the pre-trained filters on which the operation of convolution will be based and bias. The output of the layer will be a 2-Dimension vector.

| Alg | orithm 1 Convolution (1-D)                                                          |

|-----|-------------------------------------------------------------------------------------|

| 1:  | procedure CONVOLUTION( <i>image</i> , <i>kernel</i> , <i>bias</i> )                 |

| 2:  | $ImageSize \leftarrow size(image, 1)$ $\triangleright$ Size of $1^{st}$ Dimension   |

| 3:  | $NumOfKernels \leftarrow size(kernel, 2)$ $\triangleright$ Number of kernels        |

| 4:  | $KernelDim1 \leftarrow size(kernel, 1)$ $\triangleright$ Size of $1^{st}$ Dimension |

| 5:  | for $k:=1$ to NumOfKernels do                                                       |

| 6:  | for i:=1 to (ImageSize-KernelSize+1) do                                             |

| 7:  | $Conv(i,k) \leftarrow 0$                                                            |

| 8:  | for $k:=1$ to NumOfKernels do                                                       |

| 9:  | for i:=1 to $(ImageSize-KernelSize+1)$ do                                           |

| 10: | for $j:=1$ to KernelSize do                                                         |

| 11: | $Conv(i,k) \leftarrow Conv(i,k) + image(i+j-1) * kernel(k,j)$                       |

| 12: | $Conv(i,k) \leftarrow Conv(i,k) + bias(k)$                                          |

| 13: | return Conv                                                                         |

In 2 we perform an 2-D Convolution with stride 1. This is the second and third layer of our network. As inputs it gets a two-dimensional vector( $image_{stage}$  from the previous layers), the kernel which are the pre-trained filters on which the operation of convolution will be based and bias. The output of the layer will be a 2-Dimension vector.

| Alg | orithm 2 Convolution (2-D)                                                                  |

|-----|---------------------------------------------------------------------------------------------|

| 1:  | procedure CONVOLUTION( <i>image</i> , <i>kernel</i> , <i>bias</i> )                         |

| 2:  | $ImageSize \leftarrow size(image, 1) \qquad \qquad \triangleright Size of 1^{st} Dimension$ |

| 3:  | $NumOfKernels \leftarrow size(kernel, 3)$ $\triangleright$ Number of kernels                |

| 4:  | $KernelDim1 \leftarrow size(kernel, 1)$ $\triangleright$ Size of $1^{st}$ Dimension         |

| 5:  | $KernelDim2 \leftarrow size(kernel, 2)$ $\triangleright$ Size of $2^{nd}$ Dimension         |

| 6:  | for $k:=1$ to NumOfKernels do                                                               |

| 7:  | $\mathbf{for} \ i{:}{=}1 \ \mathbf{to} \ (ImageSize-KernelSize{+}1) \ \mathbf{do}$          |

| 8:  | $Conv(i,k) \leftarrow 0$                                                                    |

| 9:  | for $k:=1$ to NumOfKernels do                                                               |

| 10: | for i:=1 to (ImageSize-KernelDim2+1) do                                                     |

| 11: | for $p:=1$ to KernelDim2 do                                                                 |

| 12: | for $j:=1$ to KernelDim1 do                                                                 |

| 13: | $Conv(i,k) \gets Conv(i,k) + image(i+j-1,p) * kernel(k,p,j)$                                |

| 14: | $Conv(i,k) \leftarrow Conv(i,k) + bias(k)$                                                  |

| 15: | return Conv                                                                                 |

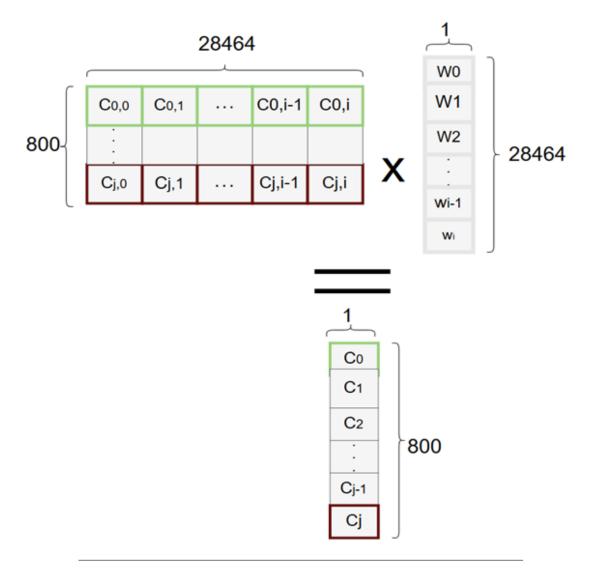

In 3 we perform a Matrix Multiplication. This is the final layer of the network. As inputs it gets a flatten vector (transforming from 2 to 1 Dimension),  $dense_{kernel}$  which are the pre-trained filters and  $dense_{bias}$ . The output of the layer will be a 1-Dimension vector in the size of Number of Classes.

| Algorithm 3 Full              | y Connected                                |                                    |

|-------------------------------|--------------------------------------------|------------------------------------|

| 1: procedure FU               | ULLY CONNECTED $(conv, kernel_{de})$       | $_{ense}, bias)$                   |

| 2: $ConvSize \leftrightarrow$ | -size(conv)                                | $\triangleright$ Size of Conv      |

| 3: NoClasses                  | $\leftarrow size(kernel_{dense}, 1)$       | $\triangleright$ Number of Classes |

| 4: for k:=1 to                | NoClasses do                               |                                    |

| 5: Classes                    | $(k) \leftarrow 0$                         |                                    |

| 6: for k:=1 to                | NoClasses <b>do</b>                        |                                    |

| 7: for $i:=1$                 | $\mathbf{to}$ ConvSize $\mathbf{do}$       |                                    |

| 8: Clas                       | $ses(k) \leftarrow Classes(k) + conv(i) *$ | $kernel_{dense}(k,j)$              |

| 9: Classes                    | $(k) \leftarrow Classes(k) + bias(k)$      |                                    |

| 10: return Con                | iv                                         |                                    |

In 4 we perform ReLU activation function. This layer performed in the output of Convolution Layers.

| Alg  | orithm 4 ReLU                        |                                        |

|------|--------------------------------------|----------------------------------------|

| 1: ] | procedure RELU(conv)                 |                                        |

| 2:   | $ConvSize1 \leftarrow size(conv, 1)$ | $\triangleright$ Size of $1^{st}$ Conv |

| 3:   | $ConvSize2 \leftarrow size(conv, 2)$ | $\triangleright$ Size of $2^{nd}$ Conv |

| 4:   | for $i:=1$ to ConvSize1 do           |                                        |

| 5:   | for k:=1 to ConvSize2 do             |                                        |

| 6:   | if $conv(i,k) < 0$ then              |                                        |

| 7:   | $conv(i,k) \leftarrow 0$             |                                        |

| 8:   | return conv                          |                                        |