## TECHNICAL UNIVERSITY OF CRETE

DIPLOMA THESIS

# Hardware Acceleration of Genome Assembly Algorithms

Author: Georgios GALANOS Committee: Professor Apostolos DOLLAS (Supervisor) Professor Michail ZERVAKIS Dr. Georgios KOTOULAS (HCMR)

*A thesis submitted in fulfillment of the requirements for the diploma of Electrical and Computer Engineering*

in the

School of Electrical and Computer Engineering Microprocessor and Hardware Laboratory

September 13, 2021

## Abstract

#### Georgios GALANOS

#### Hardware Acceleration of Genome Assembly Algorithms

Η συστοιχία γονιδιωμάτων (genome assembly) είναι ένα πεδίο της βιοπληροφοριχής που αναφέρεται στη διαδιχασία λήψης μιχρών μερών γενετιχού υλικού και επανασύνδεσής τους, με διαφορετιχές μεθόδους, προχειμένου να αναδημιουργηθεί η αρχιχή αλληλουχία από την οποία προήλθε το DNA. Δεδομένου ότι τα σύνολα δεδομένων εισόδου των DNA έχουν πολυάριθμο μέγεθος και στις περισσότερες περιπτώσεις αποτελούν πολύ μεγάλο όγχο δεδομένων, είναι σημαντιχό να εφαρμοστούν λειτουργίες και αλγόριθμοι προχειμένου να επιτευχθούν σημαντιχές μειώσεις χρόνου και χώρου όσον αφορά την πολυπλοχότητά τους. Το φίλτρο ανάγνωσης (Read Matching Filter - RMF), το οποίο υλοποίησα και παρουσιάζω σε αυτή τη διπλωματιχή εργασία, είναι ένα είδος αυτών των διαδιχασιών και έχει τον ρόλο της προεπεξεργασίας (φιλτράρισμα) των δεδομένων εισόδου στην διαδιχασία του genome assembly.

Το RMF παίρνει το σύνολο δεδομένων εισόδου που περιέχει το γενετικό υλικό διαχωρισμένο σε μέρη που ονομάζονται reads, ένα ανά γραμμή και εφαρμόζει μια διαδικασία αντιστοίχισης μεταξύ τους προκειμένου να βρεθεί αχρησιμοποίητος πλεονασμός. Όταν η διαδικασία εκτελεσθεί επιτυχώς, ο αχρησιμοποίητος πλεονασμός εξαλείφεται από το σύνολο δεδομένων και στην έξοδο παράγονται τα τελικά reads τα οποία ονομάζονται ενδιάμεσα (intermediate) contigs. Το τελικό αρχείο εξόδου έχει λιγότερα σε αριθμό και μεγαλύτερα ή ίσα σε μήκος reads σε σχέση με αυτά του συνόλου δεδομένων εισόδου, αλλά χωρίς τον αχρησιμοποίητο πλεονασμό και με αυτόν τον τρόπο το συνολικό μέγεθος του συνόλου δεδομένων γίνεται μικρότερο. Αξιοποιώντας αυτό το αποτέλεσμα, η διαδικασία του genome assembly λαμβάνει ένα μικρότερο σύνολο δεδομένων ως είσοδο και ως αποτέλεσμα κερδίζει ένα όφελος χρόνου στην διαδικασία εκτέλεσης.

Ο παραπάνω αλγόριθμος εφαρμόστηκε τόσο σε λογισμικό όσο και σε σχεδιασμό λογισμικού-υλικού σε Field Programmable Gate Array (FPGA) προκειμένου να επιταχυνθεί ο χρόνος εκτέλεσης. Οι έξοδοι του RMF και το αρχικό σύνολο δεδομένων εισόδου δίνονται ως είσοδος στο Velvet genome assembler το οποίο βασίζεται στον χειρισμό των γραφημάτων de Bruijn, μέσω της αφαίρεσης σφαλμάτων και της απλοποίησης επαναλαμβανόμενων περιοχών, προκειμένου να επεξεργαστεί τη συναρμολόγηση και να δώσει τις ακολουθίες εξόδου. Συμπεριλαμβανομένου του RMF η διαδικασία του genome assembly κέρδισε μια ταχύτητα εκτέλεσης της τάξης του 2x-6x, με καλή ποιότητα στα αποτελέσματα μεταξύ των δύο μεθόδων.

## Abstract

Georgios GALANOS

Hardware Acceleration of Genome Assembly Algorithms

Genome assembly is a field of bioinformatics that refers to the process of taking small fragments of genetic material and putting them back together by different methods in order to reconstruct the original sequence from which the DNA originated. As the DNA input datasets has numerous data size and in most cases has a very large amount of data, it is important to implement functions and algorithms in order to speedup these processes and gain significant time and space reductions in complexity. The Reads Matching Filter (RMF), which i implemented and present in this diploma thesis, is a kind of these processes and it has a preprocessing role in the whole genome assembly process.

The RMF takes the input dataset which contains the genetic material separated in reads, one per line and implement a matching process between each other in order to find unused redundancy. As the matching process executed successfully, the unused redundancy thrown out of the dataset and remain the output reads from the algorithm which they called intermediate contigs. The final output file that contains these intermediate contigs has less reads in number and bigger or equal than the input dataset's reads in length but without the unused redundancy and in this way the overall dataset size gets smaller. Exploited this result, the genome assembly process take a smaller dataset as input and as a result gain a time benefit in execution procedure.

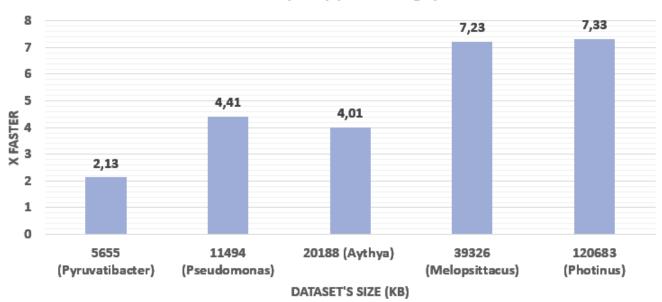

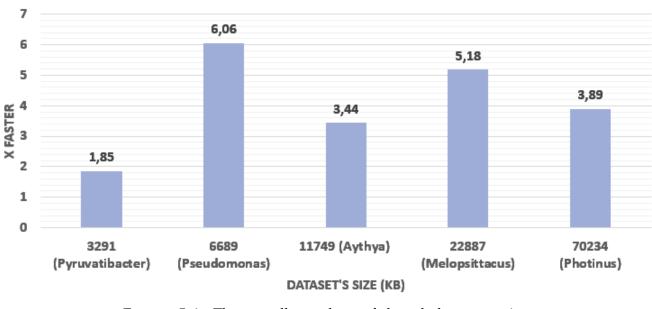

The above algorithm implemented both in a software only and in a softwarehardware design in Field Programmable Gate Array (FPGA) in order to gain an acceleration in execution time. The outputs of my design and the original input dataset are given as input in Velvet genome assembler which based on the manipulation of de Bruijn graphs, via the removal of errors and the simplication of repeated regions, in order to process the assembly and give the output sequences. The overall design included the genome assembly processing gained a speedup of the order of 2x-6x ratio, with good quality in the results between the two methods.

## Acknowledgements

Throughout the writing of this thesis i have received a great deal of support and assistance. All the way from the first appointment in order to decide the diploma thesis theme until the presentation i had a big support from colleagues and family members.

I would first like to thank my supervisor, Professor Apostolos Dollas, whose expertise was invaluable in formulating the whole outcome planning of this thesis in order to finish the work and the whole presentation of my diploma thesis, the writing and visualizing of the results and the tips in presenting things with a more specialized look, the look of an engineer. His insightful feedback pushed me to sharpen my thinking and brought my work to a higher level. Also, i gratefully acknowledge the occupation of my committee's members, who, including Professor Apostolos Dollas, are Professor Michail Zervakis and Dr. Georgios Kotoulas (HCMR).

I would also like to thank my colleague to a great extent, a special partner on my work Mr. Pavlo Malakonaki. Pavlo, I want to thank you for your patient support and for all of the opportunities i was given to further my research, implement the job and produce the results. You provided me with the tools that i needed to choose the right direction and successfully complete my thesis. I was glad to work with you and learn from you.

In addition, I would like to thank my parents for their cooperation and assistance to join this amazing faculty and sympathetic ear. You are always there for me. Finally, I could not have completed this dissertation without the support of my sisters, close friends and acquaintances, who provided stimulating discussions as well as happy distractions to rest my mind outside of my research.

Georgios Galanos,

Heraklion 2021

# Contents

| Al | ostrac     | ct                                                           | 3        |

|----|------------|--------------------------------------------------------------|----------|

| Al | ostrad     | ct                                                           | 5        |

| Ac | cknov      | wledgements                                                  | 7        |

| Li | st of I    | Figures                                                      | 11       |

| Li | st of '    | Tables                                                       | 13       |

| 1  | Intr       | oduction                                                     | 15       |

|    | 1.1<br>1.2 | My Thesis Contribution                                       | 16<br>16 |

| 2  | The        | oretical Background and Related Work                         | 19       |

|    | 2.1        | Genome                                                       | 19       |

|    | 2.2        | Genome Processing                                            | 20       |

|    |            | 2.2.1 Genome Processing Chronology                           | 20       |

|    | 2.3        | Genome Processing Programs and Tools                         | 22       |

|    |            | 2.3.1 The shotgun sequencing technique                       | 22       |

|    |            | 2.3.2 Datasets and File Types                                | 23       |

|    | 2.4        | Genome Assembly                                              | 23       |

|    |            | 2.4.1 Reference-Based Mapping Assembly                       | 23       |

|    |            | 2.4.2 De Novo Genome Assembly                                | 24       |

|    |            | 2.4.3 Genome assembler's implementations                     | 24       |

|    |            | 2.4.4 The hierarchical stages of the genome assembly and the |          |

|    |            | N50 metric                                                   | 25       |

|    |            | 2.4.5 Genome assembler programs                              | 26       |

|    |            | 2.4.6 Software Tools                                         | 26       |

|    | 2.5        | Related Work                                                 | 27       |

|    | 2.6        | Scientific Contributions                                     | 29       |

|    |            | 2.6.1 Acceleration of Algorithms                             | 29       |

|    | 2.7        | Motivation and our approach                                  | 30       |

|    |            | 2.7.1 Amdahl's law and theoretical parallel speedup          | 31       |

| 3  | Rea        | ds Matching Filter                                           | 35       |

|    | 3.1        | Software initial implementation                              | 35       |

|    |            | 3.1.1 Using different HBM banks to store the data            | 37       |

|    | 3.2        | Hardware initial implementation                              | 37       |

|    |            | 3.2.1 The top level implementation                           | 38       |

|   |                                                           | 3.2.2                                                                                                                   | Removing read vector construction and prefilter stage   | 40                                                                          |

|---|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-----------------------------------------------------------------------------|

|   |                                                           | 3.2.3                                                                                                                   | The complementary DNA strand                            | 41                                                                          |

|   |                                                           | 3.2.4                                                                                                                   | Extender implementation                                 | 42                                                                          |

|   |                                                           | 3.2.5                                                                                                                   | Write back stage                                        | 45                                                                          |

|   | 3.3                                                       | Final o                                                                                                                 | lesign implementation                                   | 48                                                                          |

|   |                                                           | 3.3.1                                                                                                                   | Host reconfiguration                                    | 48                                                                          |

|   |                                                           | 3.3.2                                                                                                                   | Kernel reconfiguration                                  | 49                                                                          |

|   |                                                           | 3.3.3                                                                                                                   | The reconfiguration in the software only implementation | 50                                                                          |

|   | 3.4                                                       | Time a                                                                                                                  | and space reports for both of the implementations       | 51                                                                          |

|   | 3.5                                                       | Extend                                                                                                                  | ded implementation                                      | 53                                                                          |

|   |                                                           | 3.5.1                                                                                                                   | Host reconfigurations                                   | 53                                                                          |

|   |                                                           | 3.5.2                                                                                                                   | Kernel reconfigurations                                 | 54                                                                          |

|   |                                                           | 3.5.3                                                                                                                   | Extended design exceeded the limit of FPGA resources    | 56                                                                          |

|   |                                                           | 3.5.4                                                                                                                   | A different extended implementation design              | 57                                                                          |

|   | 3.6                                                       | The sc                                                                                                                  | oftware implementation with score table                 | 57                                                                          |

|   |                                                           |                                                                                                                         |                                                         |                                                                             |

| 4 | Rest                                                      | ults and                                                                                                                | 1 Discussion                                            | 59                                                                          |

| 4 | <b>Res</b><br>4.1                                         |                                                                                                                         |                                                         | <b>59</b><br>60                                                             |

| 4 |                                                           |                                                                                                                         | y results                                               |                                                                             |

| 4 |                                                           | Qualit<br>4.1.1                                                                                                         | y results                                               | 60                                                                          |

| 4 | 4.1                                                       | Qualit<br>4.1.1                                                                                                         | y results                                               | 60<br>61                                                                    |

| 4 | 4.1                                                       | Qualit<br>4.1.1<br>Initial                                                                                              | y results                                               | 60<br>61<br>62                                                              |

| 4 | 4.1                                                       | Qualit<br>4.1.1<br>Initial<br>4.2.1                                                                                     | y results                                               | 60<br>61<br>62<br>62                                                        |

| 4 | 4.1                                                       | Qualit<br>4.1.1<br>Initial<br>4.2.1<br>4.2.2<br>4.2.3                                                                   | y results                                               | 60<br>61<br>62<br>62<br>63                                                  |

| 4 | 4.1<br>4.2                                                | Qualit<br>4.1.1<br>Initial<br>4.2.1<br>4.2.2<br>4.2.3                                                                   | y results                                               | 60<br>61<br>62<br>62<br>63<br>63                                            |

| 4 | 4.1<br>4.2                                                | Qualit<br>4.1.1<br>Initial<br>4.2.1<br>4.2.2<br>4.2.3<br>Final c                                                        | ty results                                              | 60<br>61<br>62<br>63<br>63<br>65                                            |

| 4 | 4.1<br>4.2                                                | Qualit<br>4.1.1<br>Initial<br>4.2.1<br>4.2.2<br>4.2.3<br>Final o<br>4.3.1                                               | y results                                               | 60<br>61<br>62<br>63<br>63<br>65<br>65                                      |

| 4 | <ul><li>4.1</li><li>4.2</li><li>4.3</li></ul>             | Qualit<br>4.1.1<br>Initial<br>4.2.1<br>4.2.2<br>4.2.3<br>Final o<br>4.3.1<br>4.3.2<br>4.3.3                             | y results                                               | 60<br>61<br>62<br>63<br>63<br>65<br>65<br>66<br>66                          |

|   | <ul><li>4.1</li><li>4.2</li><li>4.3</li></ul>             | Qualit<br>4.1.1<br>Initial<br>4.2.1<br>4.2.2<br>4.2.3<br>Final c<br>4.3.1<br>4.3.2<br>4.3.3<br>clusior                  | ty results                                              | 60<br>61<br>62<br>63<br>63<br>63<br>65<br>65<br>65                          |

|   | <ul><li>4.1</li><li>4.2</li><li>4.3</li><li>Con</li></ul> | Qualit<br>4.1.1<br>Initial<br>4.2.1<br>4.2.2<br>4.2.3<br>Final o<br>4.3.1<br>4.3.2<br>4.3.3<br><b>clusion</b><br>Conclu | y results                                               | 60<br>61<br>62<br>63<br>63<br>65<br>65<br>65<br>66<br>66<br>66<br><b>69</b> |

# **List of Figures**

| 2.1 | The DNA double helix with the nucleobases                       | 20 |

|-----|-----------------------------------------------------------------|----|

| 2.2 | The Human Genome Project launched in 1990                       | 22 |

| 2.3 | Features of selected short reads assembly programs              | 27 |

| 2.4 | Generation of two outputs sequences.                            | 31 |

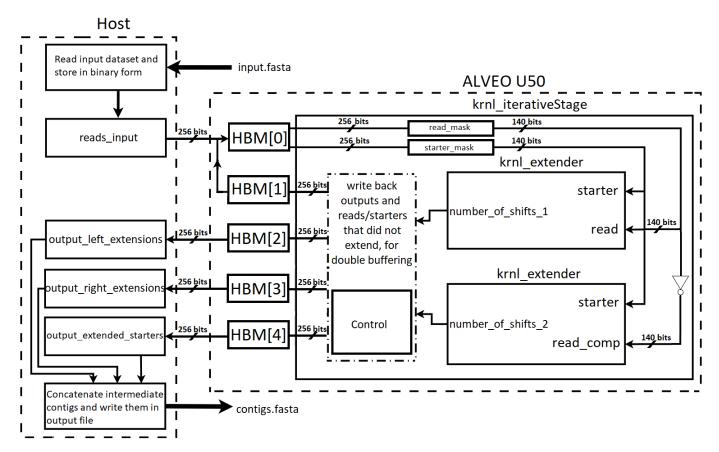

| 3.1 | Our first design in general (host and kernel)                   | 38 |

| 3.2 | Read vector construction.                                       | 40 |

| 3.3 | The double helix of the DNA: the two twin DNA strands           | 42 |

| 3.4 | The extender design.                                            | 44 |

| 3.5 | The write back stage of our kernel.                             | 46 |

| 3.6 | The output register of the write back stage. Read or read_comp  |    |

|     | concatenated with the number of shifts                          | 47 |

| 3.7 | Our final design in general (host and kernel). We have the      |    |

|     | 256-bits width board interface and the removal of the prefilter |    |

|     | stage of read vector's construction.                            | 49 |

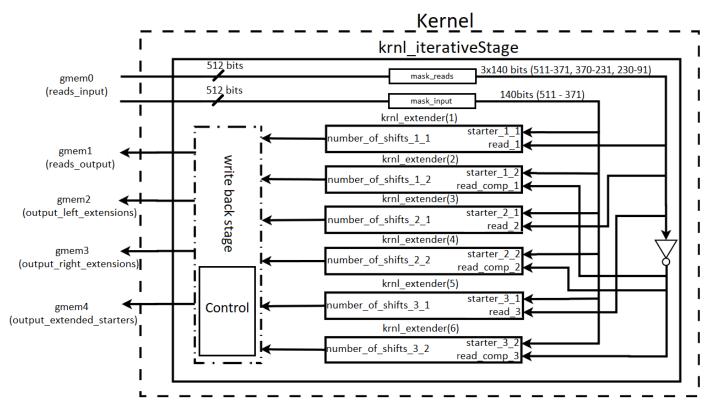

| 3.8 | The extended Kernel with the triad of reads.                    | 55 |

| 4.1 | The ALVEO U50 Acceleration Card                                 | 60 |

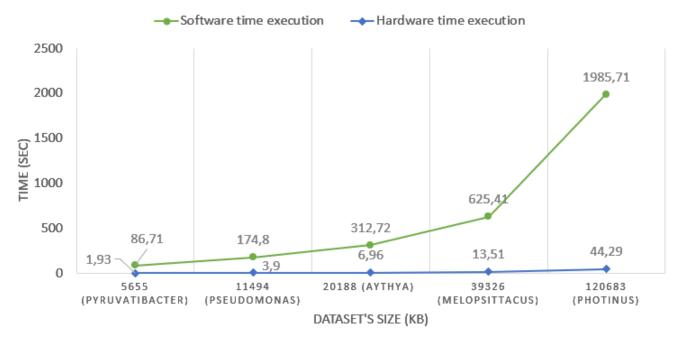

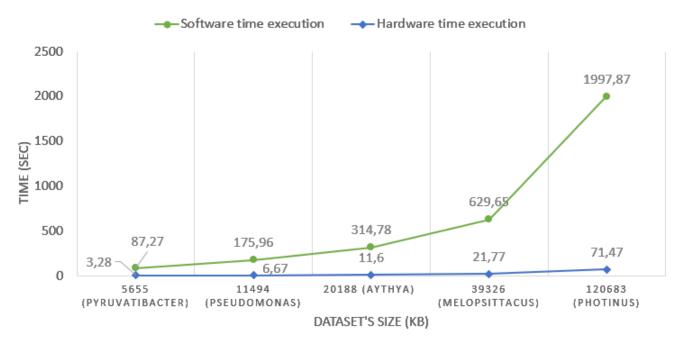

| 5.1 | RMF measured execution times both in software and hard-         |    |

|     | ware (without I/O operations from host/software)                | 70 |

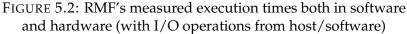

| 5.2 | RMF's measured execution times both in software and hard-       |    |

|     | ware (with I/O operations from host/software)                   | 71 |

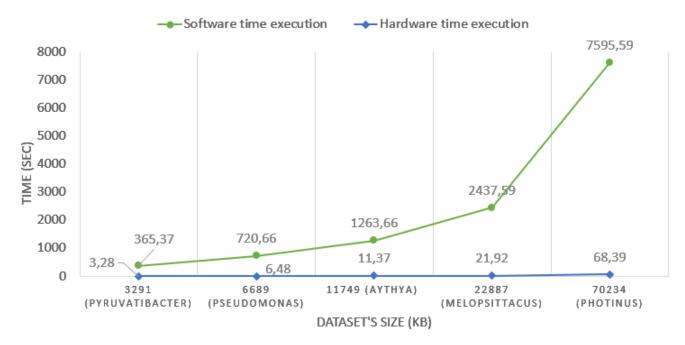

| 5.3 | RMF's measured execution times both in software and hard-       |    |

|     | ware (with I/O operations from host/software)                   | 71 |

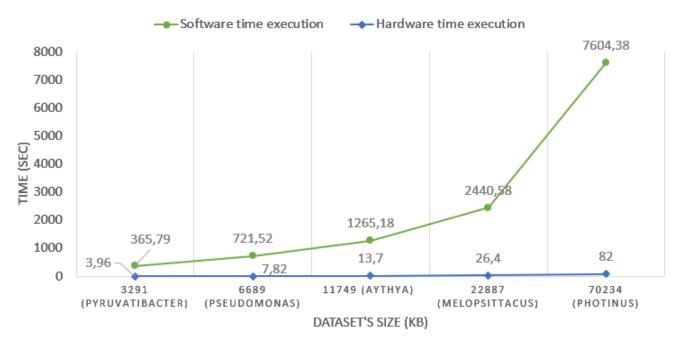

| 5.4 | RMF's measured execution times both in software and hard-       |    |

|     | ware (with I/O operations from host/software)                   | 72 |

| 5.5 | The overall speedup of the whole process included the Velvet    |    |

|     | assembly stage and our initial filtering implementation         | 72 |

| 5.6 | The overall speedups of the whole process included the Velvet   |    |

|     | assembly stage and our final filtering implementation           | 73 |

|     |                                                                 |    |

# List of Tables

| 2.1   | The percentage of the overall RMF's execution time, which the processing stage occupies. | 32       |

|-------|------------------------------------------------------------------------------------------|----------|

| 2.2   | Maximum theoretical possible speedups.                                                   | 32       |

| 2.2   | The percentage of the entire assembly process' execution time                            | 52       |

| 2.0   | if we do not account for the RMF.                                                        | 33       |

| 2.4   | Maximum theoretical possible speedups of the entire process.                             | 33       |

|       | in a difference in possible opecaups of the churc process.                               | 00       |

| 3.1   | The conversion formula of DNA bases                                                      | 36       |

| 3.2   | Changes in kernel execution time in FPGA with or without                                 |          |

|       | prefiltering stage                                                                       | 41       |

| 3.3   | The Vivado log measures for the first implementation pf the                              |          |

|       | RMF (128 bits data transferring).                                                        | 52       |

| 3.4   | The Vivado log measures for the final implementation of RMF                              |          |

|       | (256 bits data transferring).                                                            | 52       |

| 4.1   | The ALVEO U50 acceleration card specifications.                                          | 60       |

| 4.2   | The N50 metrics of the assembly from the outputs of the velvet                           | 00       |

|       | genome assembler.                                                                        | 61       |

| 4.3   | Processing module's measured execution times both in soft-                               |          |

|       | ware and hardware and the speedups (without I/O operations                               |          |

|       | from host/software).                                                                     | 62       |

| 4.4   | My design runs both in software and hardware and the speedups                            |          |

|       | (included I/O operations)                                                                | 63       |

| 4.5   | The measured execution times of the assembly with our pre-                               |          |

|       | processing stage involved.                                                               | 64       |

| 4.6   | The measured execution times of data path without our hard-                              |          |

|       | ware design involved (only Velvet run).                                                  | 64       |

| 4.7   | Overall speedup between the two methods.                                                 | 64       |

| 4.8   | The measured execution times for the processing module of                                | ~ =      |

| 1.0   | the RMF in final implementation.                                                         | 65       |

| 4.9   | The measured execution times for the RMF included the I/O                                | "        |

| 4 1 0 | operations in final implementation.                                                      | 66       |

|       | The measured execution times of Velvet with the original datasets                        | . 67     |

| 4.11  | The measured execution times of the assembly with our RMF involved.                      | 67       |

| 110   | The reduction of the dataset's size from our RMF.                                        | 67<br>67 |

|       | The measured execution times and the overall speedup with                                | 07       |

| т.15  | our final implementation filter involved.                                                | 68       |

|       |                                                                                          | 00       |

## Chapter 1

## Introduction

Bioinformatics is an interdisciplinary field that develops methods and algorithms in order to compute and execute biological data and tasks. As an interdisciplinary field of science, bioinformatics combines biology, computer science, information engineering, mathematics and statistics to analyze and interpret the biological data. Biological computation combines bioengineering and biology to build biological computers and algorithms, whereas bioinformatics uses to better understand biology. It is a fact that nowadays we have large amount of data to deal with for research propose, studies and innovations and we want useful tools to implement our job faster and better. In bioinformatics we have jobs such as genome processing, genome assembly and many others biological tasks, presuppose a very good space exploitation and a reduction in execution time as much as possible, to have a functional operational level and a good execution time. The primary goal of bioinformatics is to increase the understanding of biological processes. We have machine learning algorithms, pattern recognition, data mining, sequence alignment, protein structure prediction and clustering in families, visualization and so on, tasks which can be implemented with the contribution of the science of maths, software and hardware engineering and IT (Information technology) in general [18].

Biologists and more especially molecular ones, in the wide range of their work, use DNA, RNA, protein and other sequences, which in many cases are very large quantitative data. They have to deal with many bytes of sequencing data which need processing on computing clusters. Even if we assume the unusable redundancy this sequences may have, we can understand the increment of the time and space complexity of algorithms could have. Here is where genome sequencing take place and help by reconstructing the large sequences, by assembling the contigs into new one without any redundancy, by keeping the quality of the genome unanalyzed, as much as possible (e.g. error may occurred while reconstruction, repeats may exists). In this work we implemented a genome preprocessing filter which the main approach is presented in [39] and we make some changes to make it functional in a new FPGA to obtain a better time benefit, which is analyzed below. After that, a genome assembler can take the output contigs of our filtering stage and can construct new individual genomes. The processing time of the tasks of

a genome assembler can be considered exponentially increasing with the input file size and thus have been implemented methods which reduce the data size without missing valuable information.

### 1.1 My Thesis Contribution

In this section i will present the contribution of my diploma thesis theme among the above needs of increasing the efficiency and the effectiveness of the bioinformatics algorithms and programs. The design i implemented is a preprocessing technique and i present the implementation and the differences that we done among the various similar implementations. There are many techniques that can be implement in order to speedup the genome assembly processing and the genome sequencing in general. As DNA assembly technology cannot read whole genomes in one go, but rather reads smaller pieces, genome sequencing is a necessary task. The processing of genome assembly is a very time consuming, and as a result, expensive job. So, it is important to implement tools that assist the processing of genome reconstruction by filtering the data, which reduce the space complexity (RAM usage, hard drive space) as well as the processing time. In this paper we propose the use of reconfigurable hardware (FPGAs) in order to accelerate the execution of a pre-filtering process that removes the redundancy in a genome dataset. The Reads Matching Filter (RMF) executes a matching process between the reads of a DNA dataset in order to combine them and remove the redundant reads. As a result we have reducing on the assembly input dataset's size and the complexity of the assembly at all.

The implemented filter which acts as preprocessor generates an output that can be as input in Velvet genome assembler [34]. The basic logic about this RMF preprocessor is to takes the input reads, find for matches between the reads and generating the output contigs in order to give it as input in Velvet assembler to generate the final contigs. In contrast we pass the input reads as it is in Velvet assembler and taking the output contigs to check the similarity between the two outputs to examine the efficiency of the implementation. We found numerous speedups between the two methods and the general processing time of the assembly by Velvet reduced. The quality of the outputs seems to be satisfactorily in terms of targeting a state of the art FPGA platform that lead to a different architectural implementation in order to take advantage of the characteristics of the new platform, with respect to both I/O capabilities and hardware resources.

### 1.2 Thesis Outline

In this section we outline the organization of this thesis.

• **Chapter 2:** We describe in detail the theoretical background of the Genome Sequencing and Genome Assembly and we present the related work that exists in this field.

- **Chapter 3:** We intend to describe our implementation of the preprocessing genome sequencing program, both in software and hardware implementation and describe the differences between our's and paper's approach.

- **Chapter 4:** We present the results of our implementation.

- **Chapter 5:** We conclude this thesis and we provide directions for future work and possible extensions to our work.

## Chapter 2

## Theoretical Background and Related Work

In this Chapter, we will describe in detail the theoretical background of Genome Assembly and Genome Sequencing and we present the related work which has already been done both in research and the already existing bioinformating field.

As DNA sequencing technology works with big amount of data using bigger genomes and sequences, it needs algorithmic ways to implement aligning and merging techniques to the sequences in order to reduce the size of the read used or reconstruct genomes without loosing the quality of the output. This techniques follow algorithms of specific steps which are based on the match between consecutively reads in order to cover the unused redundancy between them. This can be done by many different ways which are listed below. The final result is a DNA sequence that it is in most cases unique or needing further processing in order to be unique (became a whole genome sequence). The result may contains faults or unwanted redundancy and in that case we can use other algorithms to prevent or fix these issues or we further processing it in order to reconstructed. These techniques cover the overall genome sequencing processing and all these approaches can help the genome assembly and many other biology tasks.

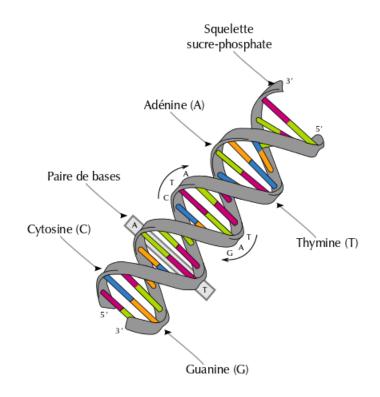

#### 2.1 Genome

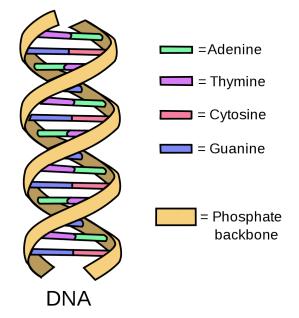

In the fields of molecular biology and genetics, a genome is the genetic material of an organism that present in the cells or in atoms. It provides all of the information the organism requires to function. It consist of **Deoxyribonucleic acid (DNA)**, a chain that is a molecule composed of two poly nucleotide chains that coil around each other to form a double helix. This two DNA strands are known as polynucleotides as they are composed of simpler monomeric units called nucleotides. Each nucleotide is composed of one of four nitrogen-containing **nucleobases (cytosine [C], guanine [G], adenine [A] or thymine [T])**.

```

FIGURE 2.1: The DNA double helix with the nucleobases

https://www.yourgenome.org/sites/default/files/illustrations/diagram/

dna_double_helix_yourgenome.png

```

The genomes can be extended, reconstructed and concatenate between each other in biological processes and create a very large sequence that needs assembly to reworked and deciphering the sequence composition of the genetic material (DNA), in order to exported new genome material for a new organism or a different version of the already existed organism.

### 2.2 Genome Processing

As we mention above, genome processing combined with genome assembly are the computational job of reconstruct genomes and assemble reads in order to generate new or make a deeper research about genome sequences of organism, bacteria, chromosomes and all the other genome stages that detailed described below. Genome processing started many years ago and here we present the general chronology.

#### 2.2.1 Genome Processing Chronology

Genome Processing is a very old research field for the need of humanity to learn more about his health and for survival purpose. Besides of this, humanity want to learn more about the life, the creatures, the material and the whole world around. For that humanity's thirst of learning, the chronology of genome processing begins before 1900.

The very early 1871 Friedrich Miescher first publishes his paper where found the appearance of 'nuclein' (now known as DNA) and associated proteins, in the cell nucleus [11]. In 1910, the first big step in genome processing happened, when Albrecht Kossel is awarded the first Nobel Prize in Physiology or Medicine for his discovery of the five nucleotide bases, adenine, cytosine, guanine, thymine and uracil.

Computers became essential in molecular biology when protein sequences first became available in the early 1950s. Then was the time when Frederick Sanger determined the sequence of insulin. Starting of this, comparing multiple sequences manually turned out to be impractical, so scientist try to figure out how to work on computer. After that, in 1953, James Watson and Francis Crick, with contributions from Rosalind Franklin and Maurice Wilkins, discover the double helix structure of DNA. In 1977, Frederick Sanger develops a DNA sequencing technique which he and his team use to sequence full genomes and invented the very first genome - that of a virus called phiX174 [14].

The need of software implementation, sequencing and assembling on computer, became more imperative decade-by-decade as in 1980 Frederic Sanger shares the Nobel Prize for Chemistry with Wally Gilbert and Paul Berg, for pioneering DNA sequencing methods which help on determination of the amino acid sequence of insulin, RNA and DNA sequencing [25]. In 1990, Human Genome Project is launched [31] (figure 2.2). The project aims to sequence all 3 billion letters of a human genome in 15 years. In 1999, Chromosome 22 is the first human chromosome to be sequenced as part of this project. The first try of determination of the human genome sequence released in 2001 and 2003 Human Genome Project is completed and confirms humans have approximately 20,000–25,000 genes. The human genome is sequenced to 99.99 per cent accuracy, 2 years ahead of schedule, in a very historic moment for biology. Additionally a recent update in this impressive project, on May 27 2021, the complete human genome sequence is close. Scientists from University of California, report that they have sequenced the remainder, in the process discovering about 115 new genes that code for proteins, for a total of 19,969. Researchers added 200 million DNA base pairs and 115 protein-coding genes — but they have yet to entirely sequence the Y chromosome, mentions Nature Portfolio [24].

The chronological development and the requirements of genome sequencing is constantly increasing and nowadays we have big amount of data for bioinformatics researches. As DNA assembly technology cannot read whole genomes in one go, but rather reads smaller pieces, genome sequencing is a necessary task. The DNA chains may consist of many bases and the processing in computers may be very difficult and expensive job. So, it is important to implement algorithms and tools that reconstruct the genomes (by throws the unused redundancy or errors) and reduce the space complexity (RAM usage, hard drive space) of biological processes.

FIGURE 2.2: The Human Genome Project launched in 1990 https://www.slideshare.net/vinithasekar/human-genome-project-72272927

### 2.3 Genome Processing Programs and Tools

Many databases, dataset files, techniques and algorithm are used by scientists in genome processing processes. Many file types describes DNA sequences with different details and information level between them. These file types form datasets that include DNA material and can be used as input in genome assembly programs or output from them. Depending the read's length, the number of reads or the information that each dataset consist of, there are many assembly programs in order to reconstruct genomes. After the assembly stage further genome processing might happen. The output of the genome assemblers can be further processed and analyzed by sequence analyzers such as BLAST [3], tools that can calculate the similarity between multiple output sequences to define the measure of correctness of the result.

#### 2.3.1 The shotgun sequencing technique

Most DNA sequencing techniques produce short fragments of sequence that need to be assembled to obtain complete genome sequences. The so-called shotgun sequencing technique and it is named by analogy with the rapidly expanding, quasi-random firing pattern of a shotgun [23]. The ends of these fragments overlap and, when aligned properly by a genome assembly program (such as Velvet), can be used to construct the complete genome. Shotgun sequencing yields sequence data quickly, but the task of assembling the fragments can be quite complicated for larger genomes. For a genome as large as the human genome, it may take large time frames of CPU time on large-memory, multiprocessor computers to assemble the fragments, and the resulting assembly usually contains numerous gaps that must be filled in later. All the assembling methods that exist have big temporal and spatial complexity because the size of input data. The task must take all the reads, one by one and compare between each other for possible matches. Here is the hardware based acceleration that can be useful. Shotgun sequencing is the method of choice for virtually all genomes sequenced today, and genome assembly algorithms are a critical area of bioinformatics research to take shot-gun sequences as input in order to implement the assembly. The majority of the input files which we used is a result of this shotgun technique.

#### 2.3.2 Datasets and File Types

Especially in dataset and file formats we have different formats concerning the details we want to include in the specific file. There are many file types that contains and describes DNA sequences [29] [13] and the most widespread one is the FASTA (and FASTQ) file format in case we do not want to include additional information about the genome. This type of file is the simplest one and has a first line begin with the symbol '>' and can contains the title of the genome and some of the description, such as the type of data this file contains (e.g. shotgun generated reads or complete genomes). After that details line we have the genome reads, one per line with a various line length per dataset, most commonly of 60 or 70 bases per line and in some cases bigger line length (e.g. 80,90), but it is a fact that all the reads contained in a FASTA file has the same length per line. FASTQ is a similar file type to FASTA, but is has other information, nucleotide base calls, a second definition line, and per-base quality scores, all in text form. In our approach we use FASTA file format both as input and output of our algorithm.

### 2.4 Genome Assembly

One of the main task in genome processing is the genome assembly. In bioinformatics, genome assembly refers to aligning and merging fragments from a longer DNA sequence in order to reconstruct the original sequence. Is the computational step that follows sequencing with the objective of reconstructing the genome from its reads. There are two major categories of genome assembly, the reference-based mapping assembly and the simple de novo assembly.

#### 2.4.1 Reference-Based Mapping Assembly

The first category assembling reads against an existing "template" sequence, build-in a sequence that is similar but not necessarily identical to the "template" sequence. If the genome has been sequenced before and a reference genome sequence already exists, then the newly obtained re-sequence reads are first mapped to the reference genome through alignment and then assembled in proper order. A revolutionary technique is the one mentioned above of Polymerase Chain Reaction (PCR)[22] which developed by Kary Mullis in the 1980s. It is about a reference-based mapping sequence technique which is based on using the ability of DNA polymerase to synthesize new strand of DNA complementary to the offered template strand. In 2007 a new DNA sequencing technology is introduced [22] that increases DNA sequencing effectiveness. The new DNA sequencing process is simpler, more accurate and efficient than the multiplex PCR that was previously used. A microarray-based technique of genome sequencing machines which quickly determine the exact genetic code of the material, come to replace the previous PCR technique [28]. Another one aligner is Bowtie, an ultra fast memory-efficient short read aligner which aligns short DNA sequences to a reference genome at a rate of over 25 million 35-bp reads per hour [4].

#### 2.4.2 De Novo Genome Assembly

The second category of genome assembly is the De novo sequence assemblers. De novo sequence assemblers are a type of program that assembles short nucleotide sequences into longer ones without the use of a reference genome. We got involved with a de novo genome assembly which has two common types of assemble programs; greedy algorithm assemblers and assemblers that construct a De Bruijn graph to represent their intermediate contigs. This assembler is Velvet [34] that we used it assembly our intermediate output contigs of our design. The input of the assembler is the intermediate contigs that our kernel generates. The main idea of our algorithm is that the pairwise alignment of all reads is done and the reads with the largest overlap is merged. This process is repeated till a single lengthy sequence is obtained. In this way we can give, as input in assembler, a smaller input file without loosing any significant information and so speeds up the processing time of the tool.

#### 2.4.3 Genome assembler's implementations

Genome assembly from sequence reads is an algorithm-driven automated process. It is a computational expensive problem and for that reason there are many different techniques and methods in order to implement it. To date genome assembly can be done using one of the below three approaches:(1) greedy, (2) overlap-layout-consensus (OLC) and Hamiltonian path, and (3) de Bruijn graph and Eulerian path [17].

Greedy approach is the simplest, most intuitive, solution to the assembly problem. Individual reads are joined together into contigs in an iterative fashion, starting with the reads that overlap best, and ending once no more reads or contigs can be joined. This technique may failed under specific conditions that the contigs do not have any significant base coherence in common. In this situation the output contigs includes gaps. Paired-end sequencing is used to close these gaps. This technique allows the sequencing both of the ends of a fragment and generate high-quality, alignable data. The second approach is the overlap-layout-consensus approach, which has 3 basic steps. The first step is using the greedy algorithm that described above, generating an output with the intermediate contigs that had been joined. In the second step it uses this output to construct an overlap graph; a graph containing each read as a node and an edge connects two nodes if an overlap was identified between the corresponding reads. The third and final step is the solution of the Hamiltonian path of this graph. Assembler try to find a single path that traverses each node in the overlap graph exactly once and generate and output which is a complete genome.

The third approach is that which uses the reads to construct a de Bruijn graph [6]. It can be recommended used in cases that the reads are short (<100bp). The main idea is that reads broken down to smaller sequences called k-mers. These k-mers are aligned using (k-1) sequence overlaps. The actual size of k depends on sequence coverage, read length, etc., but usually is not less than half of the actual read length. The final genome constructed by the Eulerian cycle method that visits every edge exactly once (allowing for revisiting vertices).

# 2.4.4 The hierarchical stages of the genome assembly and the N50 metric

Generally speaking the genome assembly is a multiprocessing job that includes different stages. Therefore, genome assembly is a hierarchical process; it is performed in steps beginning from the assembly of the sequence reads into contigs, assembly of the contigs into scaffolds (supercontigs) and assembly of the scaffolds into chromosomes. The most difficult assembly process is the assembly from the scaffolds into chromosomes because the gaps can not be easily sequenced. For that reason we have many assemblies remain restricted to scaffold level.

The quality review of the assembly is not so clear predefined. On the other hand, one very usual and useful metric in order to quantify the quality of the assembly is the N50 value. The N50 contig value can be determined by first sorting all contigs in decreasing order of size, then adding the contigs until the total added size reaches at least half of the total size of all assembled contigs. The size of the smallest contig used in this addition process represents the N50. The assembly processing can be executed multiple times until we reach a maximum N50 value. The larger the N50 value, the better is the assembly. Using the same concept, higher values of N are also used, such as N60 (until reach the 60% of the assembled contigs) and N80 (until reach the 80% of the assembled contigs). If the N50 scaffold length is too short, additional rounds of shotgun sequencing are recommended.

#### 2.4.5 Genome assembler programs

Occasionally there were many software programs and tools that implement genome assembly processes and nowadays there is a very big occupation from the researchers and programmers to make faster and better programs and tools for this tasks. We have many assemblers that can make the reconstruction of the genome from its fragments. Our approach takes either the shotgun sequencing dataset or any other datasets, with the scattered parts of the genome (input reads), make the match between similar reads and throws the presented redundancy. The output intermediate contigs of our filtering stage, given as input in a genome assembler program in order to match the contigs to construct the whole genome (or new assembled contigs). We had a wide variety of these programs to use as well as most of them are open to use.

As we mention above, there are three main ways to implement a genome assembler and in that three ways we have the grouping of them, having as criterion and the intermediate contig's length. According to article [42] we have the figure 2.3 of genome assembly programs and its features. We have in column 'Algorithm' the way each assembler implemented and some others information such as the programming language they are implemented, the required read length and if they works with single-end, paired-end or both, reads. In our case we had single-end reads with numerous read length in FASTA input formats and so we try to use Velvet, SOAPdenovo [33] or SPAdes[2] (which is not included in the figure) and finally we keep the Velvet which compiled faster, it was easiest to use and easiest to pass the arguments we want. Apart from this, we wanted to use the same assembler with the motivated paper's one in order to compare the results between them.

#### 2.4.6 Software Tools

After the genome assembler gives an output of complete genome from our intermediate contigs as inputs, we have a big variety of sequence alignment tools, such as BLAST [3] to farther analyze the results. These tools takes multiple sequences and try to find the biggest matching rate between them by shift the sequences. This task can be very useful if we take the output from genome assembler (as they generating by genome assembler) and put it in sequence analyzer, alongside with the output of the genome assembler by using the intermediate contigs of our design as input. This match rate can be a satisfying criteria of similarity, in order to decide if our intermediate contigs where right. The match rate is calculated in a reward/penalty ratio and depending on this we can assume a percent of similarity. An average percent of similarity above 95% is a very good result.

| Program                    | Provin               | IT Pros | Survivo Language            | s patom<br>patom<br>page | ired read | single contract | Pairedes | pot ousing out | elomot Dominad                                              | Hersite |

|----------------------------|----------------------|---------|-----------------------------|--------------------------|-----------|-----------------|----------|----------------|-------------------------------------------------------------|---------|

| SSAKE<br>(V3.5)            | Greedy-<br>extension | perl    | *                           | 25-36nt                  | Y         | Y               | N        | Fasta/Raw      | http://www.bcgsc.ca/<br>platform/bioinfo/soft<br>ware/ssake | -<br>-  |

| VCAKE<br>(V1.0)            | Greedy-<br>extension | perl    | *                           | <40nt                    | Y         | N               | N        | Fasta/Raw      | http://sourceforge.ne<br>t/projects/vcake/                  |         |

| QSRA                       | Greedy-<br>extension | C++     | Unix/Linux                  | <40nt                    | Y         | N               | Y        | Fasta/Raw      | http://qsra.cgrb.oreg<br>onstate.edu/                       |         |

| SHARCGS<br>(19-Nov-07)     | Greedy-<br>extension | perl    | *                           | 25-40nt                  | Y         | N               | Y        | Fasta/Raw      | http://sharcgs.molge<br>n.mpg.de/download.<br>shtml         |         |

| Edena<br>(V2.1.1)          | OLC                  | C++     | Win/Linux                   | N/A                      | Y         | N               | N        | Fasta/Fastq    | http://www.genomic.<br>ch/edena.php                         |         |

| <b>Velvet</b><br>(V0.7.59) | De Bruijn            | с       | Linux/Mac<br>OS<br>X/Cygwin | N/A                      | Y         | Y               | N        | Fasta/Fastq    | http://www.ebi.ac.uk/<br>~zerbino/velvet/                   |         |

| SOAPdenovo<br>(V1.04)      | De Bruijn            | С       | Linux/Mac<br>OS             | N/A                      | Y         | Y               | N        | Fasta/Fastq    | http://soap.genomics<br>.org.cn/soapdenovo.<br>html         |         |

| Taipan<br>(V1.0)           | Hybrid<br>algorithm  | С       | Linux                       | N/A                      | Y         | N               | N        | Raw            | http://sourceforge.ne<br>t/projects/taipan/                 |         |

FIGURE 2.3: Features of selected short reads assembly programs.

https://doi.org/10.1371/journal.pone.0017915.g011

## 2.5 Related Work

In related work we can find numerous bibliography about the innovations and the additional study that has been done in bioinformatics field. These works helped and continue to help the ever-increasing technology in biology and medical science, revealing and improving techniques and algorithms. In these many researches, our institution, the Technical University of Crete, has involved with many interesting works.

First of all there is the work in [8] where Grigorios Chrysos et. al. presents an in-depth look of how FPGA computing can offer substantial speedups in the execution of bioinformatics algorithms, with specific results achieved to date for a broad range of algorithms. The main conclusion is that FPGAs with the programmable logic they have, can be a significant tool to make bioinformatics algorithms works faster. Examples and case studies are presented for sequence comparison (BLAST, CAST), multiple sequence alignment (MAFFT, T-Coffee), RNA and protein secondary structure prediction (Zuker, Predator), gene prediction (Glimmer/GlimmerHMM) and phylogenetic tree computation (RAxML), running on mainstream FPGA technologies as well as high-end FPGA-based systems (Convey HC1, BeeCube).

In [16], Matina Lakka et al., presents the implementation on FPGA of two of the best known Multiple Sequence Alignment (MSA) algorithms, which offer high accuracy and great performance, T-Coffee and MAFFT. This paper presents the implementation of these algorithms on present-day FPGAs.

They conclude that for "large" datasets their design is 4 to 5 times faster. For "small" datasets they did not take good results but they assumed that for a large modern FPGA device they can have up to 15 parallel their designs, thus achievings peedup from 10 to 55 times faster.

In advance we can mention the PhD dissertation on Reconfigurable Architecture Structures for the BLAST DNA Sequencing Algorithm, which presented in 2011 from Dr. E. Sotiriades in [27]. In a few words as he mentions Dr. Sotiriades, presents a system based on reconfigurable logic to implement the BLAST algorithm, regardless of data size or algorithm variation [3]. His design consists of software and hardware parts and achieves a speedup of several times up to thousands of times vs general purpose computers. We use the Blast sequence alignment in our study to check the efficiency of our algorithm.

In May of 2014 in [5], Chuming Chen et. al. developed ngsShoRT (nextgeneration sequencing (NGS) Short Reads Trimmer), a flexible and comprehensive open-source software package written in Perl that provides a set of algorithms commonly used for pre-processing NGS short read sequences. They compared the features and performance of ngsShoRT with existing tools: CutAdapt, NGS QC Toolkit and Trimmomatic. They also compared the effects of using pre-processed short read sequences generated by different algorithms on De-novo and reference-based assembly. Their results show that across three organisms and three sequencing platforms, trimming improved the mean quality scores of trimmed sequences. Using trimmed sequences for De-novo and reference-based assembly improved assembly quality as well as assembler performance.

Nathaniel McVicar et al., in [20], present a flexible and fast FPGA-based short read alignment tool. Their aligner provides a speedup of 5.6x over BWA-SW with energy savings of 21%, while also reducing incorrect short read classification by 29%. They also offer optimizations with which the speedup can be increased to 71.3x, while still enjoying a 28% incorrect classification improvement and 52% improvement in unaligned reads.

Another one task that we may take into account is the error correction that must done after the sequence's generation. In April of 2010 we have a Parallel Algorithm for Error Correction in High-Throughput Short-Read Data on CUDA-Enabled Graphics Hardware where they present a scalable parallel algorithm for correcting sequencing errors in high-throughput short-read data with numerous speedups in their results [26]. They proesent that by using a CUDA-enabled mass-produced GPU, their results are in speedups of 12-84 times for the parallelized error correction, and speedups of 3-63 times for both sequential preprocessing and parallelized error correction compared to the publicly available Euler-SR program.

Finally, we can mention the growing involving of Microprocessors & Hardware Laboratory of TUC [21] which has present a numerous work on Genome Assembly and on Genome processing with many diploma thesis implemented of its students.

### 2.6 Scientific Contributions

During the 1950s, when the birth of modern molecular genetics happened, started the need of exploration of genes, heredity and the structure of DNA, the genetic information of all matter. In 1952, Alfred Hershey and Martha Chase proved that DNA was the molecule of heredity and James Watson, Francis Crick, Maurice Wilkins and Rosalind Franklin solved the three-dimensional structure of DNA with the double helix shape. From that point and till today, many scientific contributions have solve a big amount of the life questions, about what the genetic information of matter is and from what specific terms the life is configured and dependent.

Passing the years, one big problem was the inability to read genome sequences, because the large amount of the bases involved. Then, during the late 1960s and early 1970s, the combined work of several groups of researchers (Meselson & Yuan, 1968; Jackson et al., 1972; Cohen et al., 1973), helped in this problem by using DNA cut techniques at specific sites and spliced with DNA from other species. In that way started the mapping of genes where Mr. Francis Collins was the leader one, in 1980s, discovering the location of three important disease genes. After that, by the late 1980s, multiple approaches for sequencing DNA were in use and this all began to change with the work of National Institutes of Health (NIH) scientist J. Craig Venter. He started in his laboratory the genome sequencing by combine multiple sequencing techniques and he managed to sequence a big amount of genomes, with some missmatches, about 2000 whole genomes, which was as many as had been sequenced in the entire world to that point. Combine techniques seemed to work and was the start of what if follows [1]. Over the years, scientific discoveries that resulted from the application of next-generation DNA sequencing technologies, had their impact on the genome processing. Parallel platforms and new methods appear which works in a genome-wide scale with base precision and in this way these technologies brought enormous change in genetic and biological research. We have sequencing of RNA, serial analysis of gene expression (SAGE) and sequencing of ancient DNA samples as remarkable points in this point [19].

#### 2.6.1 Acceleration of Algorithms

Many researchers has try to implement and accelerate algorithms and tasks of bioinformatic field. These implementations have much of them a hardware implementation and more specifically an FPGA implementation. A Field-programmable gate array board (FPGA) is an integrated circuit designed to be configured by a customer or a designer after manufacturing and give the benefit to the programmer to make his own spatial allocation and try to accelerate an algorithm with much of optimizations in the design. Many of the design techniques and more information about these works can be found on the "Architecture Exploration of FPGA Based Accelerators for BioInformatics Applications" book from Springer Singapore [38]. An FPGA based acceleration work done from Steven Derrien and Patrice Quinton [10]. They implemented a new parallelization scheme for the hmmsearch function of the HMMER software, which is used for searching sequence databases for sequence homologs and for making sequence alignments [15]. In advance, we have the publish of Parallel accelerators for GlimmerHMM bioinformatics algorithm from Nafsika Chrysanthou et.al. researchers of our institute, the Technical University of Crete [7]. They managed to take speedups up to 200x for the FPGA-based system and up to 34x for the GPU-based system for the most compute intensive part of the algorithm. In conclusion we can present the paper of Reconfiguring the Bioinformatics Computational Spectrum: Challenges and Opportunities of FPGA-Based Bioinformatics Acceleration Platforms from a group of authors, including my diploma thesis supervisor Pr. A. Dollas, where they conducts a detailed survey on the use of FPGA-based reconfigurable computing platforms for a wide range of sequence and structural bioinformatics applications, with emphasis on performance and energy savings of the underlying architectures [9].

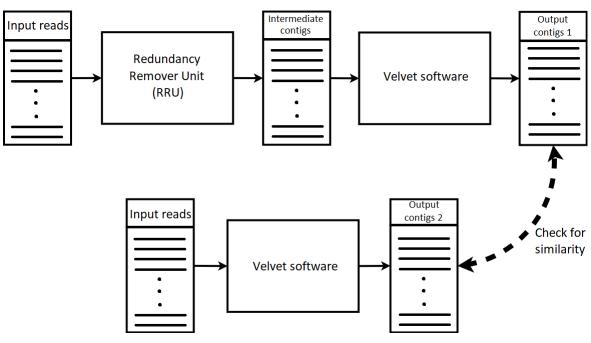

### 2.7 Motivation and our approach

In my diploma thesis we studied many different techniques and ended up to the paper of FAssem : FPGA based Acceleration of De Novo Genome Assembly [39]. This general study refers to a FPGA based Acceleration of De Novo Genome Assembly and in this particular part refers to achieved speedups over software implementations using FPGA-based accelerators. They implemented an application that use a parallel hardware implementation to make a redundancy job in the reads in the input data and they build the consensus sequences from the outputs of this design by using the de Bruijn graph-based Velvet software. So they implemented a Redundancy Remover Unit (RRU) in FPGA which acts as preprocessor and generating the input of Velvet genome assembler. The basic logic about this RRU preprocessor is to takes the input reads, find for matches between the reads and generating the output in order to give it as input in Velvet software to generate the final contigs. In contrast they pass the input reads as it is in Velvet software and taking the output contigs to check the similarity between these two outputs to examine the efficiency of the implementation. This processes appear in figure 2.4 with the two data-paths generating the two outputs.

They implemented and ran their design in an Alpha-Data board having Xilinx Virtex-6 (XC6VSX475T) FPGA with speed-grade 1 [40]. They implemented a kernel of this accelerator and named it Process Element (PE). In order to take speedup they implemented a multi-instance of PEs. As they present they managed to fit a multi-instace of 15 PEs in this specific FPGA board and they present an estimation of the speedups up to 13x faster in terms of 300 PEs. They present generally estimated speedups with different multi-PEs instances with 30,300,1000 and 3000 PEs.

Generating output sequence with RRU

Generating output sequence without RRU

FIGURE 2.4: Generation of two outputs sequences.

The main differences with their approach has to do with the hardware implementation. The first main difference is that we implemented a single kernel design, on the contrary of their multi-PEs design, so lower level of parallelism but in conclusion we saw average similar speedups and output's similarity rates thanks to next generation FPGA board. The second difference has to do with the internal hardware logic where we eliminated a stage that we ended up that it does not give any advantage in the process. In order to evaluate the results, with respect to performance and results' quality, of our work we utilized Velvet as well. About these differences we speak more specific in Chapter 3 and 4.

#### 2.7.1 Amdahl's law and theoretical parallel speedup

The theory of doing computational work in parallel has some fundamental laws that place limits on the benefits one can derive from parallelizing a computation work. To understand these laws, we have to first define the objective. In general, the goal in large scale computation is to get as much work done as possible in the shortest possible time within our budget. According to the Amdahl's law there is a upper limit about the gained speedup for each computational work. This is in almost all cases the best speedup one can achieve by doing work in parallel.

In our results that will be detailed presented in Chapter 4, we have the software execution times for our RMF design. For the processing stage of the RMF, which is the one that take the most execution time, we can compute an upper limit of possible speedup. This stage is an independent stage from the I/O operations, throw the RMF datapath, does not include dependencies between variables and we can have more than one (1) instances of this for parallel processing. In this point of view we can assume that this processing stage is a parallelizable stage.

Assuming the execution time of the processing stage as Tp and the overall RMF execution time (including I/O operations) as To we can calculate the percent of the overall RMF's execution time, which the processing stage occupies and we have the following table 2.1 for our datasets:

| Dataset          | Size  | Execution time in sec |         | Percent of       |

|------------------|-------|-----------------------|---------|------------------|

|                  | in Kb | Тр                    | То      | processing stage |

| Pyruvatibacter   | 3291  | 86,71                 | 87,27   | 99,3%            |

| Pseudomonas      | 6689  | 174,8                 | 175,96  | 99,3%            |

| Aythya           | 11749 | 312,72                | 314,78  | 99,3%            |

| Melopsittacus    | 22887 | 625,41                | 629,65  | 99,3%            |

| Photinus Piralis | 70234 | 1985,71               | 1997,87 | 99,4%            |

TABLE 2.1: The percentage of the overall RMF's execution time, which the processing stage occupies.

As we observe the percentage of the execution time of the most computational expensive part, the processing stage of the RMF, is about 99,3-99,4%. This means that there is no I/O bottleneck in RMF, as the processing stage is an independent stage from read and write stages. According to Amdahl's law if we assume the percentage of the processing stage as f the possible upper speedup that we can gain is:

$$1 \div (1 - f)$$

So, we have the below maximum theoretical possible speedups concerning these percentages:

| Dataset          | Size  | Percent of       | Maximum possible |

|------------------|-------|------------------|------------------|

|                  | in Kb | processing stage | speedup          |

| Pyruvatibacter   | 3291  | 99,3%            | 142,8x           |

| Pseudomonas      | 6689  | 99,3%            | 142,8x           |

| Aythya           | 11749 | 99,3%            | 142,8x           |

| Melopsittacus    | 22887 | 99,3%            | 142,8x           |

| Photinus Piralis | 70234 | 99,4%            | 166,6x           |

TABLE 2.2: Maximum theoretical possible speedups.

This implementation can achieve significant speedups according to the previous profiling and as it can easily be configured to run in a modern FPGA, we concluded to implement this design in order to get the results using a next generation FPGA. As we see in Chapter 4, we finally achieve speedups

32

up to 45x for our initial implementation. The differences between the maximum theoretical speedup and the gained speedup lead to the conclusion that the RMF has room for improvement. On the other hand we gain significant speedups and both for RMF design and for the whole assembly processing.

After that first theoretical speedup calculation and as we take our first software only execution time measurements from the whole assembly processing (including Velvet), we calculate, in the same way with above, the overall maximum theoretical speedup that the process can achieve. First, assuming again as Tp' the execution time of the processing stage of the RMF and as To' the overall execution time of the whole process including RMF and Velvet, we have the following table 2.3:

| Dataset          | Size  | Executio | n time in sec | Percentage of    |

|------------------|-------|----------|---------------|------------------|

|                  | in Kb | Тр′      | To'           | processing stage |

| Pyruvatibacter   | 3291  | 86,71    | 125,94        | 68,8%            |

| Pseudomonas      | 6689  | 174,8    | 232,81        | 75%              |

| Aythya           | 11749 | 312,72   | 516,96        | 60%              |

| Melopsittacus    | 22887 | 625,41   | 1065,13       | 58%              |

| Photinus Piralis | 70234 | 1985,71  | 6354,03       | 31,2%            |

TABLE 2.3: The percentage of the entire assembly process' execution time if we do not account for the RMF.

As we observe the percent of the execution time of the processing stage throw the whole assembly process (RMF+Velvet), is different depending the file size. Like the previous calculations if we assume as f' these percentages and by taking the Amdahl's law we can calculate the maximum theoretical speedup that we can gain in the entire assembly process if we manage to implement the processing stage of the RMF in parallel implementation. These speedups are tabulated in the table, below 2.4:

| Dataset          | Size Percentage of |                  | Maximum possible |  |

|------------------|--------------------|------------------|------------------|--|

|                  | in Kb              | processing stage | speedup          |  |

| Pyruvatibacter   | 3291               | 68,8%            | 3,2x             |  |

| Pseudomonas      | 6689               | 75%              | 4x               |  |

| Aythya           | 11749              | 60%              | 2,5x             |  |

| Melopsittacus    | 22887              | 58%              | 2,38x            |  |

| Photinus Piralis | 70234              | 31,2%            | 1,45x            |  |

TABLE 2.4: Maximum theoretical possible speedups of the entire process.

So we can gain a possible maximum speedup up to 4x if we manage to parallelize the execution of the processing stage of the RMF. In our initial implementation, we finally managed to gain a maximum speedup up to 3,61x and by making further improvements in the design we manage to increase this speedup as we will see in Chapter 4. In these speedups we have include all the I/O operations and the results are very encouraging in order to make sense to implement the RMF.

This speedup is a significant speedup in the whole assembly process and this drove us to implement RMF. Apart from this, the software implementations of these preprocessing stages like RMF, are very slow and not useful in the whole assembly process (and are not used from genome assemblers). For that reason the hardware implementation of them becomes necessary in order to executed in parallelism and by that way to reduce the execution time at all.

We are targeting a state of the art FPGA platform that lead to a different architectural implementation in order to take advantage of the characteristics of the new platform, with respect to both I/O capabilities and hardware resources. Apart of these, this is a design that can easy get optimizations and parallelism and we continue in the logical design implementation of this. The hardware implementation, which consist of subsystems easy to implemented in hardware, can easily synthesized and designed.

## Chapter 3

## **Reads Matching Filter**

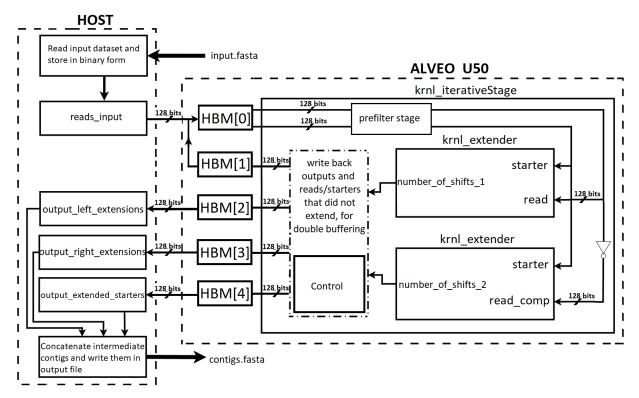

In this chapter we intend to describe the implementation of the Reads Matching Filter (RMF) of our approach and the differences it have with the paper's one which we motivated. In section 3.1 we have the software implementation with the algorithm and the processes we made and in section 3.2 we have the hardware implementation of the most computing expensive stage of our filtering and all the optimizations that we made in order to speedup the process. In hardware implementation we used the Vitis unified software platform [36] from Xilinx [41], where we build our project, with the functions that reads the input file and writes in output file runs in software mode in the host and all the matching job between the reads done in hardware kernel on the FPGA. The general filtering divided into three main stages which they presented in detail below.

#### 3.1 Software initial implementation

The Reads Matching Filter (RMF) is divided into three main stages. The first one is the preprocessing stage, where we read and store the input dataset in RAM, the second one is the process of the matching between all the reads and the last stage where the intermediate contigs generated. Here we can mention that because the length of the reads (60,70 bases per read), to have variables to store and process them, we can not use typical variables to store our data. We use Arbitrary Precision Data Types (ap\_int.h) library and in this way we can manage the bit-width of the integer numbers within the boundaries of the specified width [37].

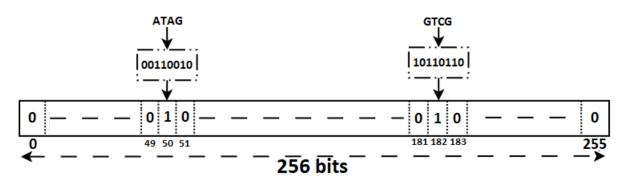

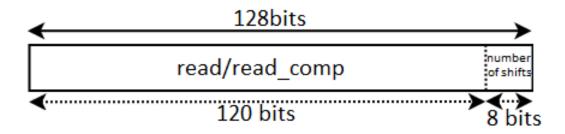

In the first stage we have to read the input file (FASTA format), line by line as reads, converting the DNA bases into binary form and store them in RAM in 128bits entries (ap\_uint<128> type, where an 60-bases read stored in 120 MSBs (Most Significant Bits)), to take advantage of the access speed. It is more useful and much more faster to work on the RAM despite the hard drive and this helps us in this stage, on execution time. The conversion in binary form done according to the conversion formula of the bellow table 3.1.

This conversion is useful because considering of a DNA base (A,T,C,G), which is a 8 bit character variable, after conversion in 2 bits we reduce the space that

| DNA base | Binary form |

|----------|-------------|

| A        | 00          |

| Т        | 11          |

| С        | 01          |

| G        | 10          |

TABLE 3.1: The conversion formula of DNA bases

dataset occupies in RAM to 25 percent of the original space, because in this 8 bits variable can be stored 4 different bases. In this way an 60 bases read can be stored in 120 bits by this conversion against of  $60 \times 8 = 480$  bits in character variables. Each read stored in RAM in 120 bits variables until no read remained in dataset.

The time this process done, we continued to the next stage, the matching stage. We take all the dataset's reads that had been stored in RAM and try to find matches between them in order to remove the presented redundancy. This stage returns 3 vectors of data for each dataset, 1 for left extensions, 1 for right extensions and 1 for the starters that took part in each comparison, included the number of bases that done the extensions. This process and the returned values of it will be further described below.

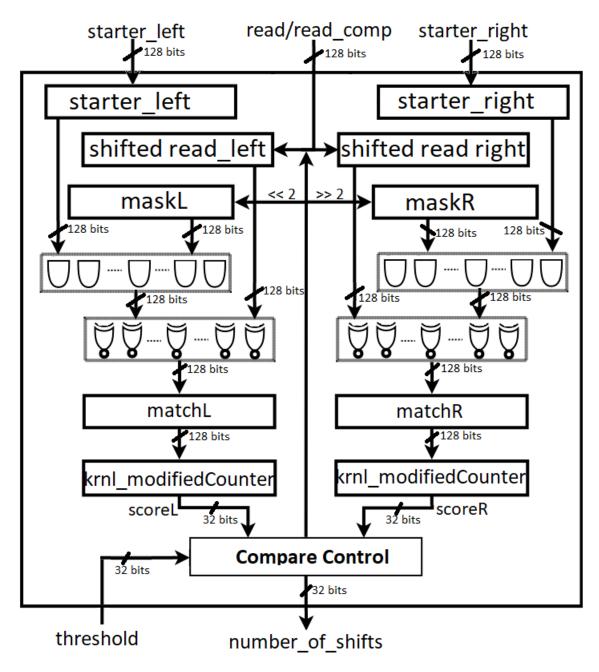

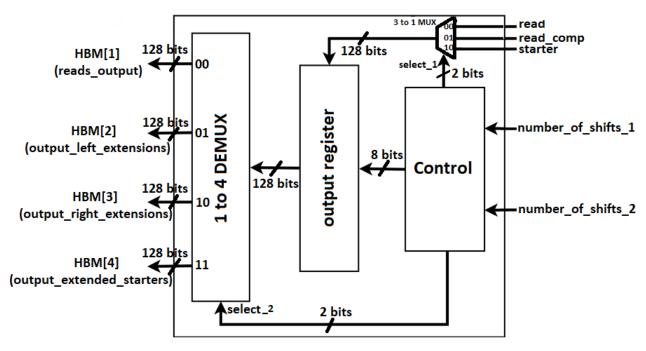

This part is the most expensive part in terms of CPU and RAM usage and for that reason it takes the most time of execution. If we suppose a dataset of N lines, we take N reads as starters and each of this starters matched with other N-1 ( $\approx$  N) reads in order to throw the redundancy process of the reads. This iterations phase, which consist of  $N^2$  matching combinations in worst case (O( $N^2$ )), can be accelerating from a FPGA implementation in order to redeem significant space and time reductions in complexity.