### TECHNICAL UNIVERSITY OF CRETE

MASTER OF SCIENCE THESIS

### A Heterogenous System Approach To The RealTime Stereo Problem

Author: Yiannis Agadakos Supervisor: Dr. Yiannis PAPAEYSTATHIOU

A thesis submitted in fulfilment of the requirements for the degree of Master of Science

$in \ the$

Microelectronics Hardware Laboratory Electronic and Computer Engineering

September 2013

## **Declaration of Authorship**

I, Yiannis AGADAKOS, declare that this thesis titled, 'A Heterogenous System Approach To The RealTime Stereo Problem ' and the work presented in it are my own. I confirm that:

- This work was done wholly or mainly while in candidature for a research degree at this University.

- Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated.

- Where I have consulted the published work of others, this is always clearly attributed.

- Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work.

- I have acknowledged all main sources of help.

- Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself.

Signed:

Date:

"Imagination is more important than knowledge. For knowledge is limited to all we now know and understand, while imagination embraces the entire world, and all there ever will be to know and understand." Albert Einstein.

### UNIVERSITY NAME (TECHNICAL UNIVERSITY OF CRETE)

### Abstract

### Electronic and Computer Engineering

Master of Science

### A Heterogenous System Approach To The RealTime Stereo Problem

by Yiannis Agadakos

The time of monolithic devices is soon to end as the demand for innovative applications increases and sophisticated technologies like augmented reality come to be. A hard constraint for such technologies is immense processing power, while also operating under real time constrains, conventional systems and software principles fail to win the challenge. However a new era of embedded devices is dawning as heterogeneous systems become readily available, the power hidden inside these tiny giants can bring applications previously unthought of within our grasp. By applying distributed embedded software engineering and following the principles of heterogeneous systems we have created a novel system that can solve the Stereo Vision challenge in Real Time with more than 40FPS in QVGA and with less than 2 Watts total power consumption while at the same time performing feature detection, furthermore the proposed architecture allows the same system to be used for any processing intensive work where parallel calculation is required, such as signal processing, by exploiting our novel client-server system developed. Lastly the design and implementation principles used and proposed in this thesis foresee and support the cooperation with a higher level of heterogeneous systems with more processing units such as the OpenCL enabled GPUs, soon to come. The proposed system can satisfy some of the most demanding processing requirements in real time, opening the door to applications previously available only to workstation machines.

## A cknowledgements

This work would have been infinitely more difficult without the guidance and tutorship of my supervisor Dr. Yiannis PAPAEYSTATHIOU and my colleague Konsantinos Makantasis MSc, whose expertise in Computer Vision proved invaluable. ...

# Contents

| Declaration of Authorship |                   |         |                                                                                 | i  |  |

|---------------------------|-------------------|---------|---------------------------------------------------------------------------------|----|--|

| A                         | Abstract          |         |                                                                                 |    |  |

| A                         | cknov             | wledge  | ments i                                                                         | v  |  |

| Li                        | List of Figures v |         |                                                                                 |    |  |

| List of Tables            |                   |         |                                                                                 | ix |  |

| A                         | bbre              | viation | s                                                                               | x  |  |

| 1                         | Intr              | oducti  | on                                                                              | 1  |  |

|                           | 1.1               | Introd  | uction                                                                          | 1  |  |

|                           | 1.2               | Goal    |                                                                                 | 3  |  |

|                           | 1.3               | Backg   | round                                                                           | 3  |  |

|                           |                   | 1.3.1   | Computer Vision                                                                 | 3  |  |

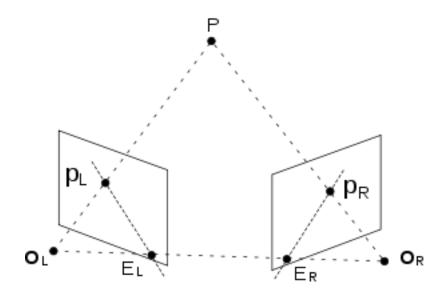

|                           |                   |         | 1.3.1.1 Stereo Vision                                                           | 4  |  |

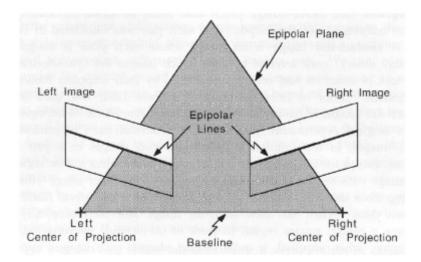

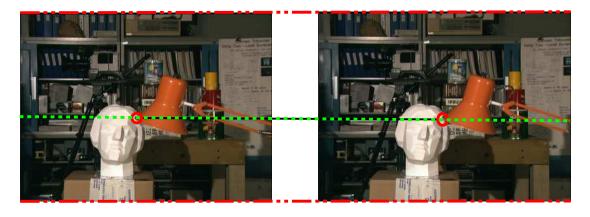

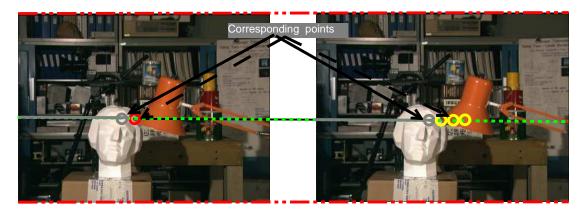

|                           |                   |         | Epipolar Geometry                                                               | 4  |  |

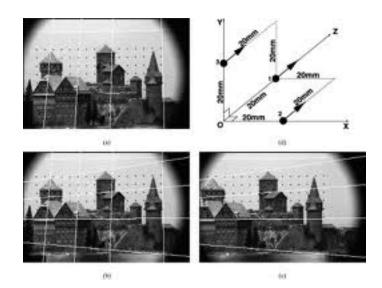

|                           |                   |         | Epipolar Constraint                                                             | 6  |  |

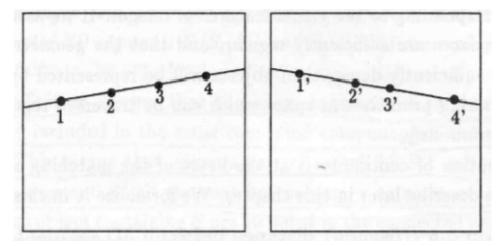

|                           |                   |         | Monotonicity and Uniqueness Constraint                                          | 6  |  |

|                           |                   | 1.3.2   | Embedded Systems                                                                | 8  |  |

|                           |                   |         | 1.3.2.1 Real Time                                                               | 9  |  |

|                           |                   |         | FPGA                                                                            | 9  |  |

|                           |                   |         | DSP                                                                             | 0  |  |

|                           |                   |         | $\mathbf{GPP}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ | 0  |  |

|                           |                   |         | ASIC                                                                            | 1  |  |

|                           |                   | 1.3.3   | Summary                                                                         | 1  |  |

| 2                         | Arc               | hitectu | ire 12                                                                          | 2  |  |

|                           | 2.1               | Relati  | ve Work                                                                         |    |  |

|                           |                   | 2.1.1   | Embedded Universe 12                                                            | 2  |  |

|                           |                   | 2.1.2   | FPGA based 13                                                                   | 3  |  |

|                           |                   | 2.1.3   | ASIC                                                                            | 3  |  |

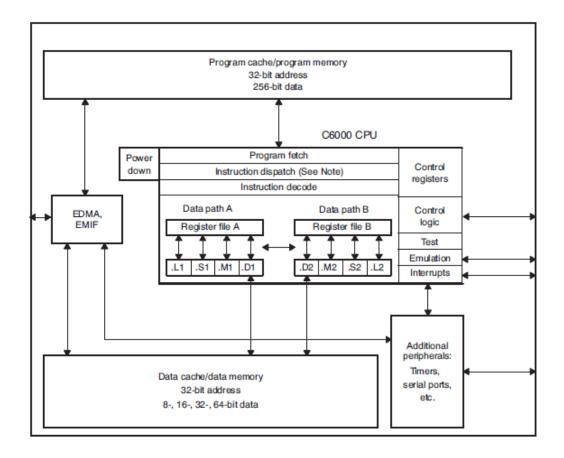

|   |     | 2.1.5 | DSP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---|-----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |     | 2.1.6 | Heterogeneous Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   |     | 2.1.7 | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

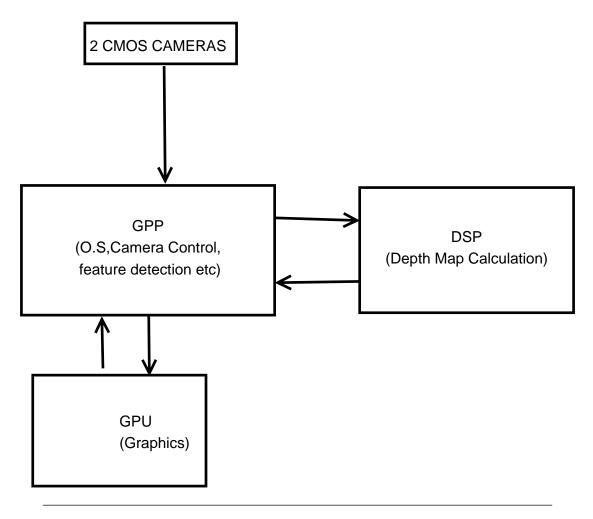

|   | 2.2 | Our A | pproach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|   |     | 2.2.1 | Initial Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   |     | 2.2.2 | Assumptions and Theory boosts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   |     |       | Epipolar Constraint                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   |     |       | Monotonicity Constraint                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

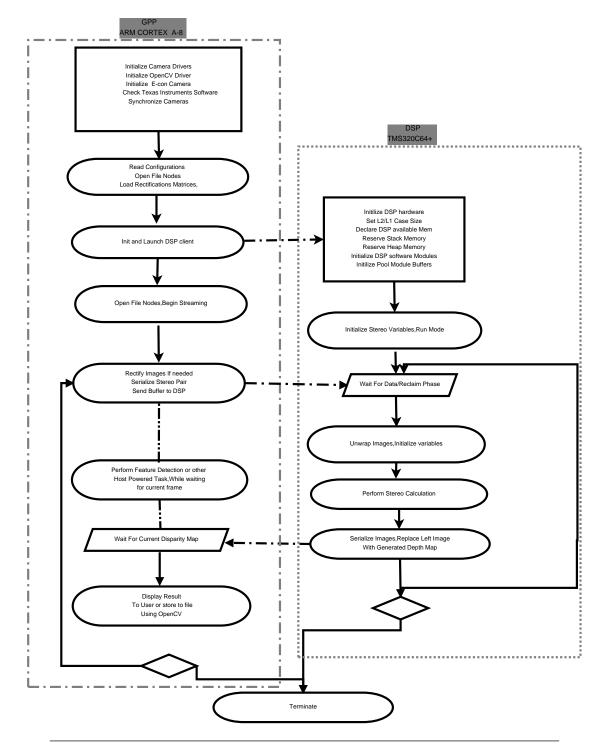

|   |     | 2.2.3 | GPP Side                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|   |     | 2.2.4 | DSP Side                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|   |     | 2.2.5 | Assembling the Puzzle 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3 | Imr | lemen | tation 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Č | 3.1 |       | uction $\ldots \ldots 23$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   | 0.1 | 3.1.1 | GPP Implementation Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   |     | 3.1.2 | DSP Implementation Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   | 3.2 | GPP   | 257 Implementation eventies a construction of the second se |

|   | ··- | 3.2.1 | Tools and Frameworks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   |     | 3.2.2 | Tests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   |     | 3.2.3 | Optimizations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   | 3.3 |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|   |     | 3.3.1 | Tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   |     | 3.3.2 | Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   |     |       | 3.3.2.1 MexFile                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|   |     | 3.3.3 | Amdahl's Law                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|   |     |       | 3.3.3.1 Window Impact                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   |     |       | 3.3.3.2 Maximum Disparity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

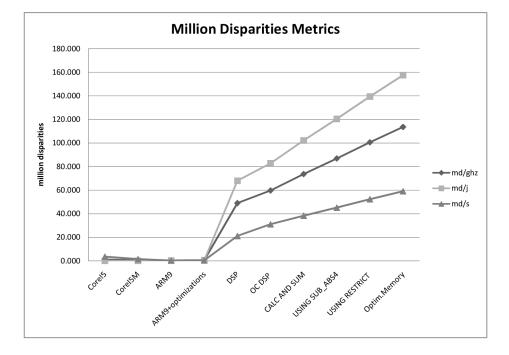

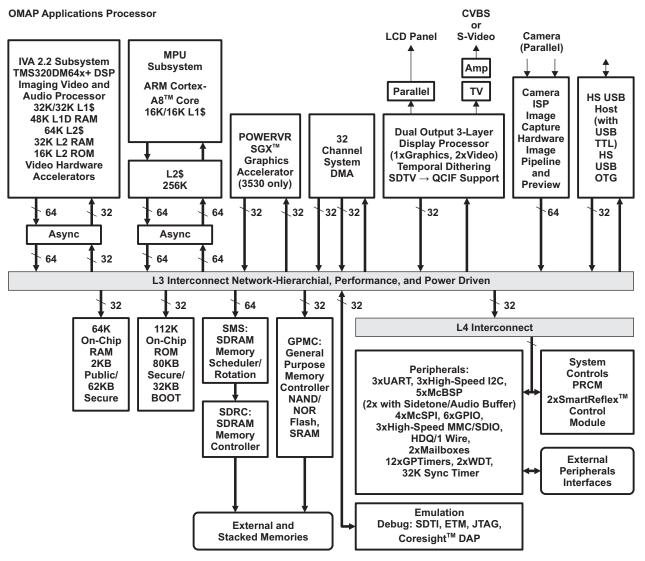

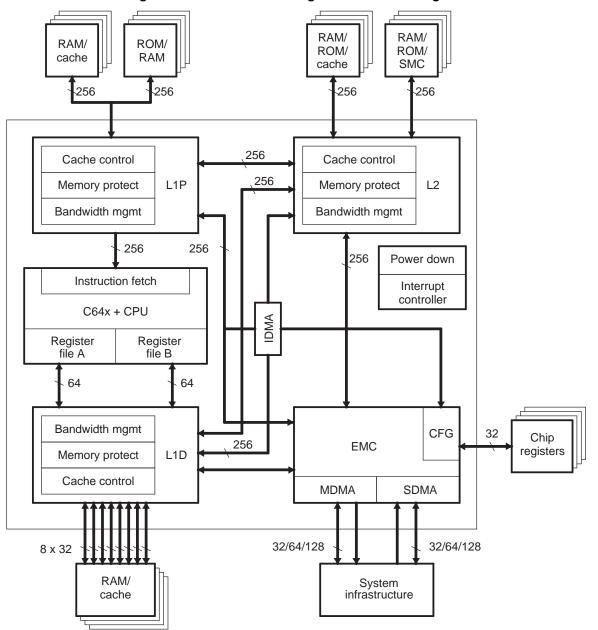

|   |     | 3.3.4 | OMAP3530                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|   | 3.4 | Optim | $izations \ldots 41$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|   |     | 3.4.1 | Platform independent optimizations- general principles 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   |     |       | 3.4.1.1 Disparity-Window Choice                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|   |     |       | 3.4.1.2 Compiler optimizations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

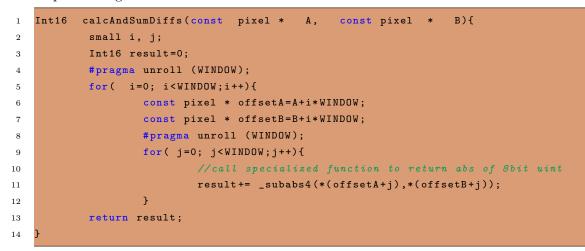

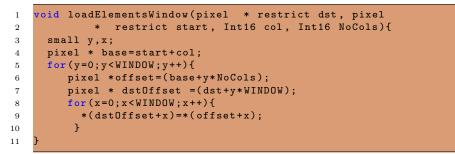

|   |     |       | 3.4.1.3 Optimized image data serialization and Loop Unrolling . 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|   |     |       | 3.4.1.4 Memory Copy Impact                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

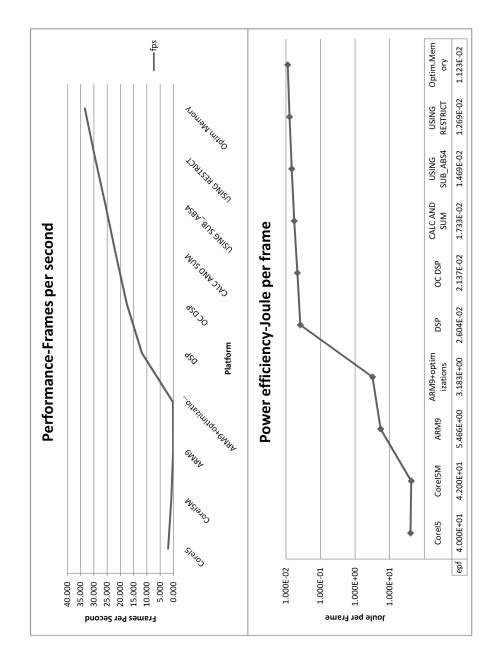

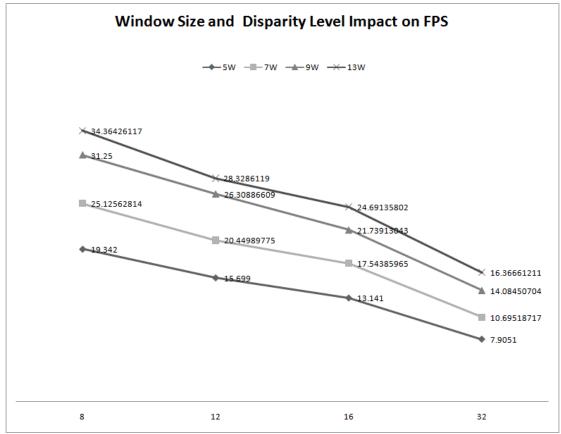

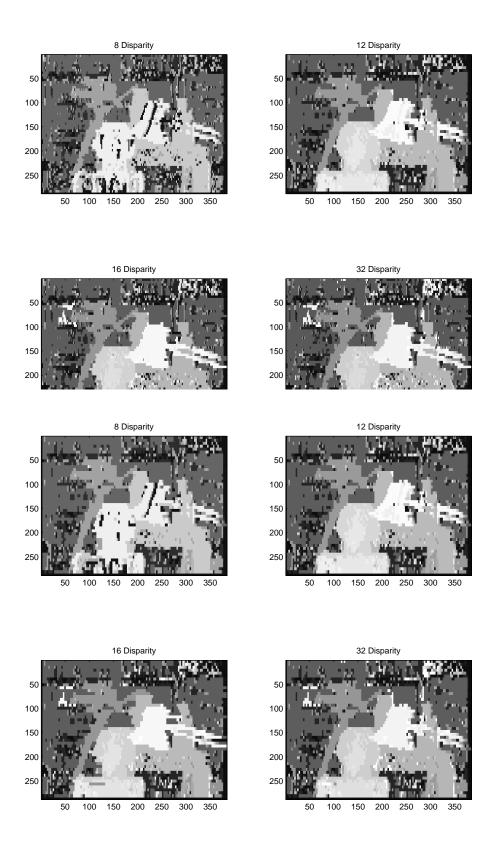

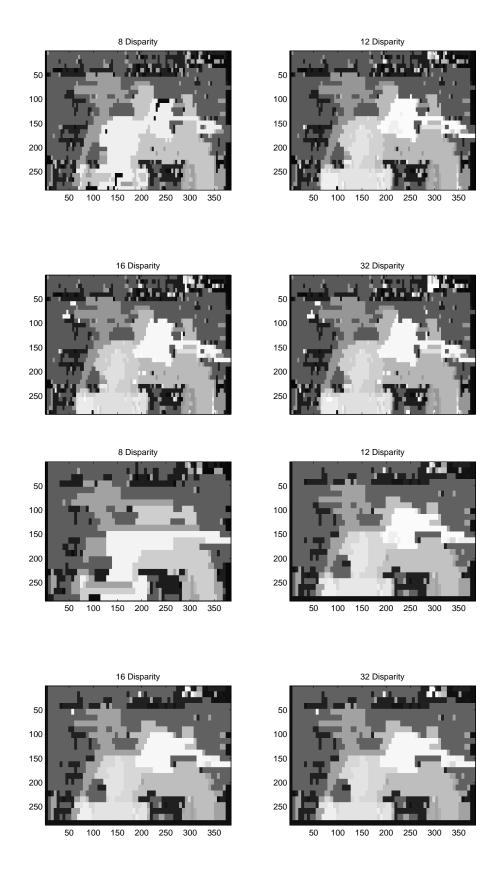

|   |     |       | 3.4.1.5 SAD on one step $\ldots \ldots \ldots \ldots \ldots \ldots \ldots 43$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |