# **TECHNICAL UNIVERSITY OF CRETE** ELECTRONIC AND COMPUTER ENGINEERING DEPARTMENT

# Thesis:

# Design and Implementation of a Network Processor Input/Output Module

# **By Ioannis Sourdis**

Members:

Professor Apostolos Dollas Assistant Professor Georgios Stamoulis

CHANIA, FEBRUARY 2002

...στους γονείς μου.

...στην Κορίνα.

...στη Χριστιάνα.

Γιάννης Σούρδης

# Ευχαριστίες

Για την ολοκλήρωση της διπλωματικής μου εργασίας θα ήθελα να ευχαριστήσω τον Μάρκο Κιμιωνή και όλους τους μεταπτυχιακούς και προπτυχιακούς φοιτητές του εργαστηρίου για τη βοήθειά τους.

Επίσης θα ήθελα να ευχαριστήσω για τη συνεργασία μας στο Protocol Processor Project τους Γιώργο Κωνσταντουλάκη, Φάνη Ορφανουδάκη, Κώστα Πραματάρη, Κυριάκο Βλάχο, Christoph Baumhoph, Νίκο Νικολάου, Στέλιο Περισσάκη, Prabhat Avasare, Jorge Sanchez, Νίκο Ζερβό και τα υπόλοιπα μέλη των συμμετεχόντων στο Pro3 (Lucent Technologies Nederland, Hyperstone Electronics, IMEC, Ellemedia Technologies και inAccess Networks, ΕΜΠ).

Ευχαριστώ ακόμη τα μέλη της εξεταστικής επιτροπής Γεώργιο Σταμούλη και Απόστολο Δόλλα για τη πολύτιμη βοήθειά τους.

Θα ήθελα ακόμη να ευχαριστήσω τον Αποστόλη Δημητρομανωλάκη και το Γιάννη Αικατερινίδη για τη βοήθειά τους.

Ευχαριστώ επίσης τον καθηγητή Απόστολο Δόλλα και τον Παναγιώτη Στογιάννο για το σημαντικό ρόλο που έπαιξαν στην απόφασή μου να ασχοληθώ με το Hardware!

Ακόμη ευχαριστώ το Διονύση Ευσταθίου και το Γιάννη Ζήση για την άριστη συνεργασία μας στα πλαίσια του ερευνητικού προγράμματος Pro3.

Τέλος θα ήθελα ιδιαίτερα να ευχαριστήσω τον επιβλέπων καθηγητή μου Διονύσιο Πνευματικάτο για τις χρήσιμες υποδείξεις και την άριστη συνεργασία μας.

# TABLE OF CONTENTS

| TABLE OF CONTENTS                                     | 3   |

|-------------------------------------------------------|-----|

| TABLE OF FIGURES                                      | 5   |

| ABSTRACT                                              | 7   |

| CHAPTER 1: INTRODUCTION                               | 8   |

| CHAPTER 2:NETWORK PROCESSING ARCHITECTURE ALTERNATIVE | S10 |

| 2.1 Efficient Data Processing                         | 12  |

| 2.1.1 Parallel Processing                             |     |

| 2.1.2 Pipelining                                      |     |

| 2.1.3 Specialized Instruction Sets or Units           | 15  |

| 2.2 Dealing with Memory Latency                       | 15  |

| 2.2.1 Multithreading                                  |     |

| 2.2.2 Memory Managers and Types of RAM                |     |

| 2.3 Examples of Network Processors                    | 16  |

| 2.3.1 Intel's IXP 1200                                |     |

| 2.3.2 MMC's Anyflow 5000, nP3400, nP7000              |     |

| 2.3.3 IBM's NP4GS3 "Rainier"                          |     |

| 2.3.4 Motorola/C-Port C-5                             | 20  |

| CHAPTER 3: PROTOCOL PROCESSOR PROJECT ARCHITECTURE    | 22  |

| 3.1 Protocol Processor Project (Pro <sup>3</sup> )    | 22  |

| 3.2 Functional architecture                           | 24  |

| 3.3 Physical architecture                             | 25  |

|                                                       |     |

| 3.4 Internal data paths                               |     |

| 3.4.1 IP Application                                  |     |

| 3.4.1.1 IP over SONET interface                       |     |

| 3.4.1.2 IP over ATM interface                         |     |

| 3.4.2 ATM application                                 |     |

| 3.5 Internal interfaces                               |     |

| 3.6 Re-configurable Pipelined Module (RPM)            |     |

| 3.6.1 Field Extractor                                 | 35  |

| 3.6.2 Protocol Processing Engine                      |     |

| 3.6.3 Field Modifier                                  | 39  |

| CHAPTER 4: PPE ARCHITECTURE                                 | 1 |

|-------------------------------------------------------------|---|

| 4.1 Modified Hyperstone RISC (MHY)                          | 1 |

| 4.2 RPM Glue Logic (RPG)4                                   | 8 |

| 4.3 Read/Write Control RAM (RWR)                            | 9 |

| CHAPTER 5: STATE BYPASS                                     | 3 |

| 5.1 Problem Definition                                      | 3 |

| 5.2 Bypass Logic                                            | 5 |

| 5.3 Bypass considering Pipeline                             | 8 |

| CHAPTER 6: RPG MICROARCHITECTURE60                          | 0 |

| 6.1 Data path                                               | 0 |

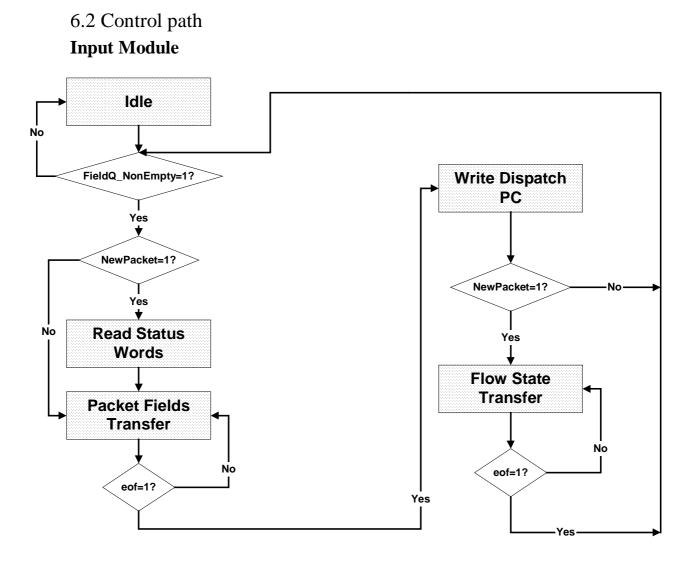

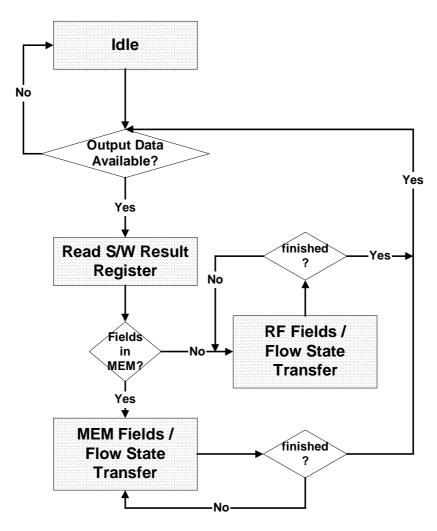

| 6.2 Control path                                            | 3 |

| 6.3 Read, Write and Process to RF                           | 8 |

| 6.4 Synchronization between Input, Output and MHY modules70 | 0 |

| 6.5 Pipeline Stall Mechanism - Backpressure7                | 1 |

| CHAPTER 7: PERFORMANCE EVALUATION                           | 2 |

| 7.1 Metrics                                                 | 2 |

| 7.2 Performance Results74                                   | 4 |

| 7.3 Overheads                                               | 6 |

| CHAPTER 8: IMPLEMENTATION AND VERIFICATION                  | 7 |

| 8.1 Techniques7'                                            | 7 |

| 8.2 Fallback module                                         | 3 |

| 8.3 Synthesis-Gatelevel Simulation                          | 5 |

| CHAPTER 9: CONCLUSIONS                                      | 9 |

| REFERENCES                                                  | 2 |

# TABLE OF FIGURES

| Figure 2a: Programmable processors vs. Dedicated hardware                                    | 10        |

|----------------------------------------------------------------------------------------------|-----------|

| Figure 2b: Evolving the Network Design System Philosophy                                     | 11        |

| Figure 2c: Graphical comparison between network processor-based systems and their hard       | lwired    |

| counterparts                                                                                 | 12        |

| Figure 2.1a: A Simple network Processing Engine Based on a Pipelined architecture            | 13        |

| Figure 2.1b: A Simple Network Processing Engine Based on a Parallel/Multiprocessor           |           |

| Architecture                                                                                 | 13        |

| Figure 2.1.1a: Parallel Processing                                                           | 14        |

| Figure 2.1.2a: Pipelining                                                                    | 14        |

| Figure 2.3.1a: Block Diagram of an Intel IXP 1200 Evaluation System                          | 17        |

| Table 2.3.1b: Intel IXP Network Processor Family Comparison                                  | 17        |

| Table 2.3.1c:Intel IXP 1200 Bus Speed and Bandwidth Comparison                               | 17        |

| Figure 2.3.2a: nP7510: OC 192c Network Processor                                             | 19        |

| Figure 2.3.3a: IBM's NP4GS3 "Rainier"EPC High-level Architecture. EPC Architecture,          | which     |

| shows how the EPC core is structured. Note that the Specialized PowerPC 405 engine           | called    |

| the ePPC (Embedded Power PC) resides here and can be used as the CP (Control pro             |           |

| in systems containing up to 2 NPs                                                            | 20        |

| Figure 2.3.4a: C-5 Network Processor Block Diagram.                                          |           |

| Figure 3.1a: Pro <sup>3</sup> Architecture                                                   | 23        |

| Figure 3.1b: Pro3 pipeline stages (Reception, Classification, State Processing and Transm    | ition) 23 |

| Figure 3.2a: PRO <sup>3</sup> functional architecture                                        | 24        |

| Figure 3.2b: Firewall for IP packets                                                         | 25        |

| Figure 3.2.a: PRO <sup>3</sup> physical architecture                                         | 26        |

| Figure 3.4.1.1a: Data flows for IP over SONET applications                                   | 29        |

| Figure 3.4.1.2a: Data flows for IP over ATM applications                                     | 31        |

| Figure 3.4.1.3a: Data flows for ATM applications                                             | 32        |

| Figure 3.5a: PRO <sup>3</sup> internal interfaces                                            | 33        |

| Figure 3.6a: The two RPMs in Pro <sup>3</sup>                                                | 34        |

| Figure 3.6b: RPM block diagram                                                               | 34        |

| Figure 3.6d: the vertical highlighted slice shows the pipelined operation, where A0 is proce | ssed in   |

| FMO, B0 is processed in PPE and C0 is processed in FEX                                       | 35        |

| Figure 3.6.2a: The Protocol Processing Engine                                                | 37        |

| Figure 3.6.2b: RPM's pipeline stages                                                         | 38        |

| Figure 4a: PPE location inside the RPM along with its main communication paths               | 41        |

| Figure 4.1a: IDLE, START, STARTACK synchronization                                           | 44        |

| Figure 4.1b: The grey boxes show the registers that carry flow state when GRSwitch [7 do     | wn to 2]  |

| = "100111"                                                                                   | 46        |

| Figure 4.1c: Register File Access                                                            | 47        |

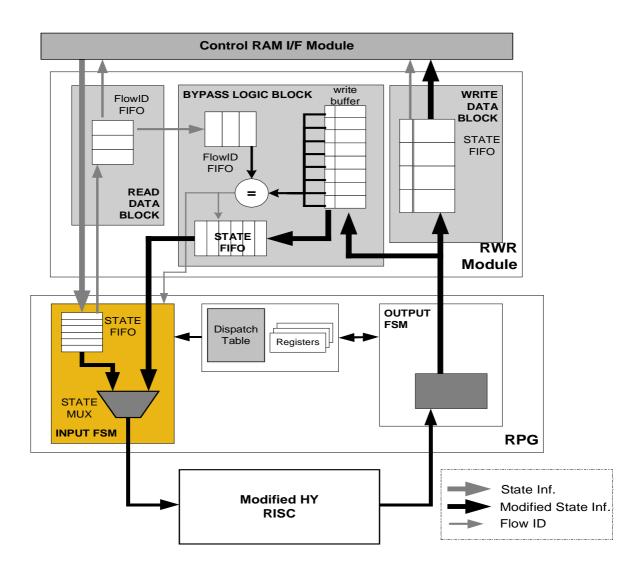

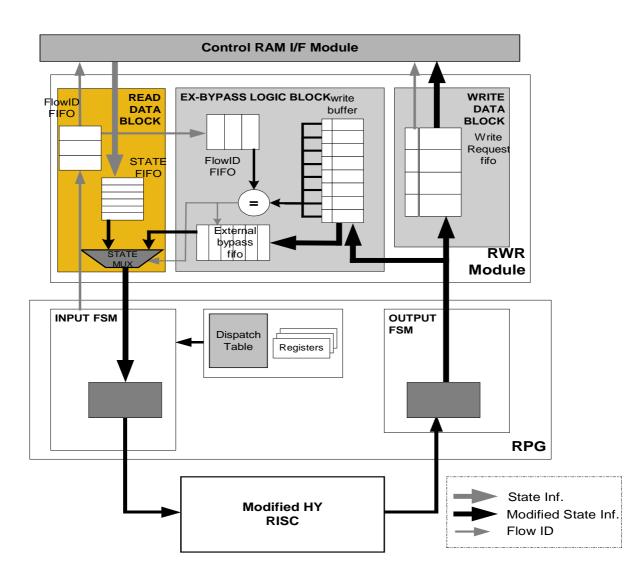

| Figure 4.3a: RWR block diagram                                                               | 51        |

| Figure 5.1a: no bypass case                                                                  | 54      |

|----------------------------------------------------------------------------------------------|---------|

| Figure 5.1b: bypass L1 – bypass L0                                                           | 55      |

| Figure 5.2a: the latest version of Flow State A already exists on G1 (registers 13,12,11 and | 10)56   |

| Figure 5.2b: the latest version of Flow State A already exists on G1 (registers 13,12,11 and | l 10)57 |

| Table 5.3a: bypass considering Pipeline                                                      | 59      |

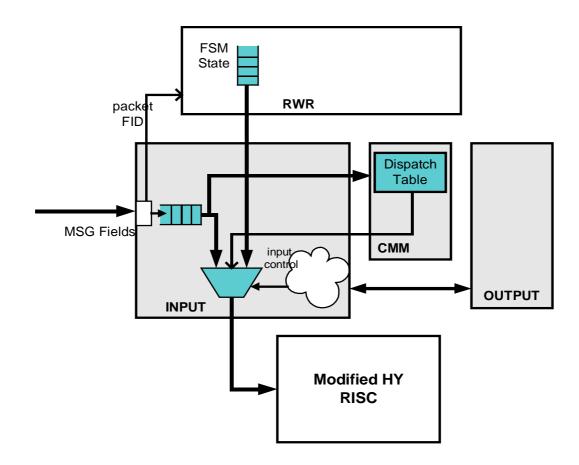

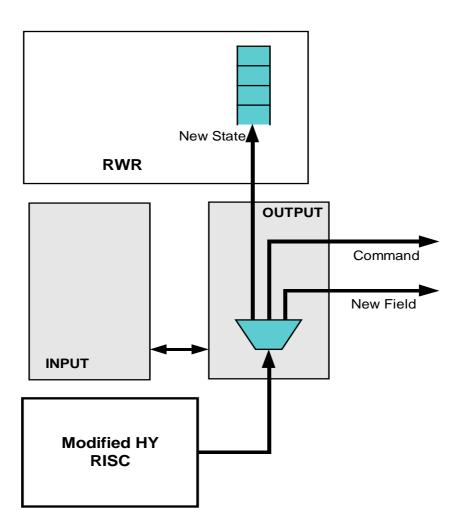

| Figure 6a: RPG Block Diagram                                                                 | 60      |

| Figure 6.1a: input module datapath                                                           | 61      |

| Figure 6.1a: input module datapath                                                           | 62      |

| Figure 6.1a: input FSM                                                                       | 63      |

| Figure 6.1b: output FSM                                                                      | 66      |

| Table 6.1c: software result register                                                         | 67      |

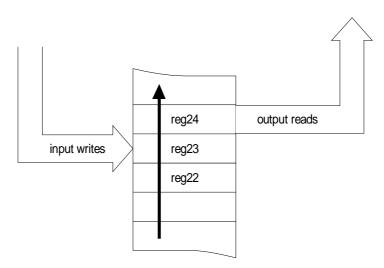

| Figure 6.3a: Read and Write to the same part of RF. Input FSM cannot write to reg24 before   | ore     |

| output FSM read it                                                                           | 69      |

| Figure 6.4a: Input-Output-MHY synchronization                                                | 70      |

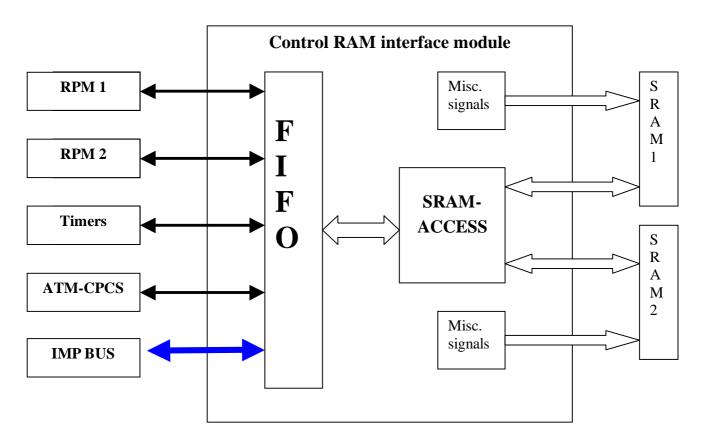

| Figure 7.1a: Control RAM Interface Module (CRIM) block diagram                               | 73      |

| Table 7.2a: Performance Results of 100.000 packets through PPE                               | 75      |

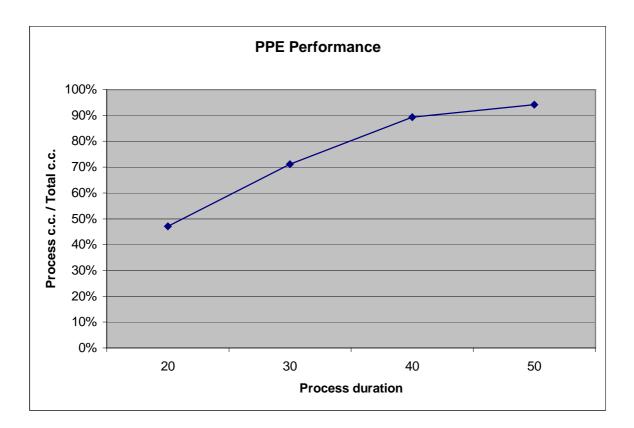

| Table 7.2b: Performance Results of 10.000 packets through PPE (changing process durat        | ion)75  |

| Table 7.2c: PPE Performance                                                                  | 76      |

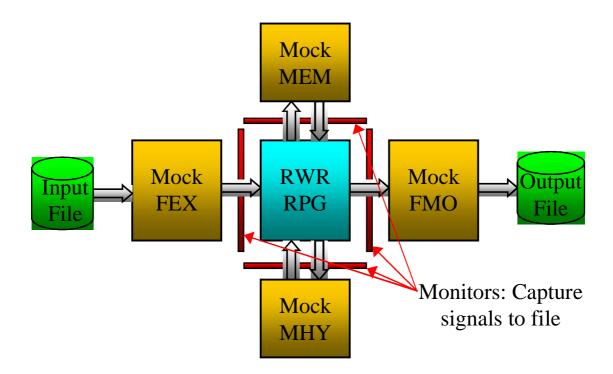

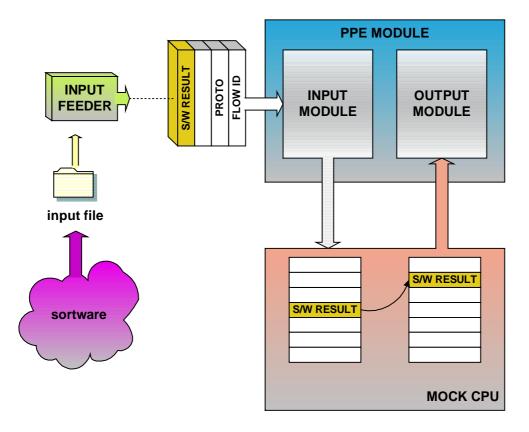

| Figure 8.1a: Test-bench using mock modules and monitors                                      | 77      |

| Figure 8.1b: mock CPU uses as software result word, a specified word, that input FSM         |         |

| transferred in RF                                                                            | 78      |

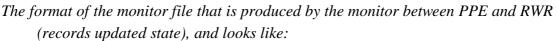

| Figure 8.1c: Test-bench using real RPM modules and monitors                                  | 80      |

| Figure 8.1d: Flow State Word format (only for debug)                                         | 81      |

| Table 8.2a: format of incoming and outgoing packets                                          | 84      |

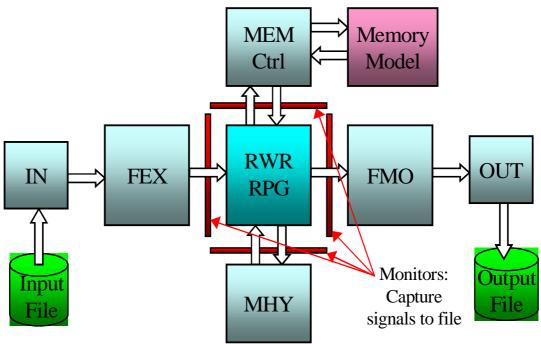

| Figure 8.2b: fallback module in PPE block diagram                                            | 85      |

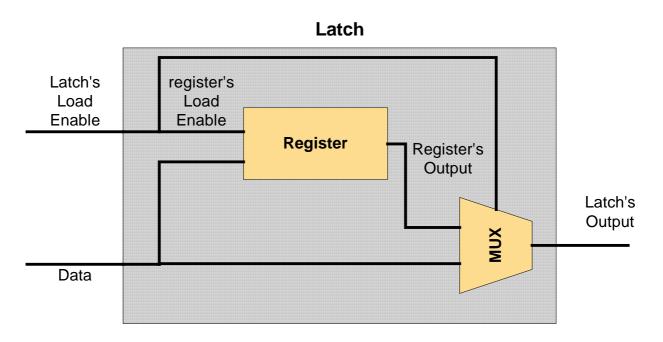

| Figure 8.3a: Latch using Register and Multiplexer 2x1                                        | 87      |

| Table 8.3b: simulation speed                                                                 | 88      |

| Table 8.3c: synthesis results                                                                | 88      |

| Figure 9a: Actual PPE block diagram                                                          | 90      |

| Figure 9b: PPE block diagram that should be designed                                         | 91      |

## Abstract

The rapid growth in the network sizes, the continuing trend for convergence of data, voice and video traffic and the tremendous growth in data traffic (particularly that associated with the Internet), has demanded the development and deployment of high-capacity telecommunication systems. Transmission lines with speeds of several Gigabits/sec are already available. To meet the protocol processing demands of the fast lines, we must employ high-performance protocol execution engines. A network processor aims in accomplishing wire-speed protocol processing, at a reasonable cost. The Protocol Processing Project (Pro3) aims in developing an integrated and affordable system, which is able to execute high-level telecom transport protocols (TCP/IP, Network Address Translation, Packet filtering, etc.) at wire speed. This thesis's goal is the design and implementation of the Protocol Processing Engine (PPE) module of Pro3. PPE interfaces the internal datapaths of Pro3 with the central processing core that executes the protocols. We organized PPE in a three-stage pipeline (input, process and output) in order to improve its performance. The pipeline processing of packets gives rise to data hazards that must be handled. The correctness of the design has been initially confirmed with "ad-hoc" testing. We then employed a systematic verification approach. First, we automatically generated input files and their corresponding results. Then, we performed simulations and finally automatically verified the simulation results against the expected ones. The Hardware Description Language (VHDL) source code of the design was compiled (synthesized using the Synopsys Design Compiler), and linked to a netlist, which was also verified using gate-level simulation. Each module was initially verified individually (functional and gate-level simulations), and then with its neighbouring modules, and finally with the rest of the Pro3 modules in chip-level simulations.

# Chapter 1: Introduction

The trend of data, voice and video traffic convergence and tremendous growth in data traffic, particularly that which is associated with the Internet, has prompted many discussions on the hardware and software needed for the future. Newer bandwidth-eager end-user software applications and faster processors in desktop and server systems are placing enormous demands on the current networking architecture. As a result, the network is evolving into a highly complex and sophisticated environment: networking bandwidth use continues to double every four months; guaranteed quality and priority customization is anticipated to all data, voice and video applications. The way telecommunication systems work is that networks run packets and software is the key in making networks work.

The rapid growth in the dimension of networks, along with the always-increasing user's demands for networking services, has imposed the development and deployment of highcapacity telecommunication systems. Such systems involve modules of high throughput, which have their time critical functions realized in application specific standard products. The power required for the processing of protocol functions at wire speed is usually obtained either by generic microprocessors or by Application Specific Integrated Circuits (ASICs). Both approaches have advantages and disadvantages. General-purpose microprocessors are designed to perform a variety of functions, but suffer from reduced performance. With time-to-market becoming the dominant force in the networking world, many companies have turned to Reduced Instruction Set Computing (RISC) technology. RISCs can execute their code very fast due to instructions simplicity, but since the decisions are made in software, the RISC is much slower than the ASIC. On the other hand ASICs are designed to meet a specific functional requirement with high efficiency, but are very difficult, if not impossible, to change once they have been designed or modified with a simple software upgrade (chapter 2). Another option is a hybrid approach. Microprocessors are inadequate in supporting the protocol processing requirements for the entire set of active sessions. This constitutes a major system resource bottleneck, because the complexity of the protocol algorithms requires higher computational power than that offered by today's processor technology [4, 17, 18, 19]. Hybrid approach combines both chip technologies, using a RISC processor as the central core, and ASICs to perform the specific tasks (Pro3 approach, chapter 3). These components called Network Processors have exhibited an enormous advance in the turn of the millennium. As for the higher layer protocol functions that are not performed at wire speed, often today, more than one high performance processing units are employed; these processing units include routing protocols, statistical compiling and reporting, error processing, connection admission control, network and transport layers protocol processing and traffic and resource management.

In the last few years, telecom industry has witnessed an enormous advance in processor technology, designs, capabilities and applications [4]. Because of their flexibility, general and

specialized processors are being developed by many industries. Powerful architectures (i.e. RISC), specialized processors, signal processors, graphics processors etc. are developed. *Network processing architectures* [7, 8, 9, 10, 11, 12, 13, 14] are also developed in order to achieve wire rate protocol processing.

Protocol Processing Project (Pro3) [5] is enhanced with hardwired functionality devoted to speed up low level streaming and networking operations. Pro3 has to do with the design and implementation of a network processor. It includes RISC processors and ASIC in a single chip, trying to perform in wire rates. Our design, input/output module of Pro3 network processor, is responsible of putting incoming packet information to a RISC core (protocol processor) and taking out updated packet information. Its goal is to improve performance of the Protocol Processing Engine (PPE) by creating a three stages pipeline (input, process and output).

Generally, the following pseudo code describes packet processing:

```

For each packet {

1. Identify connection ID (flow), packet classification

2. Get state information (i.e. last packet seen, etc.)

3. Consult selected fields (parts of header, body)

4. Execute protocol code on state and selected fields

5. Update (?) packet and flow state

6. Send (?) updated packet

7. Create (??) other control packets

}

```

When a packet arrives, network processor identifies its flow (packet classification). It obtains the flow state information for the corresponding flow. The flow state information consists of the data needed to correctly process an arbitrary packet of that flow. For example, flow state may include:

- The number of the last packet seen.

- The packets, which were transmitted, but are not yet acknowledged by the network processor.

- A list of timers' information (i.e. how long had it been since last packet arrived).

Protocol code is executed on flow state and selected fields. Packet fields that are needed for protocol processing are extracted to the modules that process protocols. Process results may be:

- Reject packet (firewall or there is acknowledgment that this packet has already got on its destination),

- Packet modification,

- Update flow state,

- Creation of additional control packets,

- Or combination of the above.

# Chapter 2:Network Processing Architecture Alternatives

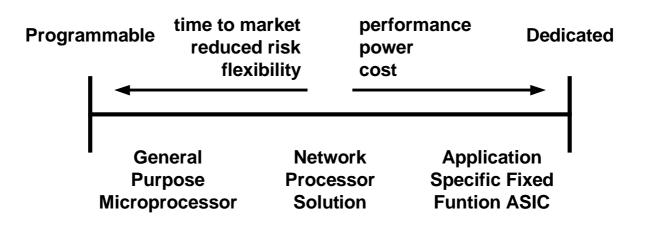

There are several different architectural solutions for packet processing. Each having some advantages and disadvantages. General-purpose microprocessors are used for their flexibility to adapt to protocol changes in the field and short time to complete the software development, but do not have enough performance to process data at wire rates. On the other hand, hardwired (custom) chips are designed to process packets at wire rates, but are not flexible. They are difficult and expensive to modify, to add features, fix bugs or adapt to rapidly changing network processors. Network processors are proposed as a solution to both these problems. They are processors optimized to perform packet processing at wire rates and are programmable and therefore flexible. There is a trade off between performance and flexibility in these three solutions (General-purpose microprocessors, Network processors, dedicated ASIC). General-purpose microprocessors are very flexible, but don't have enough performance, network processors are less flexible but have much better performance and finally, dedicated ASICs are not flexible but can perform at wire rates. This trade-off [16] is shown in figure 2a.

Figure 2a: Programmable processors vs. Dedicated hardware

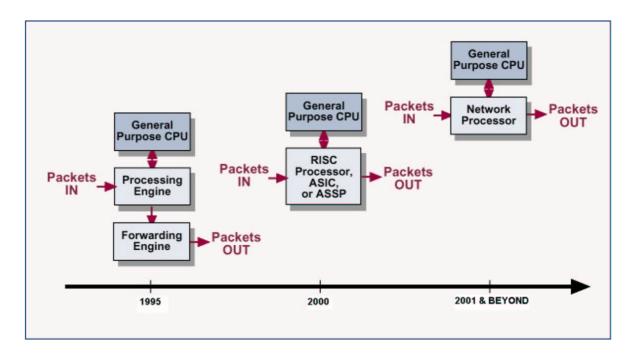

Through advances made in semiconductor technology, the philosophy of network system design has changed [21] (figure 2b). In 1995, networks employed traditional routing/switching devices, such as a general purpose CPU, a packet –processing engine, and a forwarding engine. By 2000, hybridized architectures were common. Such systems consisted of a general purpose CPU and a custom ASIC or an off-the shelf application- specific standard product (ASSP), or a combination of these devices. After 2001, technology-driven systems consist of a dedicated control CPU and a full-fledged application-specific network processor.

Figure 2b: Evolving the Network Design System Philosophy

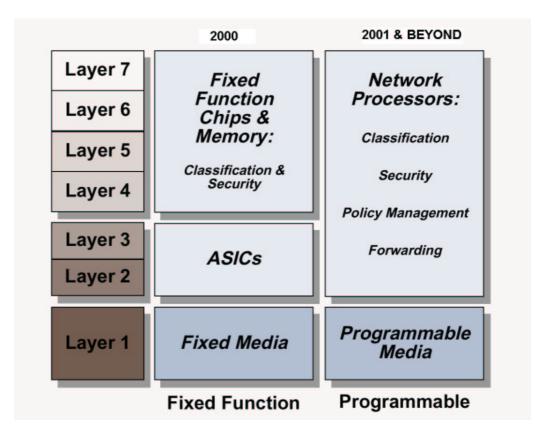

This migration of system architecture has also shifted Network Processing functionality from hardwired solutions to programmable solutions (figure 2c). Note the change from fixed to programmable media, as well as the change from ASIC/ASSP technology to a single-chip (Network Processor) solution.

The target of every network processor is to perform packet processing with the flexibility of a microprocessor, but with the performance of a dedicated ASIC. There are two issues that concern network processors' performance. The first one is packet (data) processing and alternative solutions that improve data processing performance [16]. Network processing requires transfer of packets and additional information to and from large memories with large access latency. Therefore, memory latency and the alternative ways [16] to "hide" it, is the second issue.

Figure 2c: Graphical comparison between network processor-based systems and their hardwired counterparts.

# 2.1 Efficient Data Processing

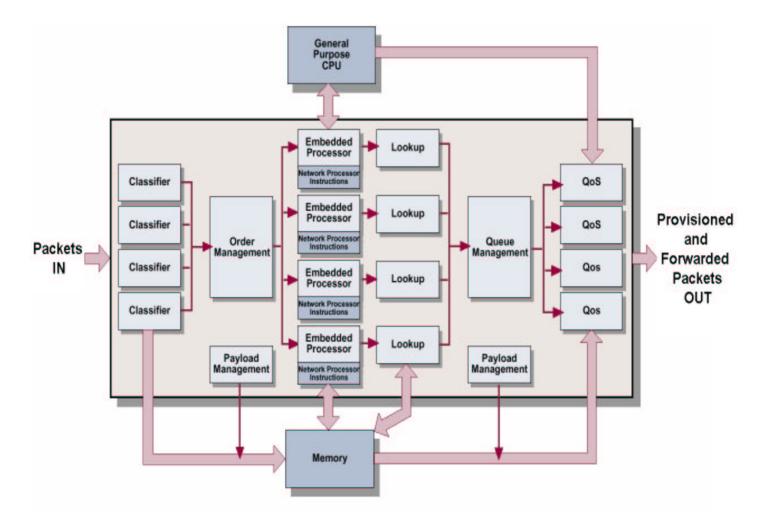

Regardless of specific function, most devises that fall under the category of "network processors" are based on either a multi-processor (highly parallel) or a multi-stage (highly pipelined architecture. In both cases, some type of hardware functional unit (state machine, programmable microprocessor, etc.) is combined with specialized software to support packet-oriented functions. Figures 2.1a and 2.1b graphically depict simple network processor architectures based on pipelined and parallel/multiprocessor approaches respectively. Parallel processing, pipeline and specialized hardwired modules can be used to achieve protocol processing at wire rates.

Figure 2.1a: A Simple network Processing Engine Based on a Pipelined architecture.

Figure 2.1b: A Simple Network Processing Engine Based on a Parallel/Multiprocessor Architecture.

# 2.1.1 Parallel Processing

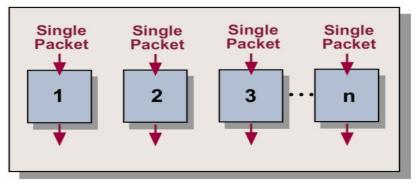

Generally, network processors use parallel processing units (figure 2.1.1a) to improve performance and perform processing at wire rates. Especially for some protocols that each packet can be transported independently (such as IP protocol) is simple to use parallelism. Different packets can be processed in parallel in different processing units (Multi Instruction Multi Data -MIMD- processing). The most common approach is to use many RISC processors in a network processor interconnected to shared memory through a common bus. Data can be demultiplexed into streams and scheduled on the parallel processors through an I/O bus, too. However, flow oriented packet processing units inter-packet dependencies. If packets of the same flow end up in different processing units inter-processor communication is required in MIMD architectures – this increases the complexity of network processors and reduces the performance of the parallel processing units. This inter-packet dependency can be avoided by scheduling packets of the same flow to end up in the same processing unit.

Figure 2.1.1a: Parallel Processing

# 2.1.2 Pipelining

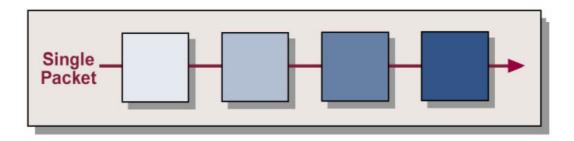

Pipeline is another way to exploit parallelism (figure 2.1.2a). It breaks packet processing into steps, each step is processed in one pipeline stage. Assuming that pipeline architecture has n pipeline stages, at any time n packets are processed concurrently. Packets are processed simultaneously in these stages, but only one result can be completed in each pipeline cycle. This technique can be combined with parallel processing (Pro3 approach § 3.2).

Figure 2.1.2a: Pipelining

## 2.1.3 Specialized Instruction Sets or Units

Analysis and modification of packets involves the manipulation of arbitrary number of bits. General-purpose processor instruction sets such as RISC are optimized for computation on a fixed word size. This leads to several shifting and logical operations to analyze and edit packet data fields. A common operation of this type is to compare a packet field with a value during packet classification. This may be used to identify a protocol. Since data comparison in RISC processors is performed on word boundaries and the bits in the packet field are not aligned, several shifts and logical operations are required to perform the comparison. A solution to this problem is to add special instructions to conventional instruction sets, such as: insert, extract field instructions, to make these operations more efficient. Another solution is to perform operations such as packet classification, which are common for all packets, in specialized hardwired pre-processing or post-processing units (either programmable or not).

# 2.2 Dealing with Memory Latency

Data transfer form and to large memories and various other memory operations such as table lookup, queuing and instruction fetches are required during packet processing. Hardware mechanism are required to "hide" these latencies, otherwise processing units will remain idle, for a great deal of time, waiting for data.

## 2.2.1 Multithreading

Multithreading is a technique that can "hide" these latencies by switching between multiple independent threads. Threads may be different programs or independent segments (such as procedures) of the same program. Since packet processing exhibits a high degree of parallelism, it is possible to identify independent threads. In a multithreading processor, each thread has its own context. A context includes all state unique to a given thread, such as registers, stack pointers, program counters, etc. Normally a memory access by a processor would block it until the data was returned. A multithreading processor can switch between contexts rapidly and the thread that performed the blocking operation can immediately pass control to another thread that is ready for execution. Having a large enough number of threads could completely hide memory latency and keep the processors' resources fully utilized.

# 2.2.2 Memory Managers and Types of RAM

Memory manager units can perform complex memory operations that would block a processor for many cycles if it had to perform them. These individual units can manage memories (memory initialization, allocation, read, write) and perform operations like queuing, tablelookup and tree searches. Modules that use memories need only to send their request to memory manager and request will be performed autonomously. The selection off on-chip and off-chip memories is also very important. SRAMs have better performance, can maintain its data as long as power is provided thus do not need refresh, are small and expensive. On the other hand, DRAMs have worse performance, they need time for refresh, but they provide the lowest cost per bit and greatest density among solid-state memory technologies. The traditional asynchronous DRAM underwent some limited changes. Examples were fast-page-mode (FPM), extended-data-out (EDO) and burst-EDO (BEDO), each provided faster cycle times if accesses were from the same row and thus more bandwidth than the predecessor. Conventional, FPM and EDO DRAM are controlled asynchronously by the memory controller; the memory latency is thus some fractional number of c.c.. An alternative is to make the DRAM interface synchronous such that the DRAM latches information to and from the controller based on a clock signal. SDRAM devices typically have a programmable register that holds a bytes-per-request value. SDRAM may therefore return many bytes over several cycles per request. The advantages include the elimination of the timing strobes and the availability of data from DRAM each clock cycles. RAMbus DRAM (RDRAM) tries to get rid of the latency by actually narrowing the bus path and treating the memory bus as a separate communication channel. Generally speaking, DRAMs use parallelism between their banks to serve many applications and utilize memory's bandwidth. DRAM operations are scheduled, possibly completing memory references out of order, to optimize memory system performance.

### 2.3 Examples of Network Processors

Seeing the unique needs of network processors, many companies such Intel, MMC, Motorola and IBM have introduced new designs for this fast paced market.

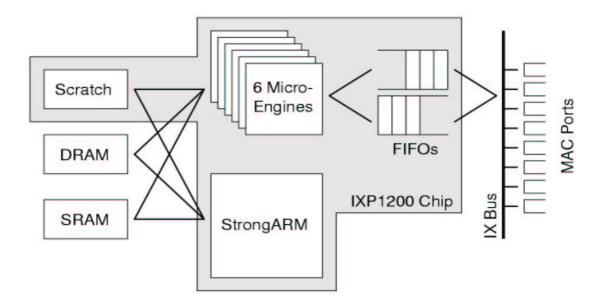

## 2.3.1 Intel's IXP 1200

Intel's IXP 1200 [7, 8, 9] (figure 2.3.1a) architecture consists of 6 micro-engines sharing a bus with memory. The micro-engines are managed by a StrongARM core processor. It has PCI bus to communicate with the host CPU, memory controllers and a bus interface to network MAC devices. The device operates at 166 MHz. Each micro-engine supports 4 threads, which helps to eliminate micro-engines waiting for memory resources. Micro-engines have a large register set, consisting of 128 general-purpose registers, along with 128 transfer registers. Multiple IXP 1200's can be aggregated in serial or parallel. IXP 1200 uses parallel context to hide memory latency. [7] evaluates IXP 1200 performance, implemented a prototype IP router on this processor, and demonstrated that it can sustain line speeds for 8 X 100 Mbps Ethernet ports. Moreover emulating infinitely fast network ports [7] shows that the IXP 1200 is capable of forwarding minimum-sized Ethernet packets at a rate of 2.69 Mbps. This experiments indicated that DRAM (of evaluation system) is the bottleneck and there is processing capability available to get at least 26% improvement with faster memory.

Figure 2.3.1a: Block Diagram of an Intel IXP 1200 Evaluation System

The following tables show IXP family specifications, from Intel's web site:

| Network Processor     | IXP1200              | IXP1240              | IXP1250              | IXP1250<br>extended temp |

|-----------------------|----------------------|----------------------|----------------------|--------------------------|

| Core speeds           | 166, 200, 232<br>MHz | 166, 200, 232<br>MHz | 166, 200, 232<br>MHz | 166 MHz                  |

| Operating temperature | 0° to 70°C           | 0° to 70°C           | 0° to 70°C           | -40° to 85°C             |

| Package               | 432-pin HL-BGA       | 432-pin HL-BGA       | 520-pin ESBGA        | 520-pin ESBGA            |

Table 2.3.1b: Intel IXP Network Processor Family Comparison

| Microengine<br>Core Speed  | 166 MHz     | 200 MHz     | 232 MHz     | 166 MHz<br>extended temp |

|----------------------------|-------------|-------------|-------------|--------------------------|

| IX Bus speed               | 66 MHz      | 85 MHz      | 104 MHz     | 66 MHz                   |

| Micro engine control store | 2K          | 2K          | 2K          | 2K                       |

| Peak IX Bus bandwidth      | 4 Gbps      | 5 Gbps      | 6.26 Gbps   | 4 Gbps                   |

| Internal power supply      | Vdd=2V+/-5% | Vdd=2V+/-5% | Vdd=2V+/-5% | Vdd=2V+/-5%              |

| External power supply      | 3.3+/-10%   | 3.3+/-10%   | 3.3+/-10%   | 3.3+/-5%                 |

| Power dissipation          | 3.80 watts  | 4.48 watts  | 5.19 watts  | 3.80 watts               |

| Memory interface speed     | 83 MHz      | 100 MHz     | 116 MHz     | 83 MHz                   |

Table 2.3.1c:Intel IXP 1200 Bus Speed and Bandwidth Comparison

# 2.3.2 MMC's Anyflow 5000, nP3400, nP7000

MMC [15] developed the AnyFlow 5000 (nPX5000) network processors. These have five different stages: ingress processing, switching, queuing, scheduling and egress processing. Perflow queuing is used which allows each flow to be queued independently. Other functions handled on a per-flow basis are queuing control and scheduling.

#### **AnyFlow 5400 Product Features**

- 5.5 Gbps bandwidth per module, scalable to 22Gbps with up to four 5400 modules

- Direct interface to MMC's BitStream Processors

- Up to 16 Fast Ethernet ports or 2 Gigabit Ethernet ports supported per 5400 device

- Shared packet memory of 3MBytes per module

- Supports unicast, multicast, broadcast and trunking operations

- MMC's output streams group packets going to the same destination and having the same properties, accelerating overall pack processing

- Eight Dynamic Discard Threshold groups provide full flexibility for programmable stream processing

- Support for 802.3x Flow Control generates XON/XOFF credit messages to Ethernet via BitStream Processors

- Scheduling support for 4 CoS per output port

- Full support for Hierarchical Weighted Fair Queuing through MMC's SP/WRR Scheduler with multi-criteria priority selection

- CPU interface provides synchronous 55MHz operation

MMC also developed the nP3400 [13], which integrates a programmable packet processor, switch fabric and multiple Ethernet interfaces on a single chip. It contains two programmable 200-MHz RISC processors and a 4.4 Gb/s switch fabric. It has policy engines supporting 128 rules.

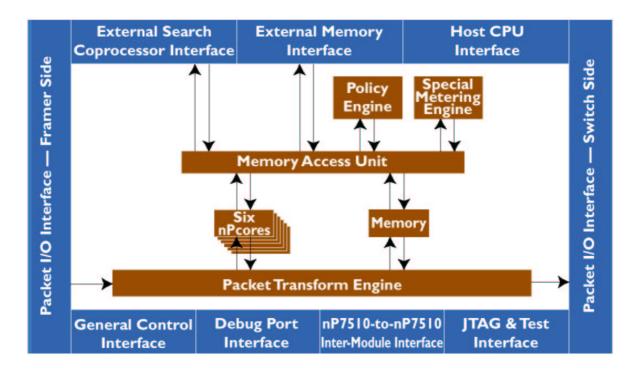

AMCC's purchase of MMC Networks developed nP7250 [13]. This is a straightforward 2.4 Gb/s network processor. It contains two MMC nPcore multithreaded packet processors and connects to an external search coprocessor and a host CPU that handle lower- and higher – level functions, respectively. AMCC transformed the nP7250 into the nP7510 [13] (figure 2.3.2a), the current top of AMCC's line, for 10 Gb/s rates by adding four more nPcore processing units and a chip-to-chip interface that allows multiple nP7510 chips to work together. nP7510 has six 333 MHz nPcores.

Figure 2.3.2a: nP7510: OC 192c Network Processor

# 2.3.3 IBM's NP4GS3 "Rainier"

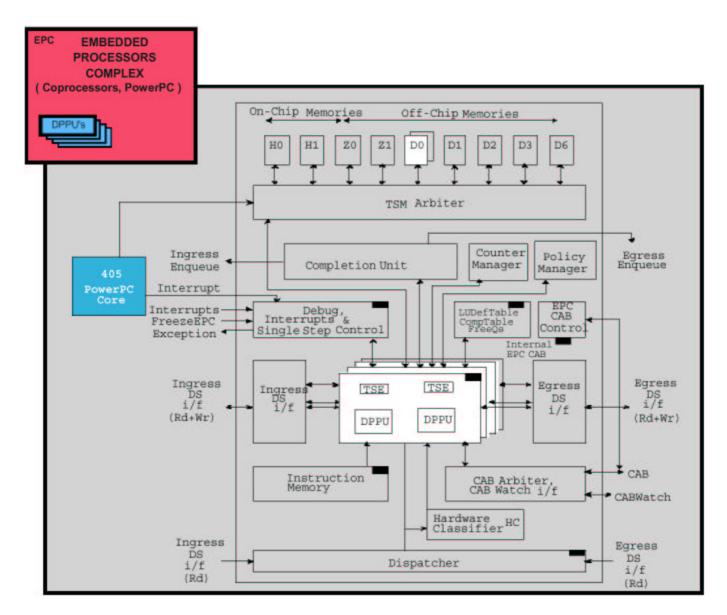

IBM developed the NP4GS3 "Rainier" NPU [14], which has good reviews [20] (figure 2.3.3.a). It has 16 programmable protocol processors and a PowerPC 405 control processor. It has hardware accelerators to perform tree searches, frame forwarding, filtering and alteration. Each processor is a 32-bit, has a 3-stage pipeline (fetch, decode, execute) and runs at 133 MHz. Each processor has seven coprocessors associated with it, including one for checksum, string copy and flow information. Hardware accelerators perform frame filtering, alteration and tree searches.

NP4GS3 function units include tree-search engines (TSE), one of which is shared with each pair of processors; two full-duplex switch interfaces; four 1 Gb/s media-access ports; and interfaces to 10 external memory arrays- eight DDR SDRAM ports and two ZBT SRAM ports.

The aggregate bandwidth of the NP4GS3 is some 4 Gb/s, allowing the part to manage a single OC-48 channel or up to forty 100Mb/s Ethernet ports. Two chips can be connected in series, using the switch interfaces and being controlled by the PPC405 core in one of the chips to double the bandwidth of the subsystem. This capability puts the NP4GS3 within striking distance of 10 Gb/s, but IBM is developing new parts that will exceed this rate in single-chip configurations [20].

For applications that need even faster data rates or more sophisticated processing, multiple NP4GS3s can be configured to communicate through an external switch fabric so that each

chip performs only a portion of the packet-processing tasks. IBM designed the chip to support up to 64 devices in parallel under control of an external CPU.

Figure 2.3.3a: IBM's NP4GS3 "Rainier"EPC High-level Architecture. EPC Architecture, which shows how the EPC core is structured. Note that the Specialized PowerPC 405 engine called the ePPC (Embedded Power PC) resides here and can be used as the CP (Control processor) in systems containing up to 2 NPs.

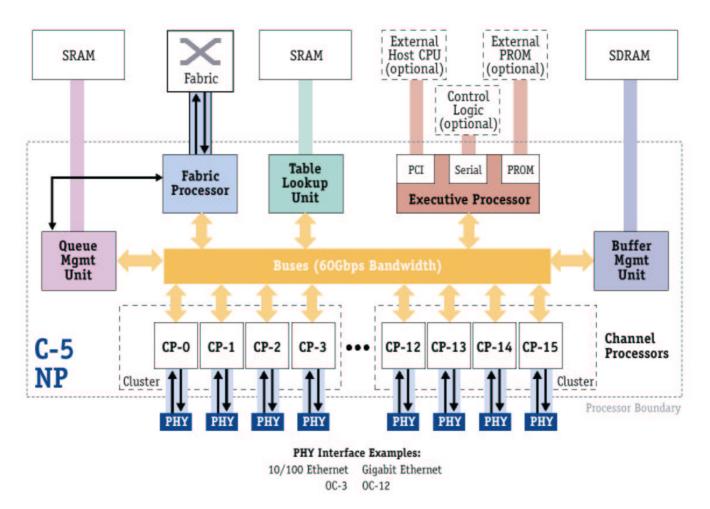

## 2.3.4 Motorola/C-Port C-5

C-Port (acquired by Motorola) developed C-5 network processor [10] (figure 2.3.4a). It includes sixteen 200 MHz channel processors, comparable to IBM's processors [20], along with five different coprocessors for control, switch-fabric interfacing, table lookups, queue management and buffer management. In addition, like the IBM's NP4GS3, the C-5 supports multichip arrangements to support bandwidth faster than the theoretical peak 5 Gb/s capacity

of a single device. The C-5 channel processors are about 50% faster than IBM's NP4GS3 [20], but they lack the multithreading support in the IBM cores. The C-5 also falls slightly short in local memory bandwidth. It supports only a single 128-bit array of external single-data-rate (SDR) SDRAM operating at up to 125 MHz. A maximum of 128 Mbyte of SDRAM can be connected to the chip. Finally, one external 64-bit, 133 MHz ZBT SRAM array, up to 32 Mbyte in size, is also supported to store table data for statistics, routing and quality-of-service (QoS) functions. IBM's offering provides more independent memory arrays that are narrower and faster and that provide more aggregate bandwidth and less risk of contention [20].

Figure 2.3.4a: C-5 Network Processor Block Diagram.

# Chapter 3: Protocol Processor Project Architecture

## 3.1 Protocol Processor Project (Pro<sup>3</sup>)

Pro3 system Architecture [1, 2, 3] aims in accelerating execution of telecom protocols by extending a high-performance RISC core with programmable, pipelined hardware. Processing intensive and (hard) real-time protocol functions are handled by the programmable hardware, while the remaining functions will be handled by the on-chip RISC in an integrated way. The concept of PRO3 is to provide the required processing power through a novel architecture incorporating parallelism and pipelining wherever possible, integrating generic micro-programmed engines with hardwired components optimized for specific protocol processing tasks. Analysis of protocol performance [2], [3] within such systems shows that a small specific subset of the protocol functions (i.e. less than 10%) is active during large period of time (i.e. more than 95% of the entire time span). The other protocol functionality is active when errors occur or for set-up and tear down of a protocol session. PRO3 targets at realizing at wire-speed the aforementioned specific set of the 10% of the protocol functions in the reconfigurable module and the remaining functions in the RISC core. The system is designed to support up to 2.5 Gb/s links for up to 500K flows supporting in worst-case 7.5Mpackets/sec.

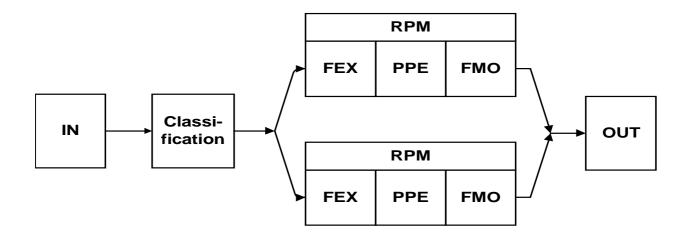

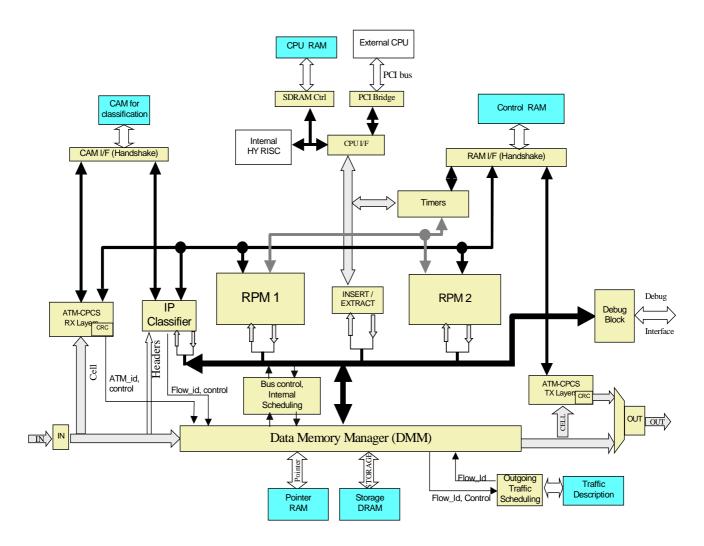

Pro3 processor [5] (figure 3.1a) integrates a state-of-the-art RISC [6], with reconfigurable, pipelined module able to deliver the needed processing power to support efficiently many thousands of (different) protocol instances, hereafter mentioned also as flows. Two such modules constitute the Re-configurable Pipelined Module (RPM figure 3.1a) of the PRO3 system, which operate in parallel, facilitating the execution of protocols with different incoming and outgoing data flow processing as well as load balancing for higher throughput.

In general, within a stateful firewall system, the following sequence of functions is applied to each incoming packet: **reception, classification, state processing, and transmission** (Figure 3.1b). Each generic function consists of a set of lower level functions and can be understood as pipeline stages. Other main blocks include **data/queue manager** and higher layer protocol processing performed in SW (**Hyperstone or the external CPU**). The common path for stateful inspection up to the transport layer will be performed in the **PRO<sup>3</sup> hardware pipeline**, and higher layer applications on the **Hyperstone internal CPU**.

Within the ATM switch system for control plane processing the above basic blocks will also exist, re-using common HW structures or dedicated ones. Part of the higher layer processing is performed in SW running on the Hyperstone CPU. Communication with the host system (External CPU), which executes the management plane, is required.

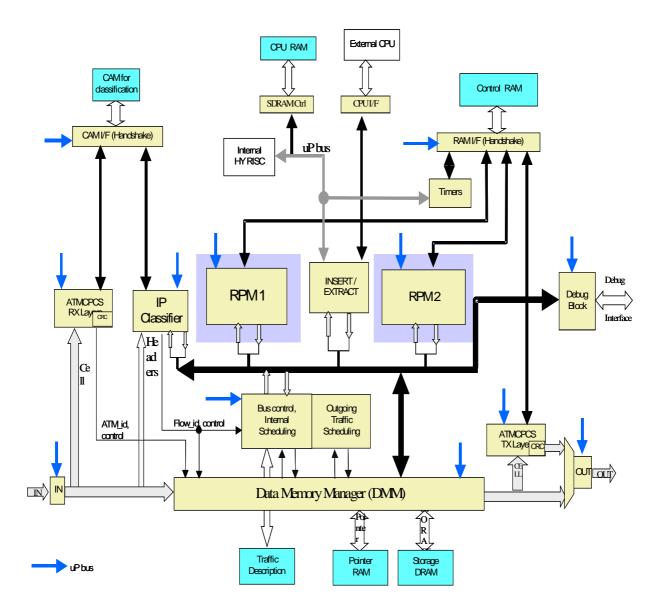

Figure 3.1a: Pro<sup>3</sup> Architecture

Figure 3.1b: Pro3 pipeline stages (Reception, Classification, State Processing and Transmition)

# 3.2 Functional architecture

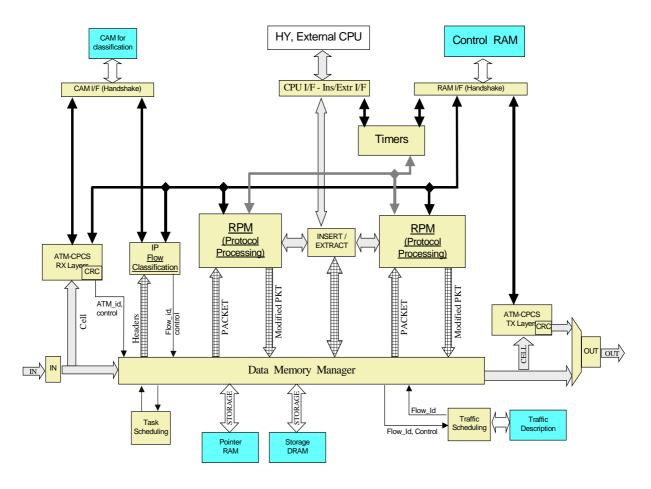

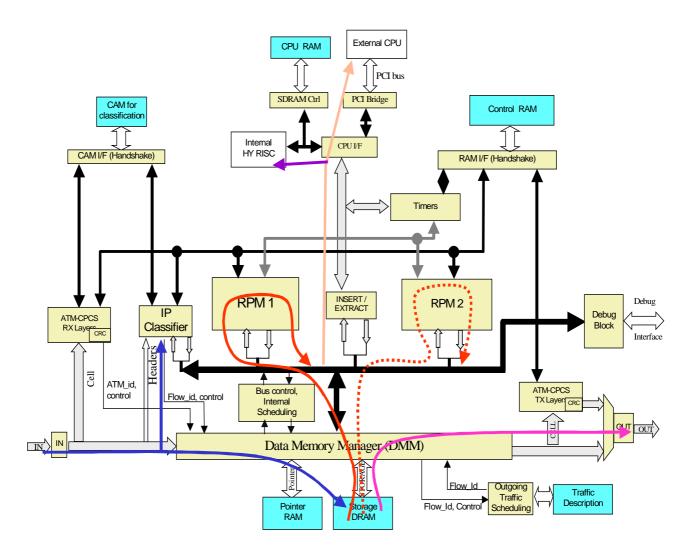

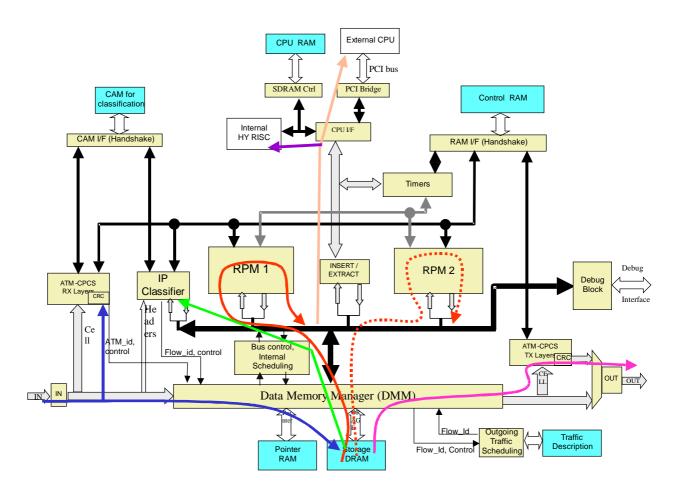

Figure 3.2a summarises the PRO<sup>3</sup> functional architecture.

Figure 3.2a: PRO<sup>3</sup> functional architecture

As depicted in Figure 3.2a, the networking data are stored temporarily on the data storage DRAM and then forwarded either to one of the two RPMs or to one of the two processors (the internal Hyperstone CPU or the external CPU). The data paths and sequence of operations are described in the following section.

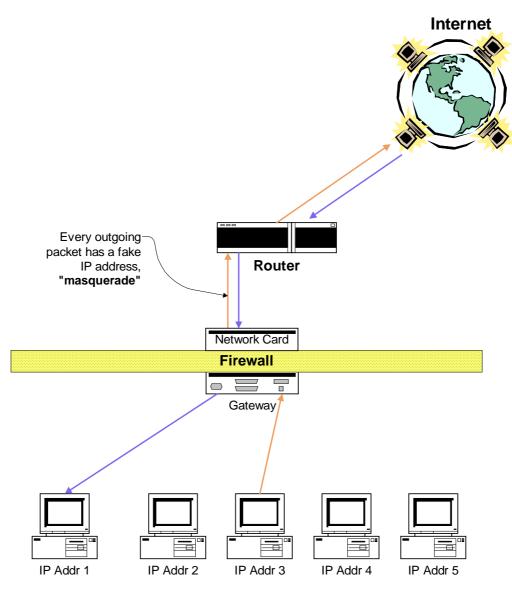

A simple example of a firewall system is described next. Figure 3.2b shows five PCs that are protected by a firewall. Incoming packets come from the outside world through a router to the firewall and they either pass or are rejected according to firewall's policy. Similarly outgoing packets are been rejected or pass through the firewall. Outgoing packets do not show their real source IP address, they seem to have source IP addresses other than their real ones. This function of firewall is called *masquerade*. Firewall's policy allows specific protocols to go out from an IP address and specific protocols to end up in an IP address. For example firewall can decide that nobody outside the firewall can use telnet to access IP1, or that IP3 cannot send e-

mails and can only use http protocol. Every protocol corresponds to a connection port. These rules and the IP address of every PC determine the result of every protocol process's execution.

Figure 3.2b: Firewall for IP packets

## 3.3 Physical architecture

Figure 3.3a depicts the PRO<sup>3</sup> physical architecture. A debug block is added that will be used for chip verification and application firmware debugging. Furthermore, the insert/extract block is elaborated and the interconnection of the internal Hyperstone CPU and the external CPU is presented.

Figure 3.2.a: PRO<sup>3</sup> physical architecture

In Figure 3.2a, a shared internal bus is shown that is used for data transfer between the RPMs and the Data Memory Manager (DMM). Apart from this point-to-point data transfer there is communication between the two RPMs or between them and one of the two CPUs.

In addition to this internal bus for on-chip communication, there is an additional microprocessor bus shared among all blocks for their configuration, control and firmware download. This bus is in fact the uP bus of the internal Hyperstone CPU.

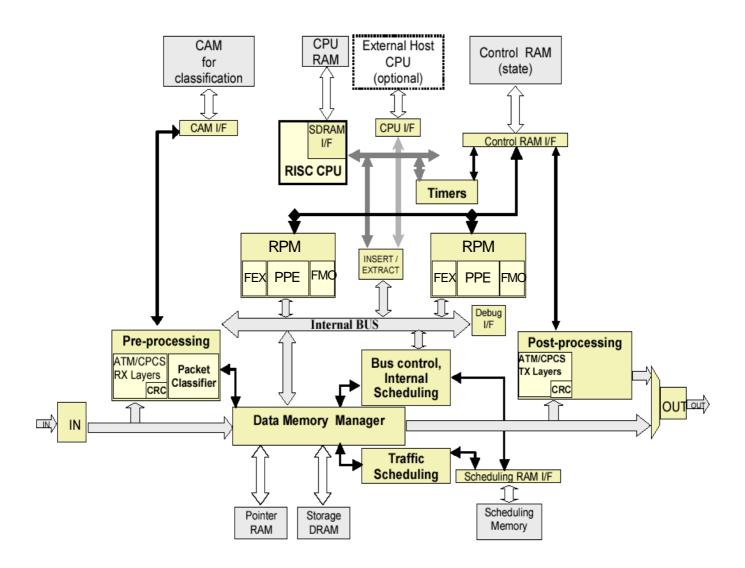

Packet pre-processing and lower layer protocol functions are executed by means of hardwired functionality (like the full ATM/CPCS layers) as well as programmable PDU processing and packet classification by means of a RISC-like micro-engine for Field Extraction (FEX) and controller of a high throughput external Ternary CAM (Content Addressable Memory) device for flexible and deterministic classification.

Since the processor must be able to support thousands of active instances of protocol FSMs, special circuitry designed to provide a pool of timer resources for the realization of the (many) thousands of active watchdog timers. The timer information is stored in the flow state.

In the transmition flow the operation of PRO3 is based on packet buffering prior to protocol processing. A Data memory Management sub-system (DMM) is responsible for memory allocation and stream buffering. Data can be retrieved by DMM in response to specific commands and be delivered over the internal bus to the RPM modules or via the insert/extract interface to the control RISC or to host CPU.

The internal Scheduling Unit maintains a number of priority queues in order to schedule the forwarding of the packets for processing according to the priority of each flow. It is also used to multiplex the execution of data transactions from the DMM to the different internal destination via the Internal Bus. Data memory interface consists of a DDR SDRAM memory block. It has been selected that is able to offer bandwidth of up to 17 Gbps. The memory data bus is 64 bit wide running @ 133 MHz.

The shared internal bus has been defined following a worst-case approach. The bus will use a 64 bit wide data bus running @ 200 MHz. This internal bus will be bi-directional and shared among all blocks as shown in the above figure. Moreover, control and address signals will be shared. A point-to-point control interface will connect each component with the bus arbiter and task scheduler for chip control and operations synchronisation.

## 3.4 Internal data paths

The internal data paths and sequence of operations of both the IP Application and the ATM Application are now detailed.

# 3.4.1 IP Application

In this section we analyse the data paths of the IP application that is typical for monitor type of applications. Based on the functional architecture described above, a number of data paths may be traversed through the PRO<sup>3</sup> system, depending on the required type of processing.

Incoming packets are directly forwarded to the DMM for storage. The memory allocation is based on fixed size segments, thus a segmentation and reassembly function is built in the component. As the packet is sent to the DMM, it is also copied to the IP classifier for flow classification. The fields required for the IP flow classification of the packet are extracted, and fed to a CAM in order to take decisions regarding the packet. As soon as the packet is correctly classified, its Flow\_ID is obtained and sent to the DMM in order to assign the temporarily stored packet to the proper queue. Finally the task scheduler is updated regarding the new packet.

Following a command by the task scheduler, the packet is forwarded to one of the protocol processing units or to one of the two CPUs either in its entirety or in parts. After processing is complete, updated data are returned to the DMM and the packet is scheduled for transmission.

When worst-case traffic conditions are to be serviced, pass through processing is required. This implies processing of minimum sized packets (i.e. 40 bytes), received and transmitted at a rate of 2.5 Gbps. By translating these figures into processing time we found that 128ns are available for the processing of each packet. On the other hand, when more elaborate processing is required on the packets, it is safely assumed that worst-case traffic conditions are not going to be observed under normal circumstances and, therefore, average traffic is considered.

In the next sections we analyse the operations existing in the IP-based protocols. Such protocols use either the IP over SONET interface or the IP over ATM interface.

#### 3.4.1.1 IP over SONET interface

In the IP over SONET interface, the data flows and the sequence of operations are illustrated in Figure 3.4.1.1a. In this type of applications (process and forward) there are two alternative blocks for protocol processing, namely RPM1 and RPM2. In general there are three independent sequences of operations that perform in parallel and have the DMM as common reference. These are *packet reception, packet processing,* and *packet transmission*. Furthermore, there is *an additional operation and data path between the two CPUs* that is not controlled by the task scheduler.

The operations are initiated upon the appearance of specific events and are completed as soon as a packet is received by the destination or sent to the network. Thus the operations are initiated from the IN block (at reception of packet), from the task scheduler (send packet for processing, or send packet back to DMM after processing, or insert/extract packet) and from the traffic scheduler (send packet to the network). In other words, the IN block initiates and controls the transactions for the input interface (reception process), the task scheduler initiates and controls the transactions in the internal bus (packet processing), and the traffic scheduler initiates and controls the transactions in the outgoing network interface (transmission). In terms of bandwidth, these operations correspond to 2.5Gbps for reception and transmission processes each and 5 Gbps for packet processing (2.5 Gbps send for processing and 2.5 Gbps received after processing).

Figure 3.4.1.1a: Data flows for IP over SONET applications

#### A. Packet reception

IN module receives a packet and forwards it to the IP classifier and DMM. IP classifier makes preliminary check, and performs field extraction and classification. Obtains Flow\_ID, Priority and Control info and sends them to the DMM. DMM segments received packet, and stores it in a temporary queue, calculates and stores packet length. It also sends to Schedulers scheduling info based on Priority, Flow\_ID and Control info received.

If the packet is to be processed then update the task scheduler control info else if the packet is to be forwarded to the network without processing, then update the traffic scheduler control info.

#### **B.** Packet processing

The task scheduler initiates and controls the operation of the internal bus and sets up the inter-block communication. It receives various input signals and identifies both sender and destination blocks.

In the following the five possible senders to destination operations are identified and described. As any block, we consider one of the RPMs, the internal CPU, or the interface to the external CPU. These blocks may be used for packet processing. Packets are usually processed in RPMs, rarely in internal CPU and in special cases in external CPU.

1. DMM to any block:

DMM sends a segment of a packet, and some additional information (classifier information, commands) through internal bus for processing.

2. Any block to DMM:

This operation is performed when an insert (processed) packet and control command is sent from a CPU or an RPM to the DMM. In case of a processed packet DMM stores it and updates the control entry for the task scheduler. Whether the packet is ready to be transmitted to the network, it is appended to an output queue. Else if the packet is to continue processing to a higher protocol layer, then it is appended to the respective higher layer queue. It might be the case that DMM receives only a control command without data.

3. RPM1 to RPM2:

In this case, RPM1 has to inform RPM2 to perform an action (send a packet). As soon as the task scheduler decides for this communication,

4. RPM to insert/extract:

In this case, RPM has to send a packet to a CPU through insert/extract module. The task scheduler will enable the transaction.

5. Insert/extract to RPM:

In this case, a CPU has to send a packet to an RPM through insert/extract module. Again the Task Scheduler will enable the transaction.

#### C. Packet transmission

The traffic Scheduler reads the status of the output traffic classes and selects the Flow\_ID of the next packet to be transmitted, it sends a command to DMM (dedicate bus) for the next packet (Flow\_ID, control) to be sent and updates its traffic queues. DMM decodes the command, reads the packet/cell to be sent and updates pointers and control.

#### D. CPU1 to CPU2 data path

An additional data path is foreseen between the two CPUs. This communication is resolved locally without the Task Scheduler coordination. The CPU I/F controls the operation and multiplexes it with the communication operations of the two CPUs with the insert/extract block (through it to DMM, RPM1, RPM2).

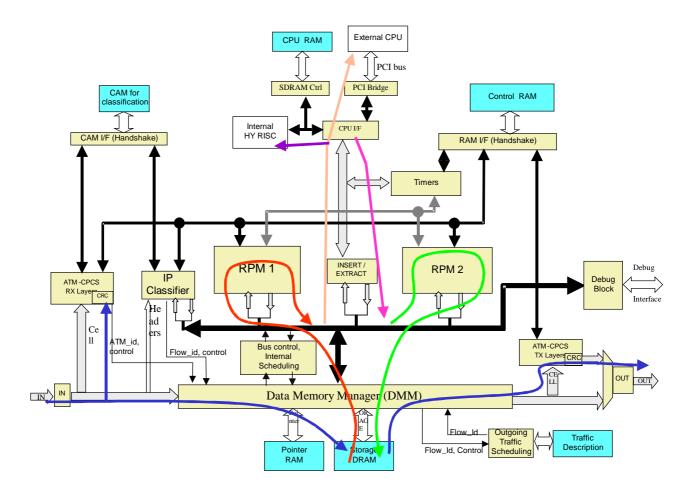

#### 3.4.1.2 IP over ATM interface

In protocols based on the IP over ATM transfer mode, the data flows and sequence of operations are illustrated in figure 3.4.1.2a. The data flows are similar to the ones presented in the previous sections. The difference is that the protocol needs first ATM-based and then IP-based classification. The protocol processing is performed based on the Flow\_ID obtained from the IP flow classification. In general in this mode the received cells are classified and queued into a number of ATM specific queues. As soon as a valid Common Part Convergence Sublayer (CPCS) packet is completed, the packet is queued for IP flow classification. Due to the non-sequential arrival of the ATM cells, it is not possible to keep information of message organization (list of cells that belong to a message) in a single queue (input queue). ATM cells are enqueued to the proper ATM flow. As soon as an ATM-CPCS message is completed, then it is forwarded for IP classification. After the IP classification, the encapsulated IP packet is appended to a single queue. In this mode of operation as well as in an ATM cell based interface in general, the DMM stores cell based streams. Here, the DMM must be able to extract only the cell payloads and send it for protocol processing.

Figure 3.4.1.2a: Data flows for IP over ATM applications

## 3.4.2 ATM application

In this section we analyse the data paths of the PRO<sup>3</sup> ATM application that is typical for terminal type of applications where protocol (or stack) termination and initiation is performed. Incoming cells are directly forwarded to the DMM for storage and copied to the ATM/CPCS receive block for classification. The cells are waiting in a FIFO for the result of the classification (Flow\_ID, Control, Priority) and are then appended to the right ATM queue. Since the ATM cells, which belong to an ATM message, don't arrive sequentially, they have to wait in an on-chip buffer until a Flow\_ID as well as the cell type (last or intermediate cell of a message) is defined.

In general all data flows and operations involved in the ATM application are identical with the operations described in the IP over SONET applications. The difference is that the ATM/CPCS components are involved and that the DMM stores queues of cells.

Figure 3.4.1.3a: Data flows for ATM applications

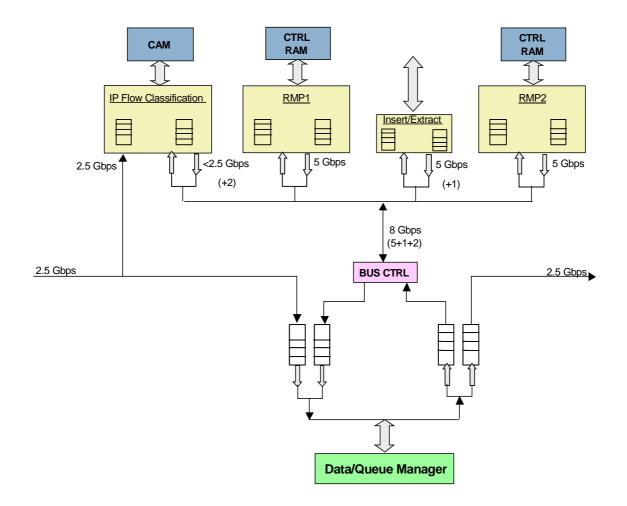

# 3.5 Internal interfaces

Having described the data paths traversed within the  $PRO^3$  system, it is necessary to briefly refer to the block interfaces. Interconnections between the various blocks, together with an indication on the required bandwidth in each interconnection segment are shown in Figure 3.5a.

Figure 3.5a: PRO<sup>3</sup> internal interfaces

# 3.6 Re-configurable Pipelined Module (RPM)

The Re-configurable Pipelined Module (RPM) components are highlighted in figure 3.6a

Figure 3.6a: The two RPMs in Pro<sup>3</sup>

The following figure presents an abstract block diagram of RPM.

Figure 3.6b: RPM block diagram

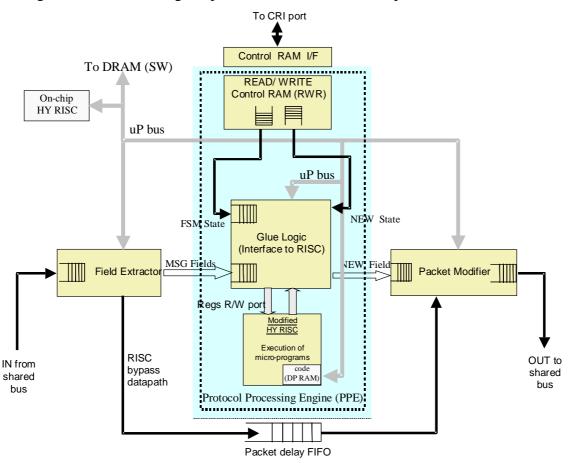

The Re-configurable Pipelined Module (RPM) is the heart of the protocol processing of the Pro<sup>3</sup> system. It consists of three sub-modules, each of which performs a part of the required protocol processing. The sub-modules, shown in Figure 3.6b (detailed block diagram in figure 4a), are Field Extractor, Protocol Processing Engine, and Packet Modifier. PPE contains a modified RISC, which is of the same architecture as the generic RISC CPU (Internal CPU Figure 3.6.2a and Figure 4a) but optimized (i.e. for efficient context switching with a set of shadow registers). For each packet, the input to the RPM module is (i) the packet's flow-id and the packet type as identified by the flow classification module, (ii) the entire flow state from the state memory, and (iii) the entire header of the packet. The filtered data are passed through the RPM pipeline to execute the protocol processing code. Between the (sub) modules, queues are used to de-couple the operations and latencies of the modules.

|    | FEX | PPE       | FMO |     |     |

|----|-----|-----------|-----|-----|-----|

| A0 | A0  | <b>A0</b> | A0  |     |     |

|    |     | FEX       | PPE | FMO |     |

| B0 |     | В0        | B0  | B0  |     |

|    |     |           | FEX | PPE | FMO |

| C0 |     |           | C0  | C0  | C0  |

Figure 3.6d: the vertical highlighted slice shows the pipelined operation, where A0 is processed in FMO, B0 is processed in PPE and C0 is processed in FEX

## 3.6.1 Field Extractor

### **Main Features**

- Extract (actually isolate) specific fields contained within a packet and forward them to the Protocol Processing Engine (PPE) of RPM for processing.

- Field extraction process can start from the packet header (or headers in case of packet encapsulation) or the trailer(s).

- Able to process data with a maximum throughput of 3.2Gbps. This is accomplished by using a 32-bit wide data path and operating clock frequency of 100MHz (half of the system clock). The aggregate throughput varies between 3.2 Gbps and 2.5 Gbps since the processing of one word may require more than one clock cycles to complete.

• The performance target is that most of the instructions will need one clock cycle to complete.

The Field Extractor (FEX) is practically a very small RISC designed for this specific task. It combines high performance and flexibility with low silicon requirements.

## **Specifications**

The FEX operation is controlled by microcode (firmware) stored in a small internal SRAM. The instruction set comprises of simple and generic (i.e. protocol-independent) instructions that can be applied in any protocol or protocol encapsulation scheme. The internal or external CPU can download the firmware dynamically during run-time.

FEX is designed to be as much generic as possible, however it is assumed that it is integrated in PRO3 and has to decode the 64-bit control word that exists in front of each 64-byte segment sent to RPM. The FEX input is compliant to the PRO3 internal bus.

Field Extractor extracts the packet fields needed for process to PPE. The rest of the packet fields are sent to the Delay Fifo.

- The extracted fields are output in 32-bit words.

- The fields are sent to PPE through the Field FIFO, in the following order: Flow ID, PROTO, Message Type, <FIELDS>, Last word with valid Control Flags. The first three fields are required for PPE-input read requests (flow state needs flow ID, Dispatch PC needs PROTO & Message Type). The last field of the set of fields contains no valid field but valid Control Flags that delineate end of fields and end of packets (2 bits).

- Only a single header/trailer can be processed at any time. However an unlimited (theoretically) number of headers/trailers can be processed sequentially.

In case a large number of fields have to be extracted, the firmware may extract part of the 32bit word that contains more than one field, handled as a large field. The firmware runs in the Modified HY RISC should now how to handle this case.

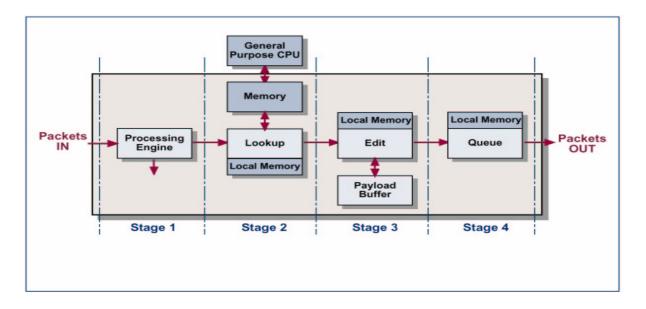

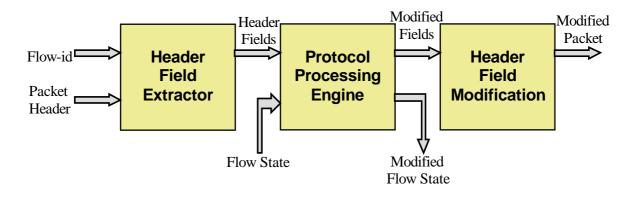

# 3.6.2 Protocol Processing Engine

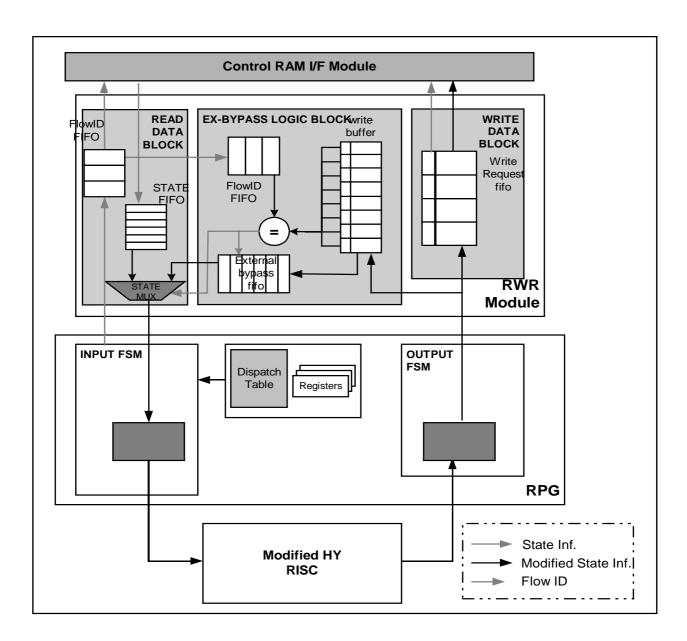

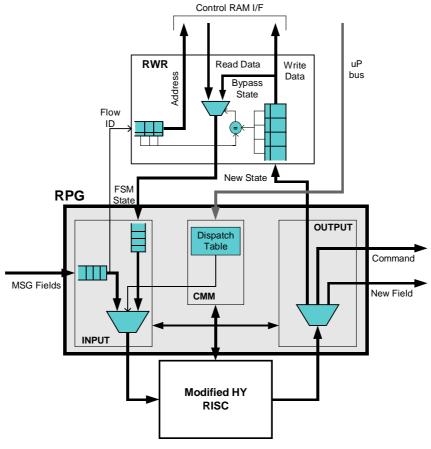

The Protocol-Processing Engine (PPE) is the core of PRO<sup>3</sup> RPM. It consists of a modified Hyperstone RISC core, augmented with peripheral "glue" logic that implements the input and output interfaces. The input interface accepts data from the field extractor module, as well as the data (flow state information) read from the state memory (Control RAM). The Hyperstone RISC uses these data as input to the protocol processing code. The output interface sends the updated state to the state memory for writing, and informs the rest of the PRO<sup>3</sup> system (through the header modification -FMO) of the decisions of the protocol processing code. One such decision may be to drop or not the packet according to the firewalling policies. Figure 4a presents the detailed block diagram of RPM detailing the position and communication paths of the PPE (including the RPM Glue Logic (RPG) and the Read/Write Control RAM (RWR)).

The high-level internal structure of the Protocol Processing Engine is shown in Figure 3.6.2a. The dashed paths in MHY depict the conceptual switch achieved by changing in/out on process registers.

Figure 3.6.2a: The Protocol Processing Engine

## **Main Features**

- Transfers data from Field Extractor to modified HY-RISC, and from modified HY-RISC to Field Modifier

- State information reading access from Control RAM to PPE.

- State information updating access from PPE to Control RAM.

- State information external bypass mechanism (RWR).

- Aggregate per group peak rate shaping for IP flows

- Programmable entry points for S/W packet handling according to protocol type and message type

- Programmable handling of "input" and "output" parts of flow state

- Implements bypassing of updated flow state for back-to-back processing of packets of the same flow (RPG).

- Full bandwidth input/output capacity

## **Specifications**

PPE uses a fixed number of registers to pass the extracted data from the Field Extractor to the RISC or to read the results of processing and send them to the Packet Modifier. In case that the data to be exchanged require larger space and do not fit in the registers (e.g. the case a large message with many fields is to be processed), the glue logic is able to segment and forward them to the RISC in steps. This means that the software routine to process this message inside the RISC is segmented into several parts defined at software development phase.

The modified Hyperstone RISC includes an external read/write port to its internal register file. During the processing of each packet, the internal registers are (conceptually) partitioned in two sets: working and I/O registers. The working registers are the ones that are used by instructions (and only by instructions) for the purpose of executing the protocol processing code. The I/O registers are accessed only through the external port by the interface logic. The purpose of the I/O registers is twofold: (1) to prepare the data necessary for the processing of the *next* packet (input part), and (2) to output the protocol decision for the previous packet to the FMO and the updated state information to the state memory (output part). Once all the above actions are completed, the processing registers (usually) become I/O registers, the I/O registers become processing registers, and the processing of the next packet is initiated. At the same time the updated state for the just-processed cell is sent to the state memory and the next packet header and state fields are put in the input part of the register file.

**RPM** PPE **FMO FEX** input process output IN OUT **RPM** PPE **FEX** input **FMO** process output

The following figure presents the pipeline stages of RPM system,

Figure 3.6.2b: RPM's pipeline stages

# 3.6.3 Field Modifier

## **Main Features**

- Operation 1: Compose a packet (protocol message) according to a specific template and put in user-defined positions a number of fields received as input.

- Operation 2: Modify (actually replace) specific fields contained within a packet. As input packet an entire packet (or part of packet) can be used. This data is forwarded by FEX and delayed in the Delay FIFO of the RPM.

- Operation 3: Create an internal message for another component. This does not have the form of a protocol message but it is according to PRO3 internal control commands.

- Field Modification process can start from the packet header (or headers in case of packet encapsulation) or the trailer(s).

- Able to process data with a maximum throughput of 3.2Gbps. This is accomplished by using a 32-bit wide data path and operating clock frequency of 100MHz (Half of the System Clock). The aggregate throughput varies between 3.2Gbps and 2.5Gbps since the processing of one word may require more than one clock cycles to complete.

- The performance target is that most of the instructions will need one clock cycle to complete.

The created packet can then be forwarded to the PRO3 internal bus towards another component. The fields used to create a packet come from the RPM RISC core and can be part of the packet header (or headers in case of packet encapsulation) or trailer(s) or even control fields for internal commands.

The Field Modifier (FMO) is a small RISC that performs the dual operation of the Field Extractor. It combines high performance and flexibility with low silicon requirements.

# Specifications

The FMO operation is controlled by microcode (firmware) stored in an internal SRAM. The instruction set comprises of simple and generic (i.e. protocol-independent) instructions that can be applied in any protocol or protocol encapsulation scheme. The internal or external CPU can download the firmware dynamically in run-time, through the microprocessor interface. The SRAM is dual port and is seen by the CPU as a memory peripheral.

FMO is designed to be as much generic as possible, however it is assumed that it is integrated in PRO3 and has to encode the 64-bit control word that exists in front of each 64-byte segment or control message sent to the PRO3 internal bus. The FMO output is compliant to the PRO3 internal bus specification.

FMO is assumed to comply with the overall processing architecture of PRO3. Time is distinguished into Processing Slots, where each Processing Slot can be variable in time and is able to accommodate and process either up to 7 PRO3 segments of a large packet or an entire packet of less than 7 segments. Each segment is 64-byte long.

The module operates on the packet data in the following manner:

- In general, we assume that after a message (packet) processing, PPE can generate several sets of fields for composing relevant messages as results.

- One of these field sets will modify the packet waiting in the Delay FIFO of RPM and the modified packet will be sent to the right destination.

- One or more set of fields can be used to construct new packets to be sent to DMM or to other PRO3 blocks.

- One or more set of fields can be used to construct control messages to other PRO3 blocks.

- Reject the packet waiting in the Delay FIFO.

- The above correspond to the following main modes of operation of the FMO block.

- **Operation 1: Packet composition**: Compose a packet (protocol message) according to a specific template (known by the firmware) and putting in user defined positions a number of fields received as input.

- **Operation 2: Packet Modification**: Modify (actually replace) specific fields contained within a packet. As input, an entire packet (or part of packet) can be used. This data has been forwarded by FEX and waited in the Delay FIFO of the RPM. This data is exactly the packet or part of packet that was sent to the RPM for processing (corresponds to one Processing Slot).

- **Operation 3: Packet Creation**: Create an internal message for another component. This does not necessarily have the form of a protocol message but it is according to PRO3 internal control commands.

PPE specifies the command to be performed through the CMD FIFO.

- The packet data are internally shaped and processed in 32-bit words.

- The new fields are received in 32-bit words from the PPE.

- The fields are received through the Field FIFO, in the following order: PROTO, Message Type, Subtype, <FIELDS>, Last word with valid Control Flags. The first three fields are required for FMO firmware branches. Message Type and subtype can also be used for packet composition. The last field of the set of fields contains no valid field but valid Control Flags that delineate end of fields and end of packets (2 bits).

- Only a single header/trailer can be processed at any time. However an unlimited (theoretically) number of headers/trailers can be processed sequentially (corresponding to encapsulated protocols).

In case a large number of fields have been generated as a result of a packet processing, the PPE glue logic is responsible to send all these fields to the FMO. However, in case the FMO FIFO becomes full, the PPE logic has to wait and then send the remaining fields.

# Chapter 4: PPE Architecture

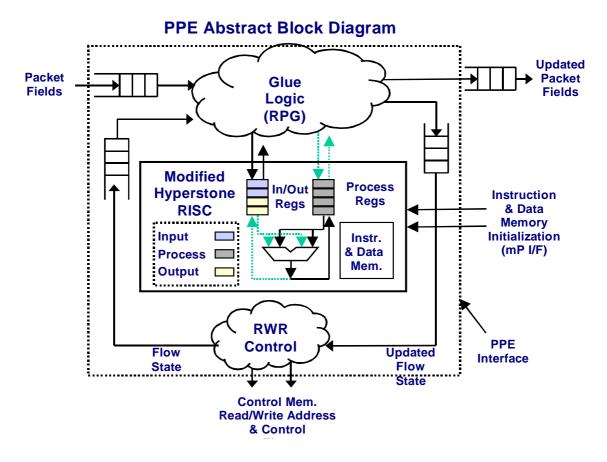

### Position in PRO3 System

PPE is part of the two RPMs instances RPM 1 and RPM 2 as shown in figure 3.6a. PPE module consists of three modules: (i) the Hyperstone Modified RISC, (ii) the RPM Glue Logic, and (iii) the Read/Write Control RAM module (RWR). The following figure presents the block diagram of RPM detailing the position and communication paths of the MHY.

Figure 4a: PPE location inside the RPM along with its main communication paths

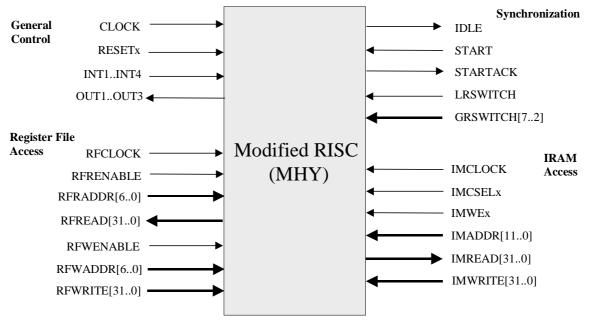

# 4.1 Modified Hyperstone RISC (MHY)

## Main Features

- 32 global and 64 local registers of 32 bits each, 16 global and 16 local registers directly addressable

- Two sets of 14 global registers (12 of them are used for flow state) and 64 local registers (for packet fields transfer) are accessible from outside the core via a special port

- Core accesses are switchable between the two sets of 12 global registers and between the two parts of a 32+32 register partitioning of the 64 local registers

- 16 KB dual-ported internal memory (IRAM) with the second port accessible from outside the core

- Special instruction for power-down control and synchronization with RPM glue logic

### Interfaces:

## **General Description**

The Hyperstone Modified RISC (MHY) module is the central packet-processing element in the PRO3 system. It interfaces to the RPM Glue Logic through the synchronization lines, the special register file access port, and the internal memory access port.

After reset, the MHY begins executing its firmware that has been put into the internal memory by the control processor (internal Hyperstone CPU). Following the initialization, the MHY enters its idle state.

To process a packet, the following steps are executed:

- The RPM Glue Logic places extracted fields from the packet as well as state information about the flow into the MHY register file and/or internal memory. When this is complete, the LRSWITCH and GRSWITCH signals are set to indicate the correct packet data locations, and the MHY is started with the START signal.

- The MHY uses one of the input registers to dispatch to the correct routine for packet processing, and processes the data to produce updated state information and, if applicable, output packet fields. While this process is running, the RPM Glue Logic may use the

second part of the register file to already load the field and state information for the next packet.

• The MHY signals completion of the packet processing routine by asserting the IDLE signal. If new data has been loaded, a new packet processing operation can be started immediately. The RPM Glue Logic can now read the updated field and state information from the MHY register file and/or internal memory. In case of the MHY register file, *this readout may overlap with the writing of the next packet fields and state*.

### Modifications compared to standard Hyperstone Core

The Modified Hyperstone RISC (MHY) is a derivative of the standard Hyperstone E1-32XS microprocessor core. Compared to the standard E1-32XS macro cell, the following things have been modified:

- An additional read and an additional write port has been added to the register file. Through the added write port, state and packet information can be put into the register file by the RPM glue logic, and through the added read port, updated state and packet information is read out by the RPM glue logic.

- The local register part of the register file has been partitioned from 64 registers into  $2 \times 32$  registers, and the global registers G2..G15 have been duplicated. When this partitioning has been enabled by the MHY, the RPM glue logic can select which of the 32 local register partitions is used by the MHY on a local register access, and it can select in which global register block is used by the MHY on a global register access. The selection for the global registers can be done independently for G4 and G5, for G6 and G7, ... G14 and G15.

- Power-down and synchronization logic has been added to start processing when a new set of state and packet information is available in the register file to process, and to signal completion of this processing. When no processing is active, the MHY switches off most of its clocks until the next packet processing starts.

- The DSP instructions and the related logic parts of the DSP execution engine have been removed in order to regain G14 and G15 as general purpose global registers. The DSP execution engine itself has been kept in order to support the ALU multiply instruction.

- Almost all of the external bus interface logic has been removed.

- For initial program load, a separate data path to the internal memory has been added so that the internal CPU can access the MHY IRAM for initialization and for status inquiries. After the MHY IRAM has been initialized, the MHY reset exception begins booting from the code in IRAM.

### Examples of block Operation

In this section, signal diagrams are given showing typical operations for the power-sown synchronization, for the register file access, and for the IRAM access.

### **IDLE-START** and Power-Down Synchronization

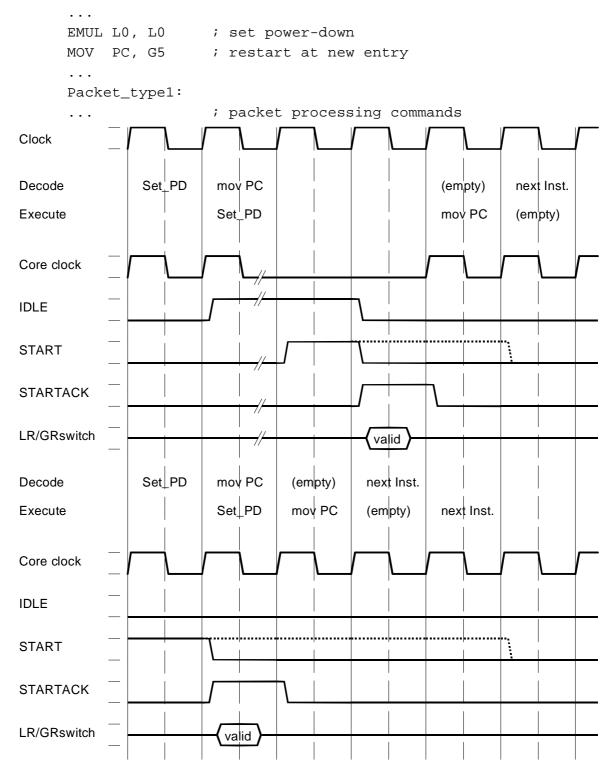

The following figure shows the signal forms for the IDLE, START and STARTACK signals and their relation to the internal core clock showing two different cases. Both cases assume that the sequence of instructions is:

Figure 4.1a: IDLE, START, STARTACK synchronization

The first case assumes that the START signal is not asserted during the decode cycle of the Set Power-down instruction. The second case assumes that the START signal is already asserted during the decode cycle of the Set Power-down instruction.

In the first case, the core clock is suspended for at least one clock cycle. The IDLE signal indicates this fact.

When the START signal is activated (found high on a falling system clock edge), the core begins wakeup from sleep mode and performs the transition back to normal working mode. The STARTACK signal is asserted for one clock cycle in the following system clock cycle. The LRSWITCH and GRSWITCH signals are latched on the falling system clock edge in the clock cycle where STARTACK is asserted. In the system clock cycle following the assertion of STARTACK, the core resumes execution with the instruction following the Set Power-down instruction.

START may be asserted for more than one clock cycle without disturbing the functionality. This first case is also valid if the START signal is asserted during the same clock cycle when the IDLE signal is asserted.

In the second case, the core does not actually enter power-down mode since the START signal is asserted early. Thus, there is no transition of the IDLE signal. During the execution cycle of the Set Power-down instruction, the STARTACK signal is asserted to indicate that there has been a wakeup from a (not executed) power-down command, and in this same cycle also the register switch signals are latched on the falling system clock edge.

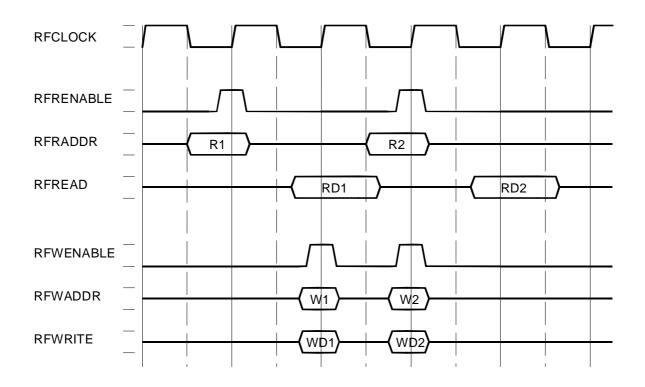

### **Register File Access**

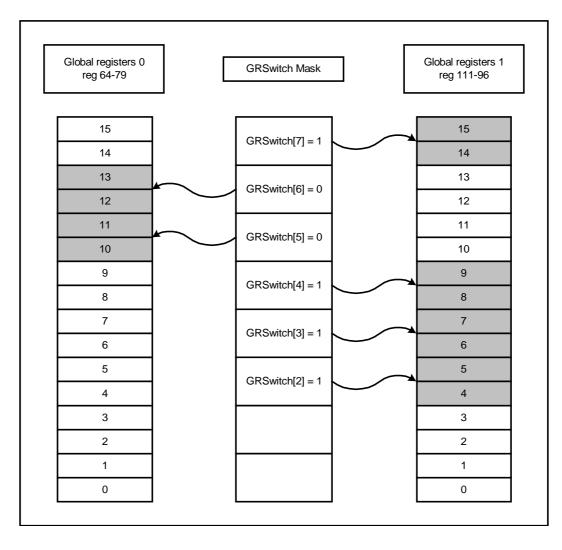

The MHY register file consisting of the 64 local registers and of two sets of the global registers G2..G15 are accessible through a special register file access port. For the register file access from outside, there are the LRSWITCH and GRSWITCH control signals.

The core accesses the local register stack in two partitions of 32 registers each. If the LRSwitch is set to 0, the core accesses the lower 32 local registers (0-31 L0), and the higher 32 local registers when the latched LRSwitch signal is 1(32-63 L1).

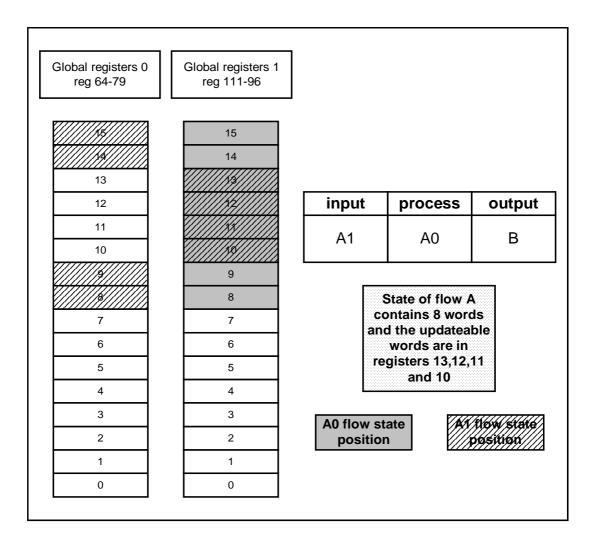

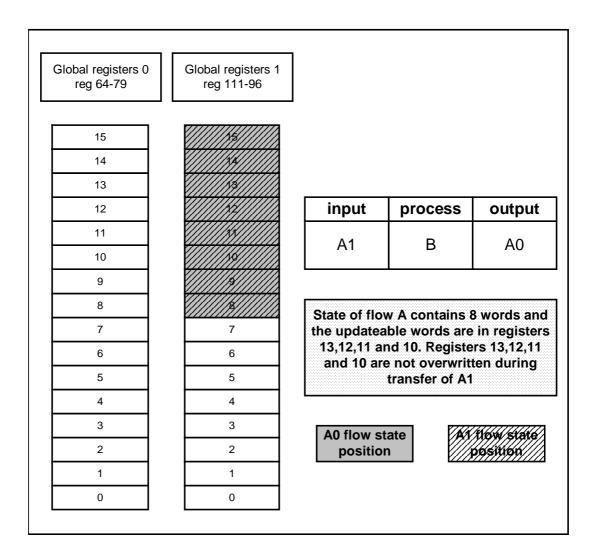

Global registers' switch is more complicated than local switch, this will be discussed in detail in the next chapter. When RPG transfers flow state to some of the global registers (from register 15 down to 4) indicates these registers by the GRSwitch mask (GRSwitch [7..2]). Every bit of this mask corresponds to a specific couple of registers and defines whether the state is in Global part 0 or Global part 1 (figure 4.1b). For example: