# **Technical University of Crete**

Department of Electronic and Computer Engineering

Microprocessor and Hardware Laboratory

# **Master Thesis**

# A Memory Efficient Intrusion Detection Architecture Using the Split-AC Pattern Matching Algorithm

**Author** Vasilis Dimopoulos

**Supervisor** Associate Professor Dionisios Pnevmatikatos

September 2006

### Table of Contents

| CHAPTER         | 1 – INTRODUCTION                                        | 5  |

|-----------------|---------------------------------------------------------|----|

| CHAPTER         | 2 – PATTERN MATCHING ALGORITHMS                         | 7  |

| 2.1 Ti<br>2.1.1 | HE BOYER-MOORE ALGORITHM                                | 8  |

| 2.1.2           | Adapting Boyer-Moore to Multiple Pattern Matching.      |    |

|                 | HE AHO-CORASICK ALGORITHM                               |    |

|                 | HE WU-MANBER ALGORITHM                                  |    |

|                 | ELATED WORK: MEMORY EFFICIENT AHO-CORASICK VARIATIONS   |    |

| 2.4.1           | Snort's Banded-Row Aho-Corasick                         |    |

| 2.4.2           | Bitmap Compression and Path Compression                 |    |

| 2.4.3<br>2.5 St | Bit-Split Finite State Machines                         |    |

|                 |                                                         |    |

|                 | 3 – THE SPLIT-AC ALGORITHM                              |    |

|                 | NTRODUCTION                                             |    |

|                 | HY USE THE AHO-CORASICK ALGORITHM                       |    |

| 3.2.1           | Aho-Corasick Simplification Heuristic                   |    |

|                 | PLIT-AC: GENERAL DESCRIPTION                            |    |

| 3.3.1           | Original Split-AC Algorithm                             |    |

| 3.3.2           | The Frequency Threshold Parameter.                      |    |

| 3.3.3           | Maximum Utilization of Available Space                  |    |

| 3.3.4           | Matching Patterns without Case Sensitivity              |    |

|                 | LGORITHM REVISIONS                                      |    |

| 3.4.1           | Split-AC Revision 1: Translating infrequent characters. |    |

| 3.4.2           | Split-AC Revision 2: State reordering.                  |    |

| CHAPTER         | 4 – RULES, RULE SETS AND RULE SUBSETS                   | 25 |

| 4.1 Sr          | NORT RULES                                              | 25 |

| 4.2 R           | ULE GROUPING                                            | 26 |

| 4.2.1           | Snort Rule Grouping                                     | 27 |

|                 | Fine-Grained Header Classification                      |    |

|                 | IVIDING RULE GROUPS INTO SUBSETS                        |    |

| 4.3.1           | Rule Set Division Algorithm                             |    |

| CHAPTER         | <b>5 – IDS ARCHITECTURE USING THE SPLIT-AC ALGORIT</b>  |    |

| •••••           |                                                         | 32 |

|                 | ITRODUCTION                                             |    |

|                 | YSTEM OVERVIEW                                          |    |

| 5.2.1           | Description                                             |    |

| 5.2.2           | System Inputs                                           |    |

| 5.2.3           | System Outputs                                          |    |

| 5.2.4           | Subsystems                                              |    |

|                 | EADER CLASSIFICATION                                    |    |

| 5.3.1           | Description                                             |    |

| 5.3.2           | Input Signals                                           |    |

| 5.3.3           | Output Signals                                          |    |

| 5.3.4           | Subsystems                                              |    |

| 5.4 FSM GROUP                                         |    |

|-------------------------------------------------------|----|

| 5.4.1 Description                                     |    |

| 5.4.2 Input Signals                                   |    |

| 5.4.3 Output Signals                                  |    |

| 5.4.4 Subsystems                                      |    |

| 5.5 FSM                                               | 40 |

| 5.5.1 General FSM Description                         | 40 |

| 5.5.2 Input Signals                                   | 41 |

| 5.5.3 Output Signals                                  | 41 |

| 5.5.4 Subsystems                                      | 42 |

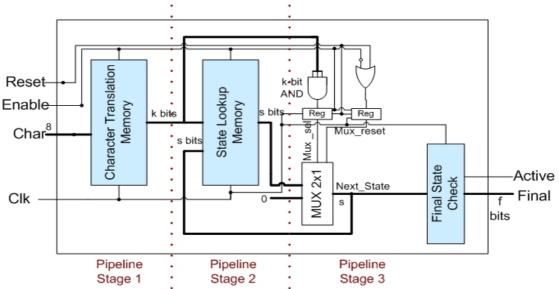

| 5.5.5 Revision 0 Specifics                            | 42 |

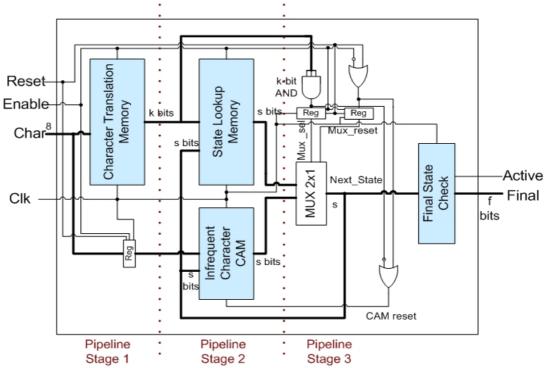

| 5.5.6 Revision 1 Specifics                            | 43 |

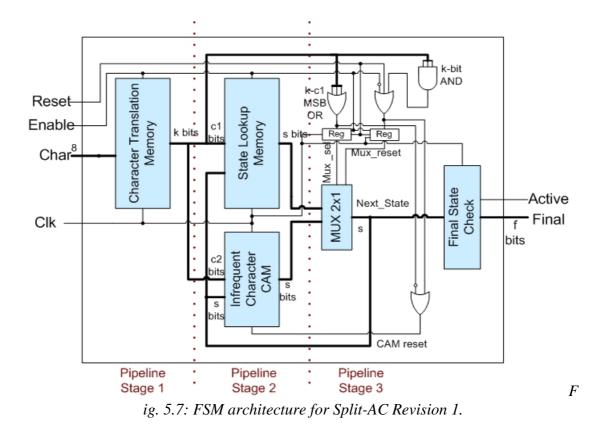

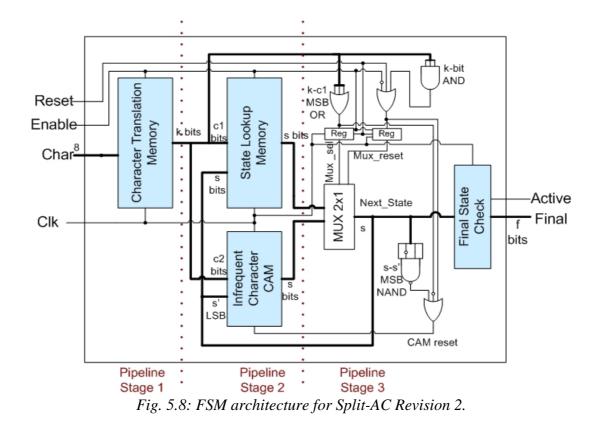

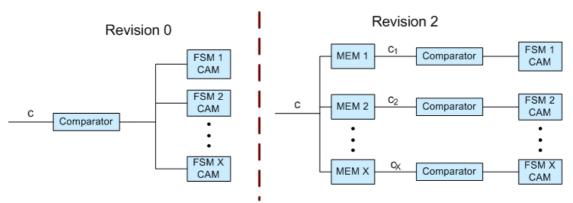

| 5.5.7 Revision 2 Specifics                            | 45 |

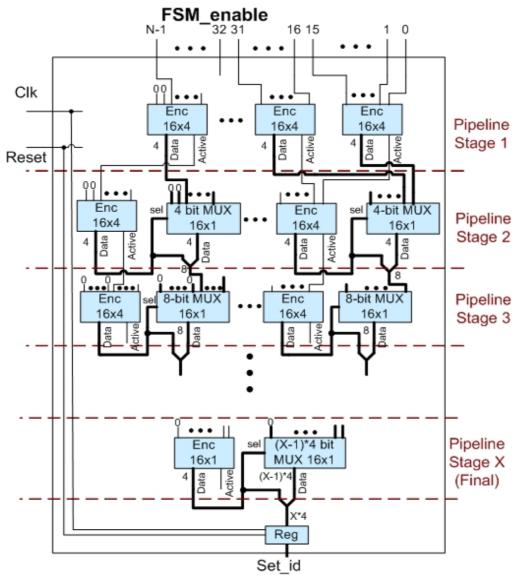

| 5.6 ENABLE ENCODER                                    | 46 |

| 5.6.1 Description                                     | 46 |

| 5.6.2 Input Signals                                   | 47 |

| 5.6.3 Output Signals                                  |    |

| 5.6.4 Subsystems                                      | 48 |

| 5.7 PRIORITY MUX                                      | 48 |

| 5.7.1 Description                                     | 48 |

| 5.7.2 Input Signals                                   | 49 |

| 5.7.3 Output Signals                                  |    |

| 5.7.4 Subsystems                                      |    |

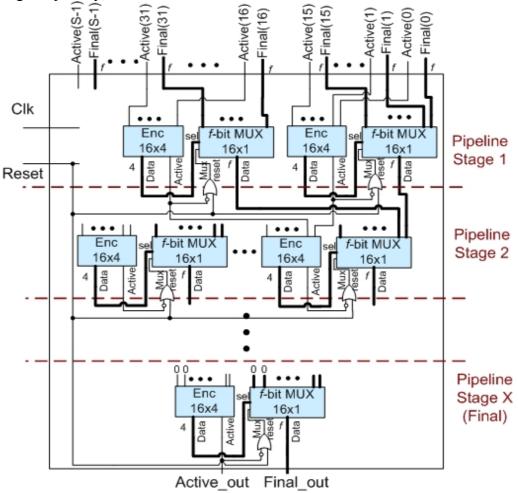

| 5.8 FPGA IMPLEMENTATION ISSUES: MEMORY ALLOCATION     | 50 |

| 5.8.1 Memory Allocation Examples                      |    |

| 5.9 IMPLEMENTATION                                    | 54 |

| 5.10 VALIDATION & TESTING                             | 55 |

| HAPTER 6 – RESULTS                                    | 57 |

| 6.1 INTRODUCTION                                      | 57 |

| 6.2 RULE CONFIGURATION                                |    |

| 6.3 RULE GROUPING AND SUBSET DIVISION RESULTS         |    |

| 6.4 SPLIT-AC BEHAVIOR                                 |    |

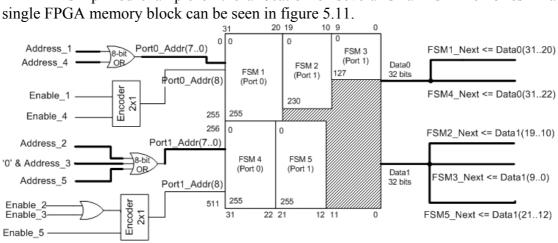

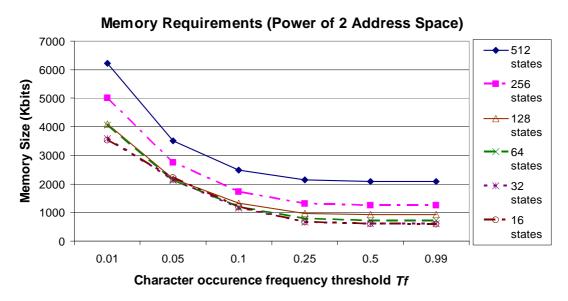

| 6.4.1 Split-AC Memory Requirements                    |    |

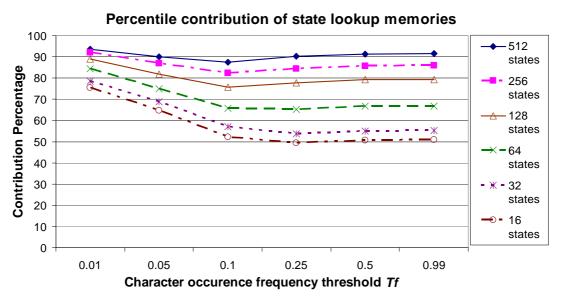

| 6.4.2 Character Translation and State Lookup Memories |    |

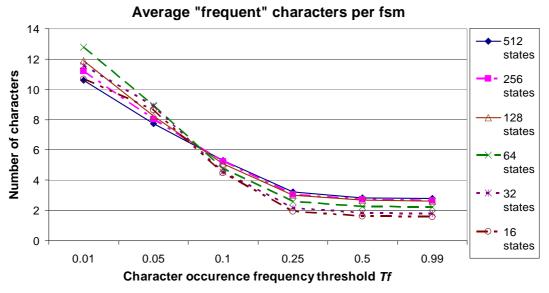

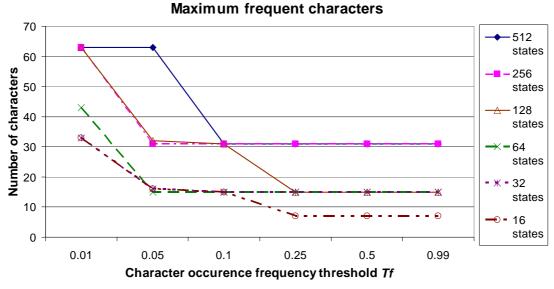

| 6.4.3 Frequent Characters per FSM State               |    |

| 6.4.4 Infrequent Character Requirements               |    |

| 6.5 ALGORITHM REVISION IMPACT                         |    |

| 6.6 FPGA IMPLEMENTATION                               |    |

| 6.6.1 FPGA Memory Allocation                          |    |

| 6.6.2 FPGA implementation Results                     |    |

| 6.6.3 Split-AC Against Bit-Split                      |    |

| 6.7 RESULT SUMMARY                                    |    |

| CHAPTER 7 – CONCLUSION                                |    |

|                                                       |    |

| REFERENCES                                            | 82 |

|                                                       |    |

# **CHAPTER 1 – INTRODUCTION**

In these past few years, an information revolution is taking place as the entire world has become connected into one global network, the Internet. People are able to communicate and cooperate with other people or access resources that may be located on the other side of the globe. Transactions over the Internet have become a steadily increasing part of global economy, while more and more Internet-only companies are emerging.

Of course, the Internet is not just about business. Academic work and research has benefited significantly, since the Internet can also serve as an enormous library where any information one is looking for can be accessed with the press of a button. Last but not least, the Internet also serves as a radical new method of entertainment: movies, music and literature are now available worldwide, while computer games such as Massively Multiplayer Online Role Playing Games, or MMORPGs, have created online gaming communities with tens of thousands or more members.

The only thing needed to access this huge world of information is a computer and an internet connection, both of which are becoming more widely available as time goes by.

However, this global availability of information raises considerable security issues. Malicious programs, or "viruses", can be easily transmitted from one computer to the next and can cause irregular operation of executing programs or deterioration of the operating system. Some types of viruses, such as "spyware" or "worms", may transmit personal information of a user or can leave a back-door open through which another user can access someone's computer. There are also many occasions where people with advanced programming skills were able to infiltrate secure networks and cause significant damage or steal corporate secrets.

In order to provide the necessary security, several methods have been developed. One of these methods is the "firewall", which can be either a software or a hardware platform. The firewall examines the headers of the packets being transmitted and received and allows only packets satisfying certain criteria, for example packets originating from a known secure network, to pass. Another widespread method of protection is the "antivirus" programs, which continuously check a computer and remove any known viruses that may have infected it.

A more recent manner of protection, which is not yet as widespread as the above two, is the "Intrusion Detection Systems", or IDS. Essentially a more evolved version of the firewall idea, an IDS examines not only the header of a packet, it also scans the payload in order to find specific patterns that constitute part of an attack or otherwise irregular behavior. Currently, Snort is the most widespread IDS and, due to the fact that it is open-source and freely distributed, is also the point of reference for all IDS-related work.

Although powerful in their capabilities, IDS can be rather computationally expensive because they rely on pattern matching algorithms to scan the entire payload of a packet and discover suspicious patterns hidden inside. A common type of attack used against intrusion detection systems, called Denial of Service (DoS), is to flood them with packets containing many suspicious patterns. In this case, the IDS must process a large number of packets and the processing of each packet takes time since many patterns are matched; if the packets arrive faster than the IDS can process them,

the IDS buffers eventually fill up and subsequent packets are either dropped, which means possible loss useful data, or allowed to pass through unchecked, which means that attacks can enter the system. This means that the pattern matching algorithms must be as fast as possible and perform in such a way that their throughput doesn't deteriorate when under attack traffic conditions.

The need for fast intrusion detection systems is made even more pressing by the hardware improvements that are rapidly increasing transmission speeds, which have currently reached multiple Gigabits per second. Since IDS are usually software based, the rate at which their processing speed increases is much smaller than that of the transmitting hardware.

Effective IDS implementations are software-based, because the hardware required to support the entire functionality of an IDS would be extremely large and complicated. However, a software-based IDS could utilize small amounts of hardware to perform certain tasks, such as pattern matching, which can be particularly expensive when performed in software.

The contribution of our work towards improving Intrusion Detection Systems is two-fold. First, we present a variation of the Aho-Corasick pattern matching algorithm, which we call "Split-AC", that is particularly suitable for hardware based IDS pattern matching and requires very low amounts of memory. There has been significant research on Aho-Corasick based algorithms, and our motivation was to develop a variation that would require the smallest possible amount of memory. Our second and last contribution is a simple IDS architecture that can fit on a single FPGA chip, performs packet header classification and pattern matching and can cooperate with a software-based IDS in order to significantly reduce the amount of work performed by the software.

The rest of this thesis is organized in the following manner. Chapter 2 provides a background in pattern matching by presenting some of the most widespread and effective algorithms. In chapter 3 we present the memory-efficient Split-AC algorithm as well as the revisions we made in order to improve some of the algorithm's aspects. Chapter 4 describes the rules being used, i.e. the manner in which suspicious network traffic is described, as well as the manner in which these rules are grouped into sets and subsets. Chapter 5 presents a detailed architecture for a hardware IDS implementation which can cooperate with software-based IDS and uses the Split-AC pattern matching algorithm, as well as the challenge that we faced trying to implement the IDS architecture in FPGAs and the manner in which the necessary validation was carried out. Finally, chapter 6 provides the detailed results for both the Split-AC algorithm and the FPGA implementation of the IDS architecture.

### CHAPTER 2 – PATTERN MATCHING ALGORITHMS

The topic of pattern matching has been the focus of significant research efforts in the past 30 or so years, with scientific areas such as bioinformatics, database searching and, of course, Intrusion Detection Systems relying heavily on the performance of the underlying pattern matching algorithms. Specifically, Intrusion Detection Systems use pattern matching algorithms to uncover certain suspicious strings inside the payload of a packet that may constitute part of an attack against the system or otherwise unorthodox behavior. The continued proliferation of Intrusion Detection Systems has helped rekindle interest in this scientific topic.

In this chapter we will first present some of the most effective pattern matching algorithms their important variations. At the second part of this chapter we present recent work on memory-efficient variations of the Aho-Corasick algorithm, since our work is also based on the Aho-Corasick algorithm.

### 2.1 The Boyer-Moore Algorithm.

First published in 1977 [1], the Boyer-Moore (BM) algorithm still remains the most efficient method for locating a single pattern with a best- and average-case search cost of O(N/m), where N is the length of the text being examined and m the length of the pattern. The worst case search cost of the algorithm is O(N\*m). Practically, this algorithm performs best for large patterns and alphabet size.

The first step in this algorithm is the construction of a lookup table, the *bad*character shift table, which has a size equal to the size of the used alphabet (e.g. 256 entries for byte matching). For every possible input character, the table holds the distance of the *rightmost* instance of that character from the end of the pattern or m if the character doesn't appear in the pattern. For example, the shift table for the pattern "banana" is shown in table 2.1.

TABLE 2.1

The bad character shift table for the pattern "banana". The symbol \* means any

| other character. |   |   |   |   |

|------------------|---|---|---|---|

| Character        | a | b | n | * |

| Value            | 2 | 5 | 1 | 6 |

The algorithm also uses another table, the *good suffix shift* table. This table holds m+1 entries, with each entry *j* indicating where we can find a reoccurrence of the *m*-*j* suffix characters.

The Boyer-Moore algorithm aligns the pattern with the start of the text, but always tries to match it from right to left. As long as text and pattern character matches, we keep proceeding towards the start of the pattern. Whenever a text character c is found that doesn't match the corresponding (m-j)-th pattern character, the entire pattern is shifted right by an amount of max(GS[j], BC[c] – j), where GS[j]

is the *good suffix shift* table value for the position of the mismatch and BC[c] the *bad character shift* value corresponding to the specific text character.

#### 2.1.1 Horspool's Variation.

A simplification of the original Boyer-Moore algorithm [2], this algorithm goes to show that a simpler but "dumber" algorithm can be faster than a complex and "smarter" algorithm. Horspool showed that using only the *bad character shift* table is usually faster for large alphabets (such as the ASCII table) and non-periodic patterns.

Horspool's variation has a best- and average-case cost of O(N/m) and a worstcase cost of O(N\*m), much like the original Boyer-Moore algorithm. The essential difference between the two is that Horspool performs more character comparisons but each comparison is faster than in Boyer-Moore.

#### 2.1.2 Adapting Boyer-Moore to Multiple Pattern Matching.

The Boyer-Moore algorithm can be adapted to simultaneously search for a set of strings, as shown in [3], by inverting some of the original ideas. The patterns are combined in a suffix-tree structure, which initially aligned with the *end* of the text, the patterns are matched from *left to right* and in case of a mismatch the tree is *shifted to the left*.

In this algorithm, the *bad character shift* table recommends a shift based on the distance from the start of the pattern of the *leftmost* instance of a character c in any of the patterns (instead of the *rightmost* appearance, as was the case with the traditional algorithm).

On the other hand, instead of the traditional *good suffix shift* table, this algorithm uses a *good prefix shift* table, which recommends a shift to the next occurrence of a complete prefix that has already been seen as a substring of another pattern, or shift to the next occurrence of some prefix of the correctly matched text as the suffix of another pattern in the set.

This algorithm has a best- and average-case search cost of O(N/m'), where m' is the length of the *smallest* pattern in the set. The fact that no shift can be larger than the length of the smallest pattern is one of the main drawbacks of this approach. Another drawback is that for a large group of patterns with reasonably varied contents, the bad character shift table (which is the main performance-giving mechanism) becomes saturated with very small values, causing the algorithm to have super-linear search cost.

### 2.2 The Aho-Corasick Algorithm

When concerned with the conditions under which a pattern matching algorithm is preferable, the Aho-Corasick (AC) algorithm lies on the opposite end of the spectrum from both Boyer-Moore and Wu-Manber. The AC algorithm checks

each text character only once regardless of how many or how small patterns we are trying to match, making it ideal for sets with very small patterns.

Since it was first proposed [4] in 1975, this algorithm has remained one of the standard methods of pattern matching, especially for very large groups of patterns (tens of thousands). During the initial phase of the algorithm, all patterns are combined in a syntax tree structure, in which every edge represents a character, every node has a unique number id, and the route from the initial node to another represents a certain pattern (or sub-pattern). Patterns that share a common prefix also share a number of nodes equal to the length of the prefix. The nodes coinciding with the end of a pattern are called "final" nodes.

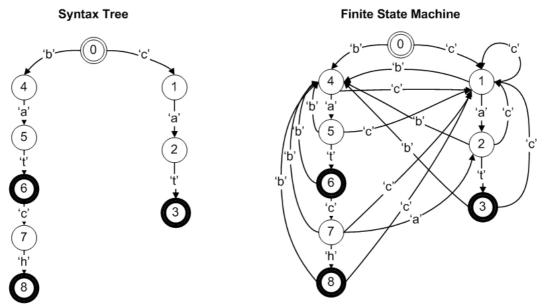

After all the patterns have been added the syntax tree, specific algorithms are used to convert that tree first into a non-deterministic automaton and, finally, into a deterministic automaton or finite state machine. The syntax tree and derived deterministic automaton corresponding to the pattern set {"bat", "batch", "cat"} is shown in figure 2.1. Note that during the conversion from syntax tree to finite state machine, the number of "final" states (not the number of total nodes) may increase. Such an effect does not occur in figure 2.1 due to the simplicity of the example.

Fig. 2.1: The Aho-Corasick syntax tree and the derived FSM for matching the patterns "bat", "batch" and "cat". Each node represents a state. The arrows represent transitions for specific characters. Nodes with a bold outline represent "final" states.

The finite state machine shown in figure 2.1 is slightly simplified. In reality, there should be arrows from each node leading back to the initial state, state 0, for all characters not already present in transitions from that node. For example, node 8 has defined transitions for characters 'b' and 'c'; for all other characters the transition is back to the initial state.

After the finite state machine has been generated, the pattern matching process is extremely simple: the fsm starts at the initial state and begins processing the characters of the text one after the other. For each input character the fsm performs exactly one transition. Whenever the fsm arrives at a "final" state then a pattern has been successfully matched. The non-deterministic automaton can also be used to match the contained patterns. However, in that case the automaton may execute up to 2N transitions. The other difference between the non-deterministic and the deterministic automaton is that the non-deterministic usually has significantly less transitions per node, a fact that has been exploited in several memory-efficient variations of the Aho-Corasick algorithm.

The strongest point of the Aho-Corasick algorithm can also be its major weakness: the fact that the number of character comparisons is precisely N. When searching for a set of long patterns using another algorithm such as multi-pattern Boyer Moore or Wu-Manber (description follows), the average case lookup cost is roughly O(N/m): for a large value of m, these algorithms perform only a fraction of the character comparisons that AC does. However, the tables turn if there is even one small pattern (one or two characters long) in the set. In that case, the other algorithms will have super-linear search cost most of the time. For a minimum pattern length of 2 or 3 characters, the Wu-Manber algorithm will *always* have super-linear cost.

Another drawback of the Aho-Corasick algorithm is its extremely large, by comparison to the other methods, memory needs. Fast implementations of the algorithm hold at each node an array of 256 pointers to next states, one for each possible character input. For software implementations of the algorithm using 4 bytes per pointer this translates to 1Kbyte per node. The large memory requirements of the algorithm make hardware implementations rather challenging.

#### 2.3 The Wu-Manber Algorithm

A more recent entry to the field of pattern matching, the Wu-Manber [5] pattern matching algorithm was first published in 1994 and is currently considered one of the most efficient pattern set matching algorithm, with a best-case search cost of O(N/m).

The Wu-Manber algorithm (WM), which also provides the pattern matching mechanism for the Snort IDS, could be considered a radical evolution of the Boyer-Moore algorithm since it also relies on bad character shift mechanism to avoid certain checking parts of the text. Specifically, a *shift* table holding  $2^k$  entries, instead of the BM's 256 entries, is used. The parameter k is the size in bits of the generated hashing index that will be explained shortly.

The contents of the shift table are initially set to m-B+1, where m is the length of the shortest pattern in the set and B is the number of characters that are hashed together. Afterwards, starting from the first character and proceeding to position m-Bone character at a time, the B sequential characters are hashed together (using the same hash function every time), producing a k-bit wide value h. The shift table is then updated so that the value for index h is equal to the minimum between the previous shift table contents and the distance of the last one of the B hashed characters from the m-th position. In essence, the shift table holds the minimum distance of the rightmost appearance of every possible hashing of B sequential pattern characters value from the m-th position. For example, the shift table for the pattern "banana" and for B=2 is shown it table 2.2.

TABLE 2.2

The Shift table of the Wu-Manber algorithm for the pattern "banana". The \*

character means any other

| character means any other. |    |    |    |   |

|----------------------------|----|----|----|---|

| Hash Index                 | ba | an | na | * |

| Shift amount               | 4  | 1  | 0  | 5 |

Apart from the *shift* table, the algorithm uses two more tables: the *hash* table and the *prefix* table. If *shift*[h]=0, then *hash*[h] holds a list of patterns whose B "last" characters (i.e. characters in positions *m*-*B* to *m*) hash into value *h*, while *prefix*[h] holds a list of hash values, one for each pattern, of the *B*' prefix characters of the pattern.

The search procedure of the Wu-Manber algorithm is the following: starting from position m in the text, the B previous characters are hashed together and a value h is generated. If *shift*[h] is non-zero, then we proceed to the right by *shift*[h] characters and repeat the process. If *shift*[h] is zero, then the B' text characters in the positions where the prefixes of the patterns would be are hashed together and form h'. h' is then compared with the contents of the *prefix*[h] list. If any of the prefix[h] values match h', then the corresponding pattern from *hash*[h] is selected and compared against the text one character at a time.

In general, the Wu-Manber algorithm has proven to be very effective for large pattern sets when the minimum pattern length is not very short (i.e at least 5 characters). The fact that the algorithm is parameterized so that a user can select the B, B' and k values that best fit his resources and the problem at hand is another significant strength of the algorithm. The algorithm major weakness is that the performance relies heavily on the length of the minimum pattern.

### 2.4 Related Work: Memory Efficient Aho-Corasick Variations

In this section we present related work on memory-efficient variations of the Aho-Corasick algorithm. We focus on Aho-Corasick variations and not memory-efficient algorithms in general because the algorithm we developed and which is presented in Chapter 3 is also a variation of the Aho-Corasick algorithm.

### 2.4.1 Snort's Banded-Row Aho-Corasick

The first memory efficient variation we examine [6] comes directly from one of the people behind Snort. The proposed variation supports two different state types: states with a full, 256-entry lookup table and states with banded-row format lookup tables. Typically, the full lookup table is used in states located near the initial state of the fsm, since they tend to have a large number of transitions, while the banded-row format is used in states located further away, since they tend to have a sparse lookup table.

Typically, the lookup table for a state of the Aho-Corasick automaton is an array of 256 values. In this array, a non-zero value signifies a valid transition to a specific state, while zero signifies a transition back to the initial state.

A lookup table using banded-row format holds all the elements located between the first and the last non-zero contents of the lookup table, the distance between the first and last non-zero elements and the position of the first non-zero element.

A simple example of a state lookup table and the corresponding banded-row format is the following:

| Original Lookup table   | :000240007060000000 |

|-------------------------|---------------------|

| Number of elements      | : 8                 |

| First non-zero position | : 4                 |

| Banded-row table        | :8424000706         |

The lookup process for banded-row format is the following. When an input character c arrives and the fsm is in a state with a banded-row lookup table, the character is first checked if it is within the banded area. If c lies before the first non-zero transition or greater is than the sum of the first position and the number of elements (thus failing after the last element), then the transition is 0 and the fsm returns to the initial state. Otherwise, the first non-zero position is subtracted from c and the resulting value is used to directly access the banded-row lookup table.

The banded-row format provides substantial memory compression when the lookup table is sparse (i.e. has many 0 values) and the non-zero values are located close together. The disadvantage of this method is that the performance, memorywise, depends heavily on the position of the non-zero values. For example, a 256 entry lookup table in which only the first and last entries were non-zero would receive no benefits from this approach.

### 2.4.2 Bitmap Compression and Path Compression

Both techniques are presented in [7] and were based mainly upon the Eatherton tree-bitmap algorithm [8] which is widely used for IP routing. Also, both techniques have been designed for the non-deterministic Aho-Corasick automaton because it has significantly less transitions per state than the deterministic automaton does.

The *Bitmap Compression* method is applied in all fsm states and uses a 256 entry bitmap and an array of non-zero transition pointers instead of the typical, 256 pointer state lookup table. A bit j of the bitmap is set if the fsm has a valid transition for input character j. The array of pointers holds sequentially all the non-zero transitions. A small example of the resulting bitmap and transition array is the following:

| Original Lookup table | :000240007060000000  |

|-----------------------|----------------------|

| Bitmap                | :0001100010100000000 |

| Transition Array      | : 2 4 6 7            |

When looking up the next state transition for a specific character c, we first check if bit j is set. If the bit is cleared then the non-deterministic automaton performs a failure transition. However, when the bit is set a popcount operation is performed on the bitmap up to position c (i.e. we count all the '1' bits appearing in the bitmap before bit c). The result of the popcount is then used to address the transition array, which returns the appropriate next state

On the other hand, the *Path Compression* technique can not be applied to all fsm states. It applies only to the states from which a chain of states with only one transition per state begins (as occurs for unique pattern suffixes inside the Aho-Corasick non-deterministic finite automaton). For example, there is a state A inside the automaton from which only the following chain of transitions begins:

$$A \rightarrow B \rightarrow C \rightarrow D.$$

Instead of allocating space for four nodes, only node A is created containing the additional information of the suffix that needs to be matched in order to perform the  $\rightarrow$  B  $\rightarrow$  C  $\rightarrow$  D transitions. In this way, whenever the automaton reaches state A we simply check if the following text characters match the specific suffix.

These two methods can reduce the required memory significantly, but have other major disadvantages. First of all, both have been designed for use with the non-deterministic AC automaton which can execute up to 2N state transition for an N-sized text. The *Bitmap Compression* method can be adapted to deterministic automatons, in which case it will offer diminished memory gains, but the *Path Compression* method cannot be utilized in deterministic fsms.

The second major disadvantage concerns the popcount operation necessary for the *Bitmap Compression* technique. The hardware required for a 256-wide popcount would be a significant cost due to the operation's complexity. An easier way of implementing the popcount is to maintain running sums every k bits of the bitmap and perform only a k-bit wide popcount (which can easily be performed by a  $2^k$  sized lookup table holding all possible popcount results). However this would come with an increase in memory requirements.

#### 2.4.3 Bit-Split Finite State Machines

A rather novel and particularly promising approach to the Aho-Corasick algorithm was proposed in [9].

In a nutshell, the idea is that instead of having one large fsm processing an 8bit character with 256 possible transitions, you have 8 small bit-split fsms, each of which has 2 possible transitions per state and processes a different bit of the character. Each bit-split fsm state also contains a g-bit wide partial-match vector, where g is the number of patterns in the original fsm, which indicates the patterns that are partially matched in this state of the bit-split fsm.

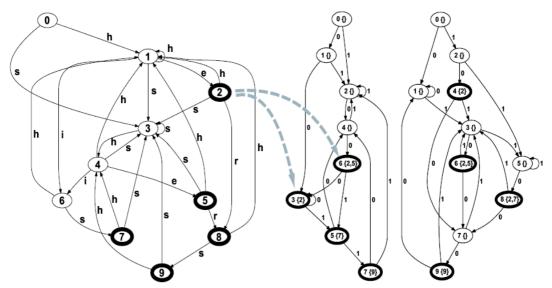

Figure 2.2[9] shows an example of an Aho-Corasick fsm for matching the pattern set { "he", "she", "his", "hers"} and the two derived bit-split fsms  $B_3$  and  $B_4$ , which process the input character's bits 3 and 4 respectively.

fig. 2.2 [9]. The initial Aho-Corasick fsm (left) and the resulting bit-split fsms handling input bits 3(center) and 4 (right). States with a bold outline represent "final" states

A bit-split fsm  $B_i$  is constructed from the initial Aho-Corasick fsm, called D, based on the following procedure. Starting from the initial state 0 of D, state 0 of  $B_i$  is constructed having a state set of {0}. The numbers in a bit-split state set correspond to D states. For all the states contained in the state set of  $B_i$ 's State 0, we find which Dstates can be reached when bit i of the input character is '0': these D states form the state set of a new  $B_i$  state. The same process is repeated for the D states that can be reached when bit i of the character is '1', resulting in another new  $B_i$  state. In the example of figure 2.2, when starting from D state 0 then D states 0 and 1 are reached for a '0' value of bit 3, while D states 0 and 3 are reached for a '1' value of bit 3. This process is repeated until the next states for all  $B_i$  states have been constructed.

When processing an input text, all 8 bit-split fsms perform independent transitions based on their corresponding input bit values. After the transition, each small fsm outputs the partial match vector of the state that it is currently located. The partial match vectors are AND-ed together and the resulting final match vector will have 1 at a certain location only if all 8 bit-split fsms have located the corresponding pattern.

The standard Aho-Corasick fsms aren't necessarily split into 8 bit-split fsms. The authors describe how, depending on the situation, it can be more effective to split it into 4 bit-split fsms with each fsm handling 2 character bits and each state having 4 possible transitions, or into 2 bit-split fsms with each one processing 4 character bits and each state having 8 possible transitions

The authors show that their algorithm is very effective in terms of both performance and memory requirements. They also present an architecture for hardware implementation of the algorithm that can be updated at runtime whenever the rule set changes. All in all, this algorithm seems to have no discernible major disadvantages.

### 2.5 Summary

In this chapter we have presented several of the most important pattern matching algorithms currently used. On one hand we have algorithms such as Boyer-Moore or Wu-Manber which take advantage of specific information from the pattern characters to skip over portions of the examined text. These algorithms usually have sublinear lookup cost, but their performance is restricted by the length of the shortest pattern in the set: a pattern of one or two characters can cause these algorithms to have superlinear cost. Since we frequently have patterns that are 1 to 3 characters long in Intrusion Detection Systems, these algorithms are not particularly suitable.

On the other hand, we have the Aho-Corasick algorithm. The idea behind this algorithm is to combine all the patterns into one large finite state machine and then examine the characters of the text one after the other. This algorithm is very powerful due to the fact that the cost to examine a text is always linear, regardless of the number of patterns or of their lengths. However, the major disadvantage of the Aho-Corasick algorithm is that it requires very large amounts of memory.

The suitability of Aho-Corasick to Intrusion Detection Systems was the reason that inspired us to develop the Split-AC algorithm, presented in the next chapter, which is based on Aho-Corasick while requiring substantially less memory.

## CHAPTER 3 – THE SPLIT-AC ALGORITHM

### 3.1 Introduction

This chapter is dedicated to the algorithm we developed for reducing the memory requirements of the Aho-Corasick pattern matching algorithm. We call this algorithm "Split-AC", which is short for Split-Aho-Corasick.

In the first part of this chapter we present the reasons for selecting the Aho-Corasick as the basis for our work as well. In the second part we present the ideas that led to the development of the Split-AC algorithm as well as a general description. The third and final part presents the original Split-AC algorithm in detail, as well as the two subsequent revisions that were made.

### 3.2 Why Use the Aho-Corasick Algorithm

There are several reasons behind our choice of the deterministic Aho-Corasick algorithm over others.

The first reason behind our choice has to do with the scientific area we are targeting: Intrusion Detection Systems. Snort rules, which are used as a reference point among all IDS-related research, specify patterns of various lengths. The problem is that several patterns are only one or two bytes long. The performance of "fast" pattern matching algorithms, i.e. algorithms that skip over sections of the text, such as Wu-Manber, is directly proportional to the length of the minimum signature. For a minimum pattern length of 3, a modest implementation of the Wu-Manber algorithm that hashes 2 characters per iteration would compare every text character *at least once*. The Aho-Corasick algorithm checks every text character only once.

Another reason is the relative simplicity of implementing the algorithm in hardware. A state lookup memory and a register holding the current state are enough: during each cycle the next character arrives, which we use along with the current state to address the lookup memory and find the next state. Algorithms that can move back and forth in the text present a larger complexity to implement.

Also, we want to combine accurate pattern matching with fine-grained packet header classification. The header classification and rule grouping processes described in section 4.2.2 result in the creation of nearly 400 different rule sets, each of which may require a pattern matching engine. This raises synchronization issues, i.e. knowing what position of the text each engine is examining. Since every Aho-Corasick fsm processes one character at a time, at any time all the fsms will be examining the same character of the text. This also solves the problem of maintaining and updating parts of the payload on-chip: the entire payload can be kept off-chip and fed to the fsms one character at a time. If an algorithm that text-skipping was used, there would be an additional difficulty of maintaining a payload segment for each instance of the algorithm.

#### 3.2.1 Aho-Corasick Simplification Heuristic

During our experimentations with the Aho-Corasick algorithm, we found a simple way to slightly reduce its complexity. Traditionally, each state of the fsm has a list of patterns or some other information associated with itself in order to understand during the search phase if it is a "final" state or not. In hardware implementations, an extra bit would be needed for the state lookup contents that would indicate which states are final and which not, or otherwise a logic block that would check if the current state number belongs to a final state.

That need for additional information can be eliminated by a simple state renaming, in which all "final" states are assigned numbers from 1 to F, with F being the total number of "final" states. In this way, we know we are at a final state whenever the current state number is between 1 and F (inclusive). Note that this makes easier only to know *if* we are at a "final" state; if we want to know the patterns that have been matched we still need to check a pattern list.

We can utilize this information by having an abstraction layer responsible for monitoring and managing the fsms, as well as storing the information concerning which pattern corresponds to every final state. Whenever an fsm reaches a final state, it informs the abstraction layer of the final state that was reached and from there on the abstraction layer knows precisely which pattern was matched.

This heuristic has been utilized fully in every version of the split-AC algorithm.

### 3.3 Split-AC: General Description.

The Split-AC algorithm was based on several observations concerning the rule groups and the corresponding Aho-Corasick finite state machines that are generated from a fine-grained header classification.

Our first observation was that the fsms corresponding to most rule groups had valid transitions, i.e. transitions not leading back to the initial state, for only a fraction of all the possible input characters: many Snort rule patterns use only alphabet characters, arithmetic digits or some standard symbols(e.g. '\'). Also, a significant number of rule groups require Aho-Corasick fsms of only a few dozen states or less, which has a similar effect since the number of different characters appearing in transitions is always less than the number of states. This observation led us to search for a method to reduce the number of input bits by grouping together the characters that cause valid transitions. Reducing the number of character bits by *n* will reduce the size of the state lookup table by  $2^n$ , since we will require, for example, only 32 or 64 transitions per state instead of the typical 256.

The second observation was that not all characters appear with the same frequency in transitions of an Aho-Corasick fsm. Some characters may appear in transitions from nearly every state, as is the case for the first character of every pattern, while others may appear transitions from only one or two states. In the example of figure 2.1, it is apparent that characters 'b' and 'c', which are initial pattern characters, appear in every state while character 'h' appears in only one transition. This observation led us to consider the possibility that it may be more efficient in terms of memory to store only the transitions of frequently appearing

characters in the state lookup table and use some other, possibly more resource expensive approach, like Content Addressable Memories, to discover the next state for specific (character, state) pairs.

Finally, there can be several characters that don't appear in even one transition in an Aho-Corasick fsm. Whenever such a character is observed, the fsm always returns to the initial state regardless of its previous state.

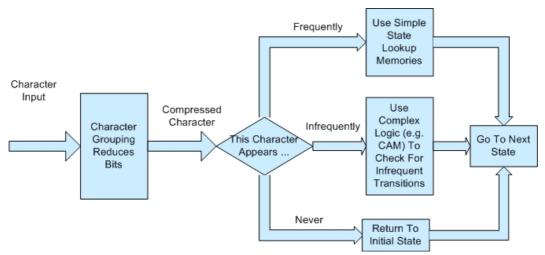

A simple diagram visualizing all the above is shown in figure 3.1.

Fig. 3.1: An abstract diagram showing how the Split-AC algorithm operates.

#### 3.3.1 Original Split-AC Algorithm

We start off with a typical Aho-Corasick deterministic fsm with S states. First of all, we define as f(c) the occurrence frequency of character c in transitions of this fsm. The value for f(c) is calculated by summing the number of states that have transitions for input character c and dividing the sum with S. Since the number of occurrences for any character c is between 0 and S, the value for f(c) is  $0 \le f(c) \le 1$ .

We now define the frequency threshold as  $T_{f}$ . Any character c with an occurrence frequency f(c) greater or equal than the threshold is considered a *frequent character*. Accordingly, valid (i.e. not leading back to the initial state) transitions the fsm makes for frequent characters are called *frequent transitions*. Characters with an occurrence frequency smaller than the frequency threshold but greater than zero are considered *infrequent transitions*. Finally, characters with a zero occurrence frequency are considered *non-existent characters*. This splitting of the characters into three groups is the reason we named the algorithm "Split-AC".

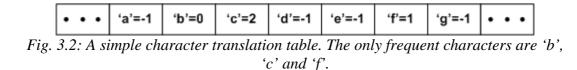

We define the total number of frequent characters as *K*. In order to perform the character grouping and "compress" the character we use a simple lookup table of 256 entries, which is addressed by the input character. This table, which we call "character translation table", holds a value of '-1' for all infrequent and non-existent characters and a different value from 0 to *K*-1 for each one of the *K* frequent characters. The width of the character translation table is defined as  $k = \log_2(K+1)$  bits, rounded up. The "+1" in this formula is due to the '-1' translation value for infrequent and non-existent characters, which must also be taken into account. We name the result of this

lookup table "translated character". A simple example of a character translation table is shown in figure 3.2.

At this point we define the number of bits needed to represent the state of the fsm with  $s=\log_2(S)$ , rounded up. Whenever the input character is a frequent character we use a second lookup table, the "state lookup memory" to find the next state of the fsm. This table has  $2^{(s+k)}$  entries and is *s* bits wide. This table is addressed by the current fsm state and the translated character: the state provides the *s* most significant address bits while the translated character provides the *k* least significant bits. In this manner, we can imagine the state lookup memory as being divided into  $2^n$  blocks, one for each state, with each block holding  $2^k$  transitions, one for each possible value of the translated character. A simple example of a state lookup memory is shown in figure 3.3. For each state the last transition will be empty because of the '-1' value (binary: "11...11") that is reserved for infrequent and non-existent characters.

Fig. 3.3: An example of how the state lookup table is divided into different blocks. The fsm has 256 states and 61 frequent characters. The grayed-out segment in each state represents unused space.

The manner in which infrequent characters are processed depends mostly on the target platform for the algorithm. If the split-AC algorithm is to be implemented in software, the "infrequent" character transitions for each state would probably be maintained in a linked list that would be examined sequentially whenever an "infrequent" character was observed. On the other hand, if we wanted to implement the algorithm in hardware a reasonable solution that offers high performance is to use a series of comparators or a Content Addressable Memory: in either case the current fsm state and the input character would be fed as inputs and the result would be the appropriate next state.

Taking all of the above into account, the lookup procedure for the Split-AC algorithm can be summarized in three simple steps.

#### Algorithm 3.1: Text scanning procedure of the Split-AC algorithm

- Step 1. The next input character c is used to address the character translation table, which responds with the corresponding translated character c'.

- **Step 2**. If the translated character c' is a "frequent" character, use the state lookup table to find the next state. Otherwise, the next state is found by checking the "infrequent" character transitions for input character c.

- **Step 3**. Check if the next state is also a "final" state. If it is "final", a pattern was located. Return to Step 1.

#### **3.3.2** The Frequency Threshold Parameter.

The only user defined parameter of the algorithm is the frequency threshold  $T_{f}$ . In this manner, a user can adapt the algorithm according to resources he has available. A low threshold value, close to 0, means that most characters are considered frequent. This in turn means that the character translation table has many non-zero entries, the translated character will possibly be more bits wide and the state lookup table will increase in size accordingly. The benefit of having a small threshold is that the effort or logic required for infrequent transitions is significantly smaller.

On the other hand, a large threshold value (close to 1), means that there are fewer frequent characters and the character translation and state lookup tables are much smaller. However, in this case a lot more logic or effort will be required for the infrequent characters

#### 3.3.3 Maximum Utilization of Available Space

As we mentioned section 3.3.1, only the characters with an occurrence frequency equal or greater than the frequency threshold  $T_f$  are considered frequent. However, this first allocation may result in some space remaining unused. For example, consider the case where 10 frequent characters have been selected based on the threshold: the translated character is 4 bits wide and the state lookup table has allocated 16 frequent transitions per state, out of which only 10 are used and 1 is reserved. In this case, we could accommodate another 5 frequent character essentially for free.

We take this fact into account by performing a second frequent character selection. After the initial frequent character selection (based on the frequency threshold  $T_f$ ) is completed and the *k* number of bits has been set, we calculate the number of unused transitions per state. Let that be *X*. We then select the *X* infrequent

characters with the largest occurrence frequencies and convert them into frequent characters.

#### 3.3.4 Matching Patterns without Case Sensitivity

An issue with every pattern matching is if and how they support case insensitive patterns matches. By case insensitive we mean that no distinction is made between capital and small letters. For example, if are searching for pattern "foo" in a case insensitive manner, then the algorithm must also be able to match "Foo", "FOO", "fOo" etc.

When searching only for case insensitive patterns, the answer is simple: use a lookup table to convert each lowercase letter into the equivalent uppercase. The situation gets pretty when a pattern set contains both case sensitive and case insensitive patterns. The usual solution is to search for all patterns in a case *insensitive* manner and to reexamine the input text in a case *sensitive* manner whenever a case *sensitive* signature is discovered.

For our hardware implementation of the algorithm, we decided against adding support for concurrent sensitive/insensitive pattern searches. This decision was based on the significant increase of implementation complexity due to the fact that text portions would need to be reexamined on occasions. Instead, whenever case sensitive and case insensitive patterns are contained in the same pattern group we will separate them in two smaller groups, one containing only the sensitive patterns while the other contains the insensitive ones, and perform two concurrent searches using the corresponding fsms.

The Split-AC algorithm can easily support case insensitive patterns matches due to the character translation table it uses. First, all patterns in a case insensitive pattern set are converted to either uppercase or lowercase (we chose uppercase). Afterwards, whenever a character C is placed in the character translation table and receives a value x, the corresponding lowercase character c receives the same value x.

In the revisions of the Split-AC algorithm, this mechanism is adequate since both frequent and infrequent characters are stored in the character translation table. However, in the original Split-AC algorithm this by itself is not enough because the infrequent transition mechanism checks the *input* character, not the translated one; since all pattern characters are converted to uppercase, a lowercase character would be ignored. In answer to this problem, a case translation table must also be used to convert lowercase characters to uppercase.

### 3.4 Algorithm Revisions

We developed the Split-AC algorithm in order to implement it in hardware. For the hardware implementation we decided on using a Content Addressable Memory-like structure for storing and checking the infrequent character transitions. This CAM is addressed with the input character and the current fsm state and responds with the corresponding next state or with the initial state 0 if no such transition exists. CAM structures are very powerful and convenient, but they are also very demanding in resources: if a CAM contains X data entries and the CAM input is Y bits wide, then during each cycle *every* data entry is compared against the input in order to find a match. This translates to X\*Y bit comparisons. With this in mind, we can estimate the cost of a CAM as roughly proportionate to the sum of input times the number of data entries. The output bits of the CAM are not of equal importance, since they perform some work only when a CAM entry has been matched.

The number of data entries in the CAM obviously can't be reduced, since that would mean omitting some transitions. Instead, we focused on reducing the number of input bits. In revision 1 we show how we can reduce the number of character input bits for the CAM at the cost of increasing the character translation table size. Finally, revision 2 shows how the state input bits of the CAM can be reduced.

The two revisions are independent and complementary: either or both can be applied and the received benefits are additive, since they target different aspects of the problem. However, during the algorithm's development we had the idea for revision 2 after revision 1 had already been implement. As a result, whenever we refer to revision 2 we assume that revision 1 has already been applied.

### 3.4.1 Split-AC Revision 1: Translating infrequent characters.

In the original algorithm, the CAM receives the untranslated 8-bit character as input. However, it is quite possible that there will be only a handful of infrequent characters in the Split-AC fsm, which could be represented by a lot less than 8 bits. To that end, we tried translating the "infrequent" characters much like we translate the "frequent" ones.

In the original algorithm Split-AC described in section 3.3.1, a total of *K1* frequent characters are selected, for which the character translation table stores values from 0 to *K1*-1. Now, we define as *K2* the number of different infrequent characters. These characters are also stored in the character translation table and each one of the infrequent characters is assigned a value from  $2^{c1}$  to  $2^{c1} + K2$ -1, where  $c1 = \log_2(K1)$  rounded up is the number of bits needed to represent the different frequent characters.

The width of the character translation table's result is now  $k = \log_2(2^{cl} + K2)$  bits, rounded up, in order to represent both frequent and infrequent characters. Additionally, the value '-1' (i.e "11...11"), which was previously reserved for both infrequent and non-existent characters, is now reserved exclusively for non-existent characters. This value has an increased responsibility in this revision, because it informs us that there exists no transition, frequent or infrequent, for a character, which means that both the frequent character state lookup table and the infrequent character CAM must be ignored and the next fsm state will be 0.

For all frequent characters, the translated character value will be from 0 to K1-1 and, as such, will have the *k*-*c1* most significant bits equal to 0. Conversely, if any of the *k'*-*c1* most significant bits is 1 then the character is definitely not a frequent one. We take advantage of this fact by using only the *c1* least significant bits to address the state lookup table, as happened in the original algorithm, and ignoring the result of the table if any of the *k*-*c1* most significant bits is 1. Note: the number of character bits for the state lookup table is the same as in the original algorithm, the difference is that the translated character is now more bits wide With regards to the CAM, there are two possibilities. The first possibility is if the number of infrequent characters is less or equal to the number of frequent characters. In this is true then only  $c2=\log_2(K2)$  character input bits are required to distinguish among all the infrequent characters. Since the *k*-*c*2 most significant bits tell us that we have an frequent character when they are zero, we use the *c*2 least significant bits as character input in the CAM and ignore the result when all *k*-*c*2 most significant bits are 0.

The second possibility is if the number of infrequent characters is greater than the number of frequent characters. In this case, all c2=k bits of the translated character are used for the character input of the CAM.

All of the above can be comprehended more easily with a couple of examples. First, let's consider a case with 63 frequent characters and 7 infrequent ones. The frequent characters are assigned numbers from "0000000" to "0111110" (=62), while the infrequent ones are assigned numbers from "1000000" (=64) to "1000110" (=70). Obviously, the state lookup table needs only the 6 least significant character bits if we make certain to ignore its result when the most significant bit is 0. On the other hand, the CAM requires only the 3 least significant character bits if we ignore its result when the most significant bit is 0, which would indicate a frequent character. The remaining bits, between bit 5 and bit 3, are not required since they are always 0 for infrequent characters.

Now let's consider a different example, where there are 15 frequent characters numbered "000000" to "001110"(=14) and 20 infrequent characters numbered "010000" (=16) to "100011"(=35). We can see that in this case k-c1=2, so if either of the 2 MSBs is 1 the translated character is infrequent. The CAM, on the other hand, requires all 7 bits for the character input since the number of infrequent characters is larger than the frequent ones.

We have shown how translating the infrequent characters can reduce the number of character bits needed by the CAM, especially in cases where only a small number of characters are infrequent. However, the tradeoff is that a larger character translation table, at least one bit wider, is required. Another minor tradeoff is that additional logic (i.e. a (k-c1)-bit OR gate) is necessary check the translated character's MSBs and decide where the next state will come from, the CAM or the state lookup table. In order to take this added complexity into account, we have amended step 2 of the lookup algorithm:

#### Algorithm 3.2: Text scanning procedure for Revision 1 of the Split-AC algorithm

- Step 1. The next input character c is used to address the character translation table, which responds with the corresponding translated character c'.

- **Step 2**. If c' is a "frequent" character, use the state lookup table to find the next state. If c' is an "infrequent" character, the next state is found by checking the "infrequent" character transitions. Otherwise, the next state is 0.

- **Step 3**. Check if the next state is also a "final" state. If it is "final", a pattern was located. Return to Step 1.

#### 3.4.2 Split-AC Revision 2: State reordering.

In our efforts to reduce the state input bits for the CAM, we frequently observed that only a small number of fsm states had infrequent transitions and would

use the CAM at some point or other. This led us to the idea reordering the states so that all states with infrequent transitions are grouped together and eliminating the common state prefix.

This state reordering is done in two stages. First, we reorder the final states. As we mentioned in section 3.2.1, all *F* final states are assigned numbers from 1 to *F*. These states are reordered internally, i.e. in the same *F* positions, but in such a manner that final states *without* infrequent transitions occupy position 1 to *F*-*x*, while final states with infrequent transitions are grouped to numbers F-x+1 to *F*, where *x* is the number of final states with infrequent transitions.

The second stage is the reordering of non-final states with infrequent transitions, which are now assigned numbers from F+1 to F+y, where y is the number of non-final states with infrequent transitions.

The result of the state reordering process is that all states with infrequent transitions are now located between positions F-x+1 and F+y, which share a common prefix of s-s' bits and a varying suffix of s' bits. By ignoring the s-s' common prefix bits between F-x+1 and F+y, we can use the remaining s' bits as a state input for the CAM, where s is the number of bits representing the fsm state.

However, the *s*-*s*' prefix bits are not completely ignored. They may be unnecessary for the CAM input, but they are necessary to control when we want to access the CAM. To assure correctness, the CAM must be accessed only when the *s*-*s*' prefix bits are equal to the common prefix of the states with infrequent transitions. For example, if an input character c is infrequent but the *s*-*s*' prefix bits have a different value from the common state prefix then we are certain that the CAM cannot give us a valid result since we aren't at a state that contains infrequent transitions.

A simple example of how this revision affects the algorithm is the following. We have an fsm with 60 states (s=6 bits) that has a total of 10 states, final and non-final, containing infrequent transitions. After reordering, these states are placed in sequential positions from "001010" (=10) to "010011" (=19). Obviously, the states with infrequent transitions have s-s'=1 bit common prefix and the CAM now requires only s'=5 state bits. In case of an infrequent input character, the CAM will be accessed only if the MSB of the current state is 0.

This algorithm modification reduces the size of the CAM input for "free", without increasing memory size like Revision 1. The only tradeoff is that additional logic (i.e. a (s-s')-bit AND gate with some inputs possibly inverted) is required to check the state prefix and control when the CAM is accessed.

The final version of the lookup algorithm, which takes both revisions into account, is the following:

#### Algorithm 3.3: Text scanning procedure for Revision 2 of the Split-AC algorithm

Step 1. The next input character c is used to address the character translation table, which responds with the corresponding translated character c'.

- **Step 2**. If c' is a "frequent" character, use the state lookup table to find the next state. If c' is an "infrequent" character and the current state contains infrequent transitions, the next state is found by checking the "infrequent" character transitions. Otherwise, the next state is 0.

- **Step 3**. Check if the next state is also a "final" state. If it is "final", a pattern was located. Return to Step 1.

# CHAPTER 4 – RULES, RULE SETS AND RULE SUBSETS

In the first part of this chapter, we describe the rule format that Snort uses, which is also the supported rule format for our application. The second part of the chapter describes the manner in which rules are classified into groups in Snort and in the IDS we implement. Finally, the third part of the chapter describes our motivation for dividing the initial rule sets into smaller subsets, as well as the manner in which that division is performed.

### 4.1 Snort Rules

Rules are used to specify what is considered as suspicious or dangerous traffic. We use the same language as the Snort NIDS [11],[12],[13],[14] for writing rules. A typical rule would something like:

alert tcp 192.168.1.0/24 any -> \$EXTERNAL\_NET 100:200 (content: "foo"; sid:100;)

Each rule is composed of two distinct parts. The first seven parameters, up to the opening parenthesis, form the *rule header*. The purpose of the header is to specify what types of packets require more detailed inspection as well as the action to be taken if the specific rule is activated. The rule header parameters are (from left to right).

- Action: specifies what manner of action will be taken if the rule is activated. The action parameter is almost always "alert", which means an alert message is generated and the packet is logged, but it can also be "log" (logs the packet for processing at a later time), "pass" (ignores the packet), "activate" (generates alert for this packet and turns on another "dynamic") or "dynamic" (remains idle until activated by an "activate" rule and then acts as a "log" rule).

- 2) **Protocol**: This parameter can be either "tcp", "udp", "icmp" or "ip". If the value is "ip" then we are interested in protocols other than TCP, UDP and ICMP.

- 3) **Source IP**: source IP address for the packet. The value for this parameter can be "any", which means that any source IP address is acceptable, a specific IP address (e.g. 192.168.1.20), a subnet address (e.g. 192.168.1.128/25), a list of addresses which is indicated by brackets and uses ';' between the addresses to separate them (e.g. [10.20.30.40;50.60.70.0/24]) or a symbolic address which is specified by a \$ (e.g. \$HOME\_NET). Aside from "any", all the above values can be negated with a '!' at the beginning, which signifies that we want anything except this specific address or subnet (for example !192.168.1.128/25 means all addresses below 192.168.1.128 or above 192.168.1.255).

- 4) Source Port: useful only for TCP and UDP rules (IP and ICMP rules always have "any" in the specific field. Aside from "any", the value can be a specific port (e.g. 80), a port range (e.g. 100:200) or a symbolic port (e.g. \$HTTP\_PORTS). All values except "any" can be negated by use of the '!' symbol (e.g. !100:200 means

ports below 100 or above 200). When indicating port ranges one end of the range can be left blank, in which case the port range translates to "equal or greater" or "equal or lesser" (e.g. :80 means ports less than or equal to 80).

- 5) **Rule Directionality**: a '->' value indicates a straightforward rule in which the parameters to the left of the arrow are the source parameters while those to the right are the destination parameters. The other possible value is '<>' which indicates a bidirectional rule in which the source and destination values are interchangeable.

- 6) **Destination IP**: similar use as the source IP.

- 7) **Destination Port:** similar use as the source port.

The second half of each rule is the *rule options*, which are located inside the parentheses and specify what attributes of the packet are considered suspicious.

Whenever an incoming packet satisfies the criteria of a rule header, the corresponding rule options are checked. If *all* specified options are verified, then the entire rule has been matched and appropriate action must be taken. Rule options offer a large variety of checks that can be performed and are fully described in [14]. However, for the purpose of this work we are interested only in the following options:

- sid: unique rule id number.

- content: specifies a string to be located inside the payload. If the rule contains more than one "content" option then only the first interests us.

- nocase: the string to be matched is case insensitive

- ip\_proto: the protocol number of the packet (for IP rules)

- itype: ICMP type (for ICMP rules only)

### 4.2 Rule Grouping

Checking every single rule against an incoming packet independently is a very expensive process when you have thousands of rules; thousands of header parameter comparisons are required to find which rules can apply to the packet and each rule could trigger a payload scan for a certain pattern. On the other hand, scanning the payload of a packet for *every* pattern in *every* rule may require only one pass of the payload, it also requires significant time to sort through the results and discard the inconsequential (i.e. not applicable to this packet) pattern matches.

In order to strike a balance between the two extremes described above, rules that have the same values for certain header parameters are grouped into *rule sets*. Every incoming packet must now go through a header classifications process in order to discover which rule groups can be applied. Instances of all patterns contained in a rule set are later discovered by performing a single pass (for each activated rule group) of the payload by using a multiple pattern matching algorithm.

We define the following four criteria that a *perfect* rule grouping method and the corresponding packet header classification process must satisfy:

- Distinct: The derived rule sets are formed in such a way that at most one rule set will match every incoming packet

- Complete: The rule group or groups that are selected for an incoming packet contain all the rules that could be matched by this packet.

- Minimal: Rule groups should not contain rules that will be content matched and later discarded due to some other header parameter.

- Fast: Only a very short, fixed period of time is required to select the matching rule set.

Of course, like most things perfect, such a header-based classification of rules into groups has yet to be implemented. Instead, we will show how Snort groups its rules into sets as well as the rule grouping and subsequent packet header classification method used in our IDS implementation.

### 4.2.1 Snort Rule Grouping

The Snort IDS implements a very coarse-grain rule grouping method [12], in which only the protocol and one or two additional parameters are used. This method is implemented with two 64K arrays of sets, called "Source" and "Destination" as well as an additional, "Generic" rule set. Initially all sets are empty.

For TCP and UDP rules, Snort checks the specified source and destination port rule header parameters. If the source port has a unique value x (i.e not "any", negated port or a port range) then the rule is included in rule set "Source[x]". Likewise, if the destination port has a unique value y, the rule is inserted into set "Destination[y]". If neither the source or destination ports are unique, the rule is inserted into the "Generic" set. For ICMP and IP rules the process is simpler, since only one value is of interest: the ICMP type for ICMP rules and the protocol for IP rules. If the rule parameter is a specific number z, then the rule is inserted in "Source[z]", otherwise it is placed in the "Generic" set.

This rule grouping method has the benefit that the rule set matching a packet header can be discovered very fast: if an incoming TCP or UDP packet has source and destination port values 'i' and 'j' accordingly, only "Source[i]" and "Destination[j]" need to be examined. If both are empty, then the payload is scanned using the "Generic" set. If either is non-empty, then it is used to examine the payload. In case that both sets are non-empty then a conflict has appeared and possibly both sets will need to be examined. ICMP and IP packets are processed even faster, since only the "Source" array and the "Generic" set need to be checked. In this way, both the "fast" and the "distinct" criteria are satisfied rather well.

However, this rule grouping method also has significant disadvantages. First of all is the fact that rules with negated values or values inside a range are placed in the "Generic" set, which under conditions leads to inaccuracy. The "Generic" rules may be ignored in cases where they should actually be verified. For example, lets consider rule A with a port value of X and rule B with a port value of !Y, where X and Y are different. Each rule also specifies several other parameters. If a packet arrives with a port value of X, then it will be compared only against A even though it should also activate B. In short, the "complete" criterion is not satisfied very well.

One final disadvantage is that the resulting rule sets may contain a relatively large number of rules, of which plenty may later be discarded. For example, several rules of a set may actually be invalid because they have specified a different IP address than that of the packet. The patterns for these rules are matched during the payload scan, but must then be discarded because they don't satisfy the necessary conditions, causing the software to waste additional effort. This indicates a small degree of compliance with the "minimal" criterion.

#### 4.2.2 Fine-Grained Header Classification

Since we are aiming for a hardware implementation of our system, we plan to take advantage of the available parallel processing capabilities to use a more finegrained rule grouping method. In a nutshell, we use the same parameters as Snort with the addition of the Source and Destination IP addresses.

Specifically, when grouping rules into sets, the following parameters are always used.

- Protocol

- Source IP

- Destination IP

Aside from these three standard parameters, some protocol specific parameters are also used when grouping. For TCP and UDP rules, the source and destination port numbers are also used. ICMP rules use the ICMP type, which is specified by the "itype" *rule option*, while IP rules use the protocol number, which can be specified by the "ip\_proto" *rule option*. When such a rule option is not present, the parameter is considered to have an "any" value.

The rule grouping procedure is very simple: all rules that have exactly the same parameters belong to the same rule set. Since rules usually specify a string to be located inside the payload, every rule set is usually associated with a specific pattern set, and the packet payload must be scanned for any of those patterns using traditional multiple string matching methods. Of course, it is possible to have rule sets in which no rules specify strings to be matched.

At this point we must clarify some exceptions to the rule grouping procedure, as they appear in our implementation. First, when a rule header specifies a list of IP addresses (e.g. [x; y; z]) as source or destination IP then that rule belongs to one set for each address in the list. If a rule header had address lists on both the source and destination IP address, then we take all possible combinations of one source IP and one destination IP and insert the rule to the corresponding rule set. For example, if the header source IP is a list of 3 addresses and the destination IP is a list of 4 addresses, we consider each of the 3\*4=12 IP address combinations as a different rule set. This has been done to simplify the header matching process so that each time we will check for only one IP value.

A second exception is the bi-directional rules. Because we want each rule set to be unidirectional (for implementation simplicity), we consider each bidirectional rule as two unidirectional rules: one with the normal source and destination header parameters and one with the transposed parameters.

One final detail, which is also implemented in Snort, concerns the IP rules. When an IP rule specifies a range of protocols which includes one or more of the other three (i.e. TCP, UDP or ICMP) rule protocols, then this rule is inserted not only to the IP rule sets, but also to rule sets for any other matching protocols. For example, a rule in the form of

```

alert ip $HOME_NET any -> $EXTERNAL_NET any (ip_proto: <8; ...)

```

will also be inserted as a TCP (protocol number=6) and ICMP (protocol number=1) rule with "\$HOME\_NET any -> \$EXTERNAL\_NET any" header parameters.

In summation, the performance of this header classification method according to the four specified criteria is the following:

- Distinct: Poorly satisfied, since all rule sets matching the header of a packet are activated. Our tests have shown that as many as 29 different rule sets can be activated for a single packet.

- Complete: Excellent satisfaction. Because all matching rule sets are activated and checked, no possibly matching rules will be ignored

- Minimal: Satisfied to a large degree. The header classification process doesn't take into account every possible header parameter specified by a rule (e.g. flags, Time To Live). As such, some content matching rules in a set may later be discarded.

- Fast: Excellent satisfaction. Due to the architecture of the header classification component described in section 5.3.1, all groups matching a packet are found in only two cycles.

### 4.3 Dividing Rule Groups into Subsets

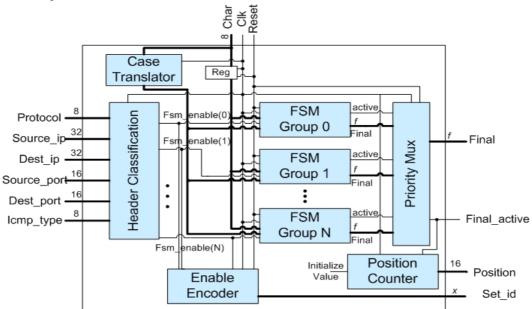

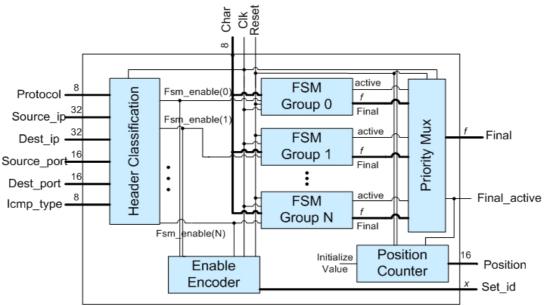

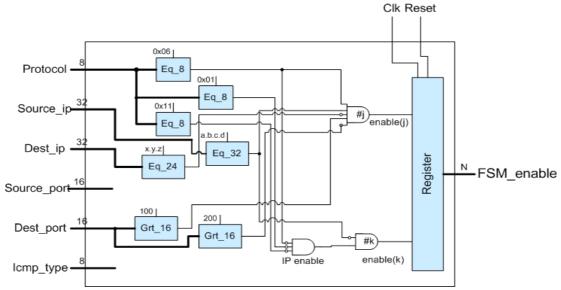

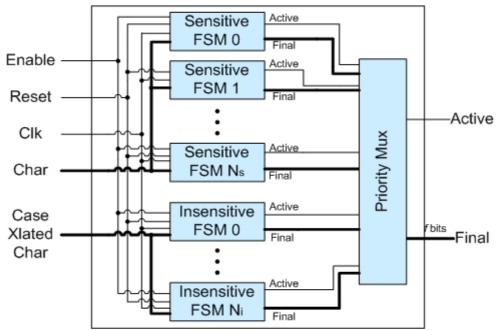

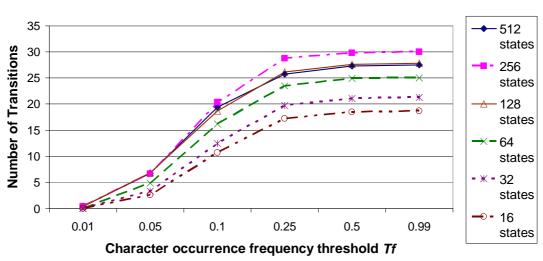

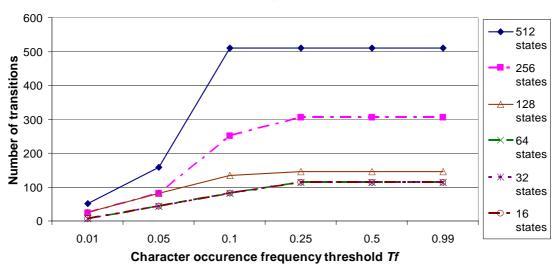

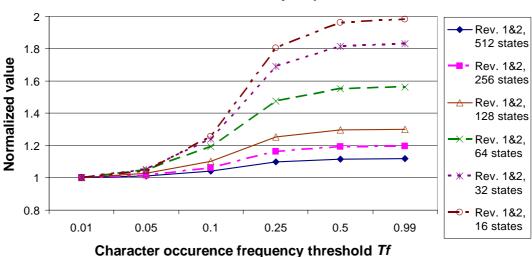

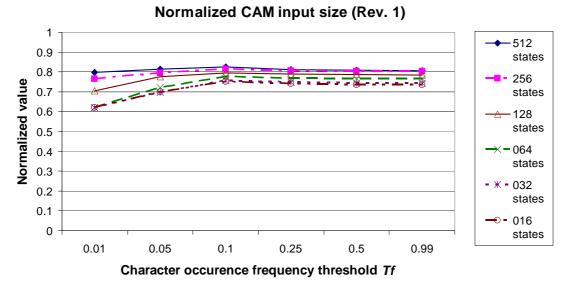

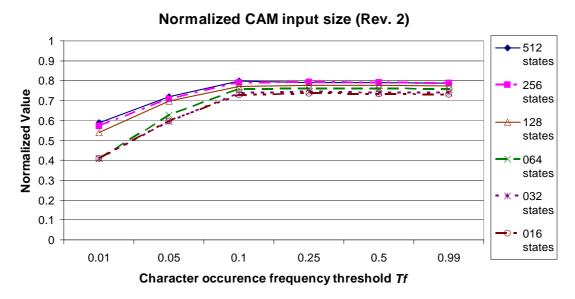

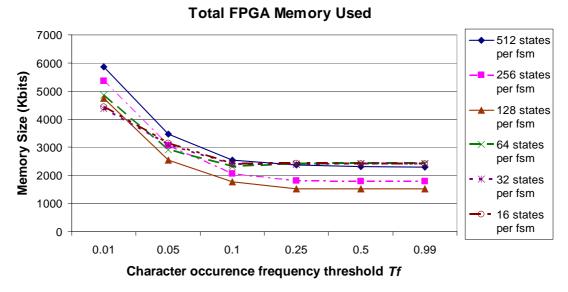

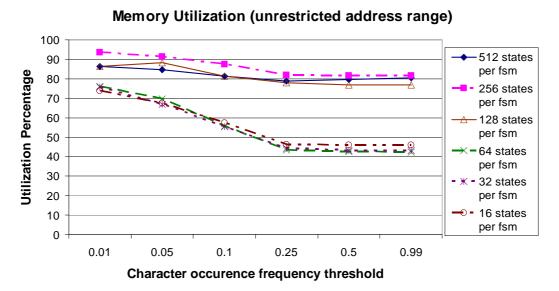

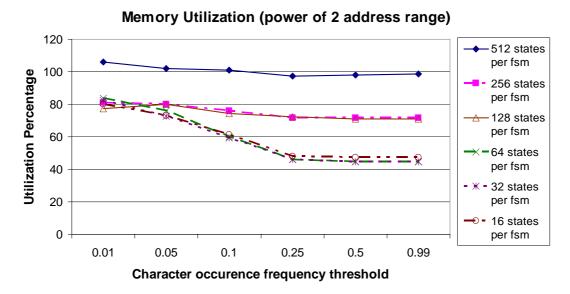

We have focused on the Aho-Corasick algorithm and its derivatives, which would essentially mean that every rule set (and, by extension, every pattern set) has a corresponding finite state machine. However, several pattern sets are large enough to require fsms with a few thousand states, which amounts to very large memory requirements. In addition, fsms with a very large number of states often use a large number of different characters, which means that the Split Aho-Corasick architecture does not offer significant memory gains. A simple way to reduce the size of the required memory is to split large pattern groups into smaller subsets and associate a smaller fsm with each derived subset.